基于FPGA的参数化多路数据对齐器设计∗

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

0 引言

在高速实时信号处理系统中,经常出现多路数字信号的传输。由于信号传输路径不同,造成信号延迟的差异,因此需要将多路数据对齐。高速系列的FPGA都集成了高速串行的I/O收发器,比如Altera器件的GXB模块,宽带信号利用多个通道传输后,在接收端通常通过检测同步字头的方式进行对齐[1];再如多路相关信号,经过不同的传输路径过程后合并处理,也可以通过门限信号进行对齐。多路数据对齐设计通常要考虑收发结构、健壮性、时钟域统一[2]等问题。

另外,随着FPGA的应用越来越多,设计的可移植性成为十分重要的问题[3]。应用综合工具提供的参数化功能,利用硬件语言的参数化设计方法,是解决设计可移植性的有效方法。

针对上述需求,本文介绍一种多路数据对齐器的参数化设计方法。该方法依据数据特征自动检测同步标志信号,不需要收发端的同步控制信息,简化了系统结构,而且可以灵活地适应各种应用;最大限度地减少对齐处理时的数据丢失,设计了异常检测自动复位的异常处理,保证了数据的连续性;另外,也可以解决多路数据跨时钟域的问题。

1 基本原理

多路数据对齐器的设计是以FPGA为基础,采用参数化的硬件描述语言设计,通过延时寄存、同步检测和状态控制等逻辑实现。目前大容量、高速度的FPGA器件通常都内嵌可配置的随机存取存储器(Random Access Memory,RAM),它可以通过指定地址写入或者读取数据。本设计中使用双口RAM作为数据存取单元,进行对齐操作。首先,将多路数据写入RAM。考虑数据输入跨时钟域的情况,对每一路数据分别产生循环的写入地址,同时根据数据特征提取同步标志,并将同步标志所对应的数据地址写入同步地址寄存器。然后,等待全部的多路数据都检测到同步标志,并都将同步地址输入到同步地址寄存器,输出同步输出标志。最后,根据同步输出标志,初始化读地址为同步地址寄存器的同步地址,并设定为循环地址。各路的读地址时钟域相同,且都是通过相同的同步输出标志使能进行初始化,则对应的输入数据为同步标志所对应数据,输出同步标志对齐,进而输出数据对齐,这也解决了各路数据时钟域统一的问题。

当在数据中多次插入同步标志时,前一次已经完成数据对齐,如果两次同步标志之间数据稳定,各路数据长度一致,下一次的数据对齐操作没有数据丢失;如果各路数据长度不一致,则用同步标志对应数据进行补齐,即都能保证数据的连续性。如果由于数据异常导致某一路检测不到同步标志,则不输出同步输出标志,依据上一次的数据对齐结果输出。

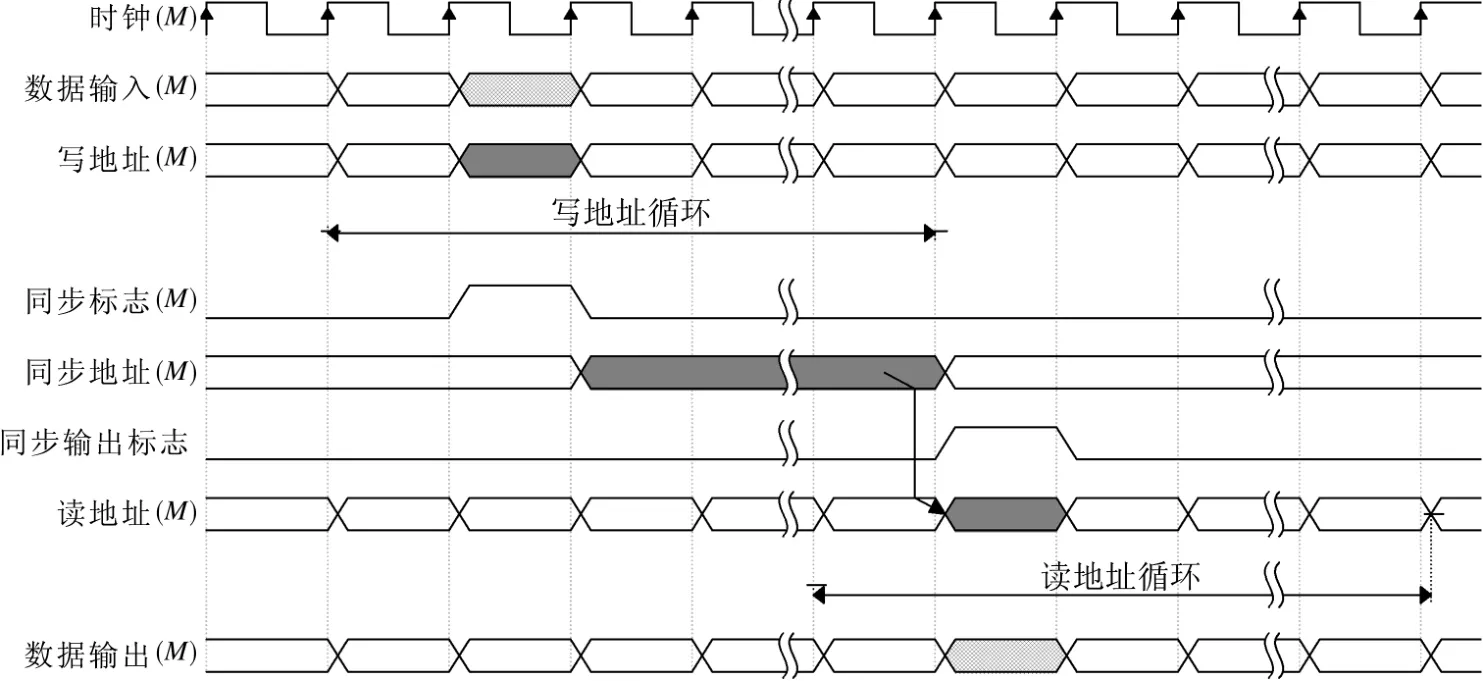

针对多路数据(N路)输入时,第M路数据的RAM读写时序关系如图1所示,其中黑色图框表示该路的同步地址。同步输出标志是各路公用的,当置高时所有路初始化读地址为该路的同步地址寄存器的同步地址。

图1 对齐器RAM读写时序关系

电路结构框图如图2所示,主要逻辑由同步标志提取电路、检测状态控制电路、读写地址产生电路三个部分组成,并使用了一个双口RAM组,一个同步地址寄存器组,深度为数据的通道数量。其中同步标志提取电路是针对不用的应用而专门设计的,其他电路模块为通用的。

2 电路设计

运用硬件描述语言VHDL构建底层电路,将需要变动的参量以参数表示,并传递到设计的顶层文件[4]。含有变化参量的子模块以generic语句加入参数;需多次例化的元件以generate语句实现,例化次数不定时,将例化次数以参数表示。

图2 电路原理框图

本文设计中的变化参量为两类:一是和数据缓存相关的参数,为RAM的数据宽带和存取单元数目,后者通常通过估计多路信号延迟的最大差异来估计;二是和同步标志提取相关的参数,结合具体应用设置。

(1)同步标志提取电路

依据数据特征,输出各路的同步标志。考虑到对齐器的通用性,针对具体的应用设计同步标志提取电路,即只需替换同步标志提取电路就可以适应不同的应用。本文第3节,列举了两种应用,分别设计了同步标志提取电路,第一是使用Altera器件的GXB模块多个通道传输后,在接收端通过检测同步字头的方式进行对齐;第二是多路相关信号经过不同的传输路径后合并处理,通过过门限信号进行对齐。

(2)检测状态控制电路

检测各路的同步标志状态,并输出同步输出标志。使用记录类型(RECORD)定义同步标志的检测状态,如下所示。

┈类型定义┈

type type_synflag_dect is record

synflag_dect:

std_logic_vector(ch_num-1 downto 0);

synflag_dect_all:std_logic;

synflag_dect_rst:std_logic;

end record;

┈例化┈

signal synflag_dect:type_synflag_dect:=((others=>′0′),′0′,′0′);

说明:

a)ch_num:输入参数,通道数量,要求大于1。

b)synflag_dect:逻辑矢量,位宽为通道数量,表示各路同步标志的检测状态。某一路检测到同步标志的时候将其对应位置高,当synflag_dect_rst上升沿复位。

c)synflag_dect_all:逻辑位,当检测到所有通道的同步标志时置高,否则置低。该信号可以作为同步输出标志。由于参数化通道数量,电路实现时可以取NOT synflag_dect进行判断,当逻辑矢量NOT synflag_dect为0时置高,反之置低。

d)synflag_dect_rst:逻辑位,复位synflag_dect信号。设置中间变量计数器synflag_dect_cnt,当synflag_dect非0时计数,为0时复位。当synflag_dect_cnt大于RAM深度或者synflag_dect_all为高时置高,否则置低。前者表示在指定的误差限度内(多路信号延迟的最大差异)没有完成对齐,即同步标志检测出现异常状态;后者表示完成对齐。

以synflag_dect_all信号上升沿作为同步输出标志。上述逻辑都是通过时序逻辑控制。

(3)读写地址产生电路。

考虑数据输入跨时钟域的情况,使用生成语句(generate)对每一路数据分别产生循环的写地址,并将各路同步标志所对应的数据地址写入同步地址寄存器。根据同步输出标志,在同一个时钟域下初始化读地址为同步地址寄存器的同步地址,并设定为循环地址。各路对应RAM在该读地址下的输出为数据输出。

3 应用举例

3.1 GXB接收对齐

在宽带数字信号处理中,对器件的带宽和采样率都有较高的指标要求,在数据传送中多基于高速串行传输技术(SERDES)采用多路光纤传输[5]。

本文配合Stratix IV器件GXB接收器设计对齐器模块。使能8B/10B编码,设置控制码K28.5(0x BC),同时在发送端各路数据添加同步码(0x1CBC)。采用四路传输进行例化和仿真测试。如图3所示为例化的顶层图形化模块、参数列表、端口列表,参数列表虚线框中内容表示和同步标志提取电路相关的参数,ctrl_width表示和GXB核rx_ctrldetect相关参数,channel_numbers表示通道数量,ctr_word表示同步码。当某一路数据检测到rx_ctrldetect为高且数据输入为同步码时,输出同步标志。

如图4所示为该模块仿真波形图。可以看到对齐后的输出,同时显示连续的对齐操作下数据没有丢失。该模块已经使用器件完成了时序仿真、编程下载,以及在线测试。

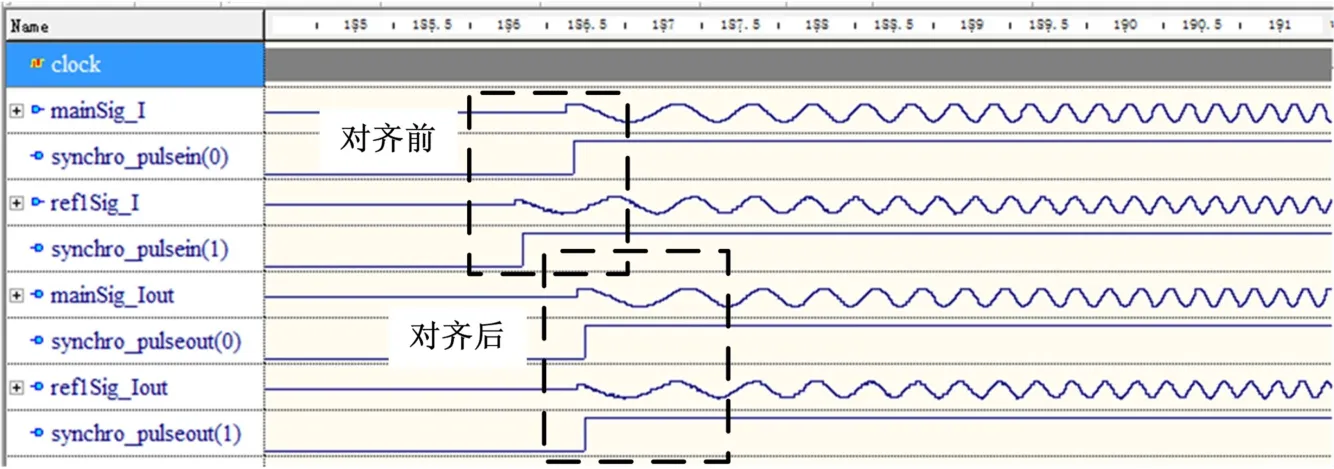

3.2 多路相关脉冲对齐

多路相关的雷达脉冲信号(IQ),经过不同的传输路径过程后合并处理,处理前需要检测过门限信号进行对齐。获取各路输入信号的过门限信号,利用过门限信号上升沿作为同步标志进行对齐。如图5所示,对两路信号进行对齐操作,图5显示对齐前后各路信号的I路信号和过门限信号。

图3 GXB接收对齐器

图4 GXB接收对齐器仿真图

图5 多路相关脉冲对齐

4 结束语

本文设计的多路数据对齐器,使用参数化硬件语言设计,采用结构化设计思想,分离同步提取电路,以适应不同的应用,集成度高、可移植性强,同时兼顾了数据连续性、数据异常、跨时钟域等问题。本设计在工程实践中具有一定的参考和实用价值。

[1]魏书军,刘振安,赵棣新,等.FPGA多通道数据自动对齐的设计与实现[J].核电子学与探测技术,2010,30(3):410-412.

[2]唐辉艳,李绍胜.FPGA设计中跨时钟域同步方法的研究[J].铁路计算机应用,2011,20(5):43-44,47.

[3]孙延腾,吴艳霞,顾国昌.基于VHDL语言的参数化设计方法[J].计算机工程与应用,2010,46(31):68-71.

[4]张鹏南,孙宇,夏洪洋.基于Quartus II的VHDL数字系统设计入门与应用实例[M].北京:电子工业出版社,2012:78-96.

[5]向海生,马利祥,王冰.基于拼接采样技术的宽带数字接收机[J].雷达科学与技术,2014,12(4):450-453.