基于FPGA的GPS同步时钟系统设计

郑恭明,沈媛媛(长江大学电子信息学院,湖北荆州 434023)

基于FPGA的GPS同步时钟系统设计

郑恭明,沈媛媛

(长江大学电子信息学院,湖北荆州434023)

摘要:结合恒温晶振时钟无随机误差和GPS秒信号无累计误差的特点,采用GPS测量监控技术,对高精度晶体振荡器的输出频率进行精密测量和校正后作为系统时钟,通过相位同步算法使FPGA的输出PPS信号与GPS的PPS信号同步。系统中使用Nios II + Verilog HDL设计了高分辨率的时间测量和快速校准时钟同步单元,缩短了频率校准和同步时间。实验结果表明:系统同步精度较高、结构简单,并成功地应用于电磁勘探数据采集系统中。

关键词:GPS;时钟同步;恒温晶振; FPGA

现有的时间同步系统一般采用GPS/北斗秒脉冲信号或恒温晶振的定时信号来进行各系统同步,但存在缺陷:前者在恶劣的施工环境下常会因为各种干扰而发生跳变,同步效果并不理想;后者长时间存在频率漂移,同样无法维持长时间的同步。为解决这些问题,本设计结合GPS有效信号的稳定性,将GPS授时信号用于校准系统的恒温晶振分频秒信号,使之与GPS的秒信号PPS同步,以替代PPS信号。这样不仅克服了GPS授时信号易受外界干扰的缺点,也解决了晶振频率随时间漂移的问题,能获得较为理想的同步信号。为了使本地晶振长时间地同步于GPS系统,就需要不断测量GPS授时信号与本地晶振分频信号的时间间隔,再根据测量数据来校准和同步本地秒信号。本设计较之文献[1-4]所用的方案,系统方案更简洁、集成度更高、算法更易实现、成本更低。

1 系统设计

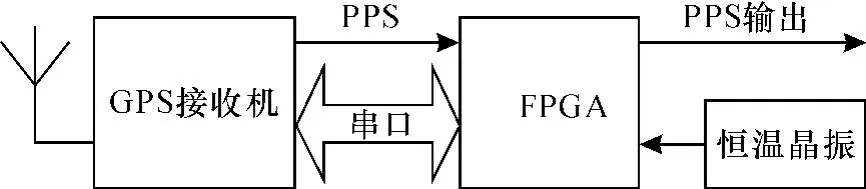

系统方案如图1所示,主要由GPS接收机、恒温晶振和FPGA系统模块3部分组成。GPS接收模块用于输出标准的PPS脉冲信号和国际标准时间( universal coordinated time,UCT),通过串口初始化FPGA系统的时间;恒温晶振作为稳定的系统时钟; FPGA的时序模块对PPS信号进行守时逻辑处理,并输出处理后的PPS信号和同步信号,FPGA的Nios II系统接收GPS的UCT时间,并判断当前输出的PPS信号是否与卫星时间同步。FPGA的时序模块用于测量恒温晶振分频秒信号与PPS信号上升沿的相位差,从而调整恒温晶振分频秒信号的初始相位,使其与PPS信号同步。

2 GPS时钟和恒温晶振频率校准

2. 1 GPS秒脉冲

图1 硬件结构框图Fig. 61Hardware diagram

GPS接收机接收到的GPS秒脉冲或多或少存在一些误差,GPS秒脉冲的误差服从正态分布,与国际标准时间( UCT)相比只存在单个秒脉冲左右的漂移,从一段时间来看,GPS秒脉冲并不存在累计误差。因此首先对单个脉冲的有效性(即是不是伪脉冲)进行鉴别。在大量统计的意义下,计数值的偏差(对应于1个GPS秒脉冲计数时钟芯片的输出)近似服从正态分布,算法中采用的滤波门限值为10,也就是当计数偏差大于10,就认为当前的GPS秒脉冲是伪脉冲,舍弃不要。另外,对于GPS的长期稳定性,计数上也不可能取无限长。由于所选晶振的稳定度很高,本设计选择校准时间为256 s。

2. 2恒温晶振频率校准

高稳晶振在系统的守时过程中具有重要作用,因此,系统对高稳晶振的准确度和稳定性要求十分高,为了保证系统输出的短时标的精度,需要对高稳晶振的频率进行测量、校准[2-3]。

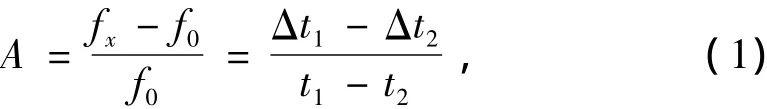

用GPS秒脉冲PPS提供门控时间,长度为T; 以GPS秒时标信号作为计数的开门信号,以高稳晶振分频生成的秒时标信号作为计数的关门信号,在t1、t2两个时刻对开关门信号之间的时差进行测量,分别得到t1和t2。根据频率准确度( A)的公式可得到频率的实测值fx。

测频过程中,应确保计数器引入的测量量化误差比被测频率标准的准确度高1个数量级。由于系统中高稳晶振的校频准确度是10-10,则量化误差引起的频率准确度的偏差为10-11。量化误差的表达式可以表示为

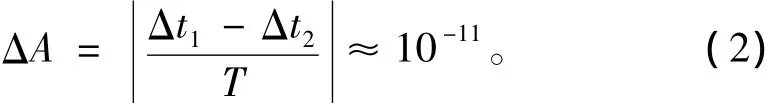

测频过程中,计数器时钟周期t0= 1/f0= 10 ns,因此,t1-t2引起的量化误差为±10 ns。根据式( 2),得到测频所需的门控时间为T = 1 000 s。图2中恒温晶振频率测量模块中取T = 1 024 s。

图2 基于FPGA的高精度时钟同步实现原理Fig. 62Clock synchronization schematics based on FPGA

3 同步时钟的实现

根据上述原理,本系统将授时和校时功能采用同一个环路集成。利用单片FPGA构建锁相环路,将识别后的GPS接收的PPS信号与校正频率后的恒温晶振经分频产生的秒信号进行数字鉴相,得到二者的时间差,然后调整恒温晶振经分频秒信号的初始相位,使其与GPS接收到的PPS信号同步,原理如图2、图3所示。采用计数器1和PPS相位调整器对高精度晶振进行分频,产生晶振秒时钟信号;晶振秒时钟与GPS秒时钟PPS进入鉴相器进行相位比较,计数器2对相位偏差进行计数;将偏差值反馈回PPS相位调整器,调整晶振秒时钟的初始相位,从而构造出一种简便的高精度时钟发生装置。

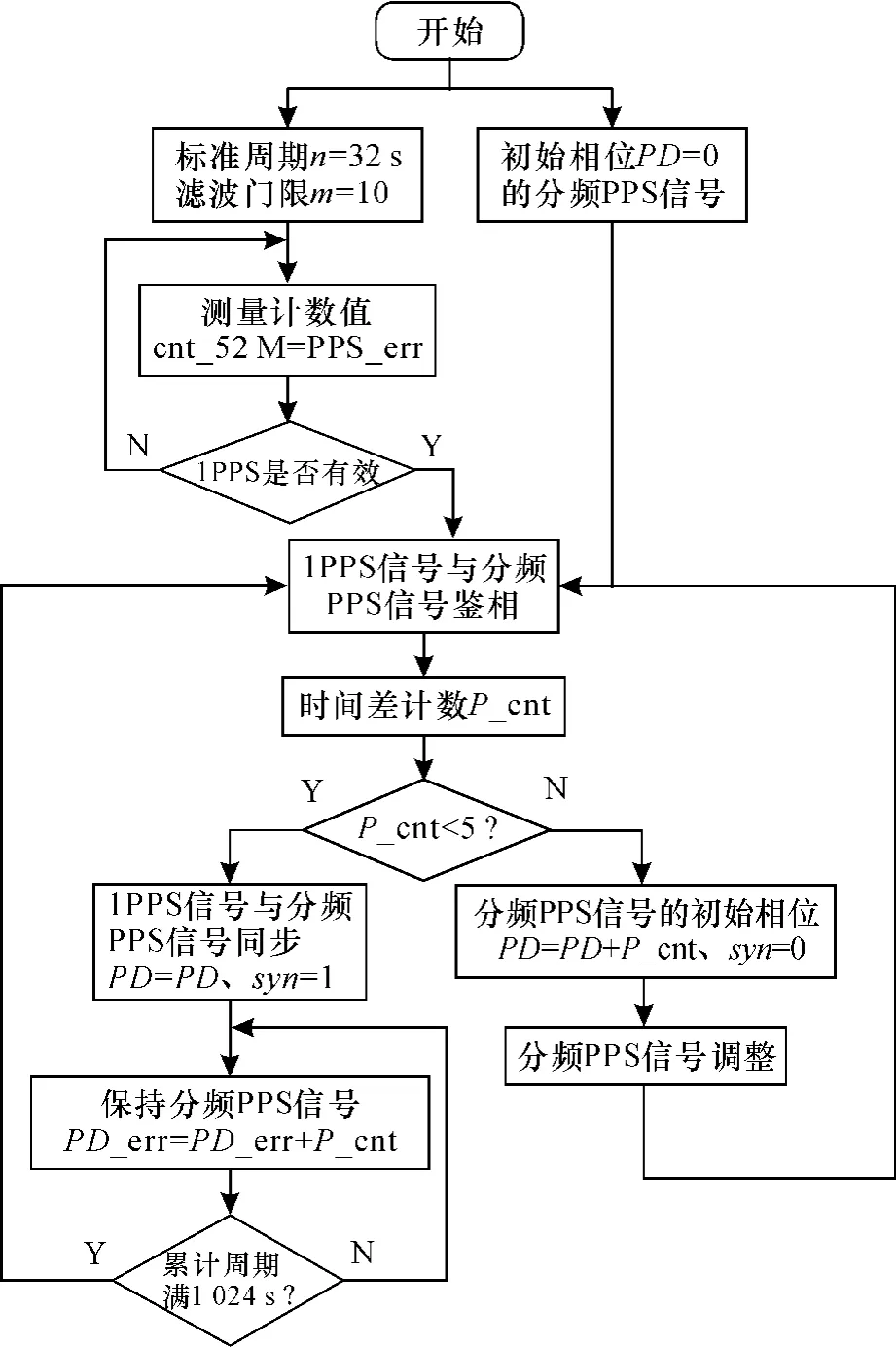

图3 时钟同步流程图Fig. 63Flow chart of clock synchronization

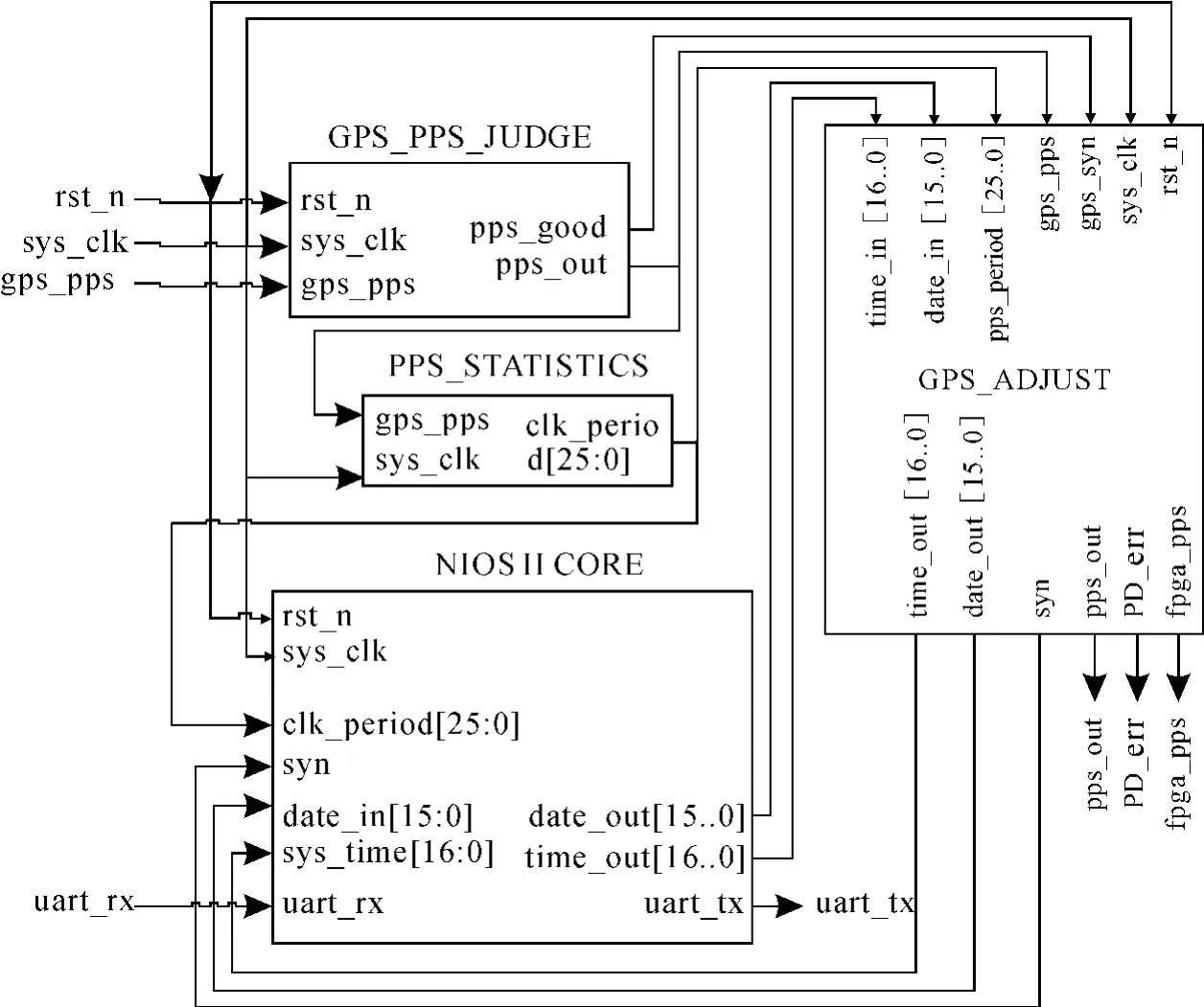

整个系统选择一片Altera公司Cyclone III系列EP3C10E144型号的FPGA作为载体,使用Verilog语言[5]和SOPC技术[6]来实现。系统包括4个模块: Nios II软核、GPS接收的PPS信号的识别模块、恒温晶振频率校正模块和时钟同步模块,系统连接如图4所示。Nios II软核读取GPS接收的UCT时标,并处理GPS的PPS信号与时钟同步模块产生的同步PPS秒信号之间的时间差数据,将结果送给时钟同步模块以调整同步PPS信号的初始相位; PPS信号识别模块剔除伪秒信号,减少干扰;恒温晶振频率校正模块以GPS秒信号时标为基准,对恒温晶振进行1 024 s的频率修正,并将修正值传递给时钟同步模块作为晶振的频率;时钟同步模块是核心,以修正后的晶振频率为基准产生秒信号,并将其与GPS的PPS信号鉴相,调整本机PPS信号的初始相位,使其达到同步的精度P_cnt <5要求为止。

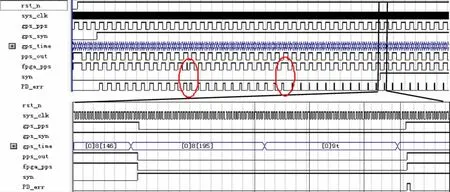

时钟同步模块是系统实现同步的核心,其时序仿真如图5所示。图5上半部分反映了本地FPGA_ PPS信号与GPS_PPS信号的同步过程,椭圆标出了两处FPGA_PPS信号调整的地方,以及调整前后FPGA_PPS信号与GPS_PPS信号时间差的PD_err的变化。图5下半部分是同步时刻的放大显示,信号syn为高时表示时钟同步,同步时的FPGA_PPS信号与GPS_PPS信号时间差PD_err只有一个系统时钟的误差。

图4 时钟同步的FPGA系统Fig. 64FPGA system of clock synchronization

图5 时钟同步仿真时序Fig. 65Clock synchronization timing simulation

GPS接收的PPS信号识别模块、恒温晶振频率校正模块和时钟同步模块全部使用Verilog HDL语言实现,内部时延小、精确度高。其中恒温晶振频率校正模块和时钟同步模块对周期频率和精度均实现了参数化设计,便于仿真和移植。

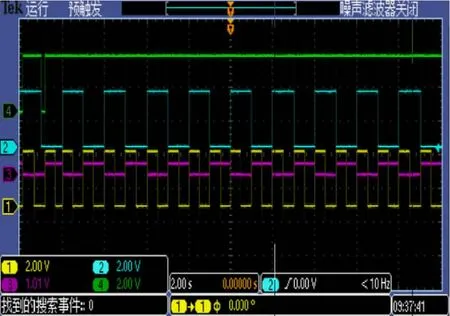

图6为系统测试示波器截图: 1通道为FPGA产生的PPS信号; 2通道为GPS的PPS信号的二分频信号; 3通道为FPGA的PPS信号的二分频信号; 4通道为2、3通道信号的异或信号。图中显示的为从未同步到同步的时刻,即4通道的信号全为高电平。

图6 系统测试同步波形Fig. 66Sync waveform of system test

实验测试显示,系统开机并收到GPS信号在1 024 s内对恒温晶振频率校正后,最长在256 s内实现FPGA的PPS信号与GPS的PPS信号同步,同步后在人为失步情况下FPGA_PPS信号与GPS_ PPS信号的日守时时差t小于25 μs。2个实验系统同步后在人为失步情况下FPGA_PPS信号与GPS_ PPS信号的日守时时差t小于5 μs,满足了短时标设计微秒级的同步精度要求,成功应用于电磁勘探的数据采集同步系统。

4 结束语

本设计是利用本地恒温晶振频率分频秒信号与GPS模块输出的标准秒脉冲信号同步,替代易受干扰的GPS秒脉冲PPS信号。基于Verilog HDL实现了高分辨率的时间间隔测量和PPS相位调整单元,并配合FPGA嵌入式软核处理器Nios II,利用滑动平均法对测量的时间间隔数据进行实时处理,校正恒温晶振分频秒信号,不仅能够准确地测量恒温晶振分频信号与GPS秒脉冲PPS信号之间的时间间隔,而且降低了GPS秒脉冲随机波动对测量结果的干扰,为恒温晶振频率分频秒信号提供可靠的相位修正数据。此外,整个系统完全在一片FPGA中实现,利于提高测量分辨率,减小系统体积,提高系统运行的稳定性。本系统不仅可以用于电磁勘探的数据采集时钟同步,还可以在其他对时钟同步有较高要求的仪器中使用,具有良好的应用前景。

参考文献:

[1]曾祥君,尹项根,林干,等.晶振信号同步GPS信号产生高精度时钟的方法及实现[J].电力系统自动化,2003,27 ( 8) : 49-54.

[2]张国琴,吴玉蓉.基于GPS校准晶振的高精度时钟的设计[J].仪表技术,2010 ( 4) : 23-24.

[3]卢祥弘,陈儒军,何展翔.基于FPGA的恒温晶振频率校准系统的设计[J].电子技术应用,2010( 7) : 101-104.

[4]李泽文,曾祥君,黄智伟,等.基于高精度晶振的GPS秒时钟误差在线修正方法[J].电力系统自动化,2006,30 ( 13) : 55-58.

[5]阿申登.Verilog嵌入式数字系统设计[M].夏宇闻,译.北京:北京航空航天大学出版社,2009.

[6]王晓迪,张景秀.SOPC系统设计与实践[M].北京:北京航空航天大学出版社,2008.

Design of GPS synchronized clock system based on FPGA

ZHENG Gong-ming,SHEN Yuan-yuan

( Electronics&Information School,Yangtze University,Jingzhou 434023,China)

Abstract:GPS-clock,free of cumulative error and the high precision crystal oscillator,free of random error,thus can be effectively combined.By advanced GPS monitoring and controlling technology,the output frequency of the crystal oscillator is measured and adjusted,by synchronizing FPGA_PPS with GPS_PPS by phase synchronization algorithm.A high-resolution fast-measuring unit and clock synchronized unit are designed by Nios II +Verilog HDL to reduce the time of calibration and synchronization.After experimental verification,the high precise telegraphic synchronized system can be successfully applied in data acquisition system of electromagnetic survey.

Key words:GPS; synchronized clock; OCXO; FPGA

作者简介:郑恭明( 1980—),男,硕士,讲师,研究方向:信号处理、嵌入式及EDA技术与应用,zgm831 @ yangtzeu. edu. cn。

基金项目:中国石油科技创新基金项目( 2011D-5006-0302) ;湖北省教育厅科学研究项目( B2013279)

收稿日期:2014-03-11

doi:10. 3969/j.issn. 1674-9057. 2015. 01. 032

文章编号:1674-9057( 2015) 01-0198-04

文献标志码:A

中图分类号:TM764

引文格式:郑恭明,沈媛媛.基于FPGA的GPS同步时钟系统设计[J].桂林理工大学学报,2015,35 ( 1) : 198-201.