低功耗CMOS带隙基准源

哈尔滨理工大学 赵玉迎 厚 娇 常 金 姜久兴 赵 波

低功耗CMOS带隙基准源

哈尔滨理工大学 赵玉迎 厚 娇 常 金 姜久兴 赵 波

本文采用了CSMC 0.18um的标准CMOS工艺,设计了一种工作在亚阈值区的低功耗CMOS带隙基准源,本设计电路是由纯MOS管组成,不包含双极型晶体管,采用工作在线性区的MOS管代替电阻,减少了芯片的面积,工作在亚阈区的MOS管也使得系统的功耗有所降低。室温下,整个电路系统的电流(包含启动电路)为433.08nA,功耗为649.6nW,版图面积为0.0048mm2,工艺流程与标准CMOS工艺有很好的兼容性。

带隙基准;低功耗;亚阈值区

0 引言

便携式电子产品已经成为当今消费者的重要需求,SoC技术的广泛应用已经成为当今发展的重要趋势,低功耗是SoC系统的发展目标[1]。为了降低功耗,应尽可能的减少SoC每一个子电路的功耗,基准源作为这些子电路的重要组成部分,发挥着重要的作用。基准源的设计朝着降低电源电压、降低系统功耗、减小芯片面积、容易集成的方向发展。

本文设计的基准源电路不包含双极型晶体管,是由纯MOS管组成的基准电路,其中利用工作在强反型、线性区的MOS管代替传统电阻,其他MOS管都工作在亚阈值区域[2,3]。这个工作区域,可以使得基准源的功耗在几百纳瓦,采用标准的CMOS工艺技术,工艺易于集成,没有双极型晶体管和大电阻的使用,芯片的面积也可以有效的降低。

1 电路原理

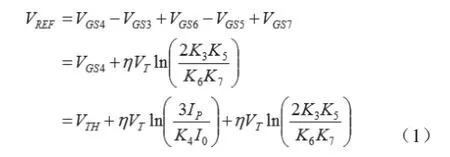

图1为带隙基准源系统的原理图,电路包含电流源子电路、偏置电压子电路、放大器以及启动电路。电流源子电路采用自适应的偏置(自偏置)技术,用一个工作在线性区的MOS管电阻MR1代替传统的电阻R,产生一个电流Ip,偏置电压子电路通过PMOS电流镜镜像电流Ip,并且产生一个基准电压的输出VREF。偏置电压子电路由一个MOS管和两个源极耦合对构成。在偏置电压子电路中M3-M7的栅极和源极两极电压和电流源子电路中的MR1构成了一个闭环的形式。除了MR1所有的MOS管都工作在亚阈值区[4-7]。MOS电阻MR1工作在强反型的三极管区。电路具有两个相反温度系数的电压,把这两种温度系数的电压结合起来,就可以产生一个与温度没有关系的基准输出电压。

图1 基准源电路原理图

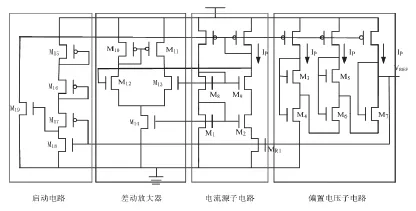

基准输出电压的温度系数可以表示为:

式(3)表明可以通过设置MOS管的宽长比Ki得到零温度系数的输出基准电压,通过温度补偿就可以得到一个与温度没有关系的输出基准电压[8,9]。

2 电路仿真

2.1 直流特性

2.1.1 VREF与T的仿真结果分析

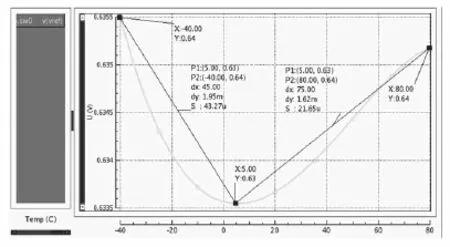

采用DC仿真[10],直流电压为1.5V,得到输出电压VREF随温度的变化关系。

图2 TT工艺角下的VREF与T的关系

图2表明,在温度为-40~80°C范围内,输出基准电压的最大值与最小值之间相差仅为1.95mV,输出基准电压与温度呈弱相关,基本不随温度的改变而改变。

以思维结构与化学实验进程相整和为x轴,以思维品质为y轴,以能力水平为z轴,建立立方体模型,P(P1思维目的——实验选题;P2思维材料——实验设计;P3思维过程——实验操作;P4思维品质——实验观察;P5思维监控——实验处理),T(T1深刻性;T2灵活性;T3独创性;T4批判性;T5敏捷性),L(L1水平 1 实验仪器及操作的识别和描述;L2水平2化学实验事实的加工与处理;L3水平3化学实验原理的理解和运用;L4水平4化学实验方案的设计和评价),并以P1,P2为例进行解读。

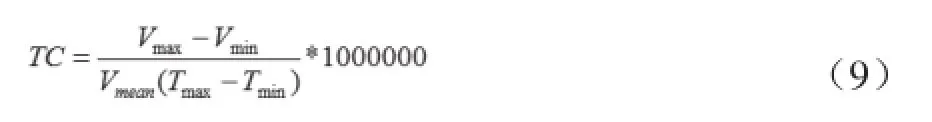

2.1.2 温度系数

温度系数(TC)是衡量带隙基准电路的输出基准电压随着温度变化的一个性能指标,温度系数的表达式如下[11]:

根据式(9)可以计算出温度在-40~80°C范围内,温度系数为25.61ppm/°C,温度系数的值越小,表明基准电压与温度的相关性越弱,温度系数和VREF与T的关系是相互对应的。

2.1.3 VREF与supply power的仿真结果分析

线性度(LS)表征的是输出基准电压偏离输出电压平均值的程度,也可以理解成输出基准电压随着电源电压的改变,线性度的表达式如下[12]:

将电源电压作为设计变量并对其进行扫描,仿真得到VREF随电源电压的关系,并利用公式计算线性度。

图3表明电源电压的范围为0~2.2V,输出基准电压的稳定范围为1.4~2.2V,在这一电压范围内输出仅变化15.09×10-3mV,线性度为18.86ppm/V,输出基准电压不随电源电压变化。

图3 TT工艺角下VREF与电源电压的关系

图4 TT工艺角下I与T的关系

2.1.4 I与T的仿真结果分析

图4表明,电路系统的电流随着温度的增加而增大,在温度变化范围内,电路系统的电流改变量为30.32nA,室温下电路系统(包含启动电路)的电流为433.08nA,电流完全满足设计要求。

2.2 交流特性

电源抑制比(PSRR)是衡量基准源电路对电源线上产生噪声的抑制能力的性能参数[13-17]。采用交流仿真,对基准进行dB(20)输出。

图5 TT工艺角下的PSRR

图5表明在频率为1~100KHz内,电路系统具有较高的抑制噪声的能力,在频率为100Hz时,电源抑制比91.95dB,在PSRR为45dB时,频率为46.98KHz,电路系统能够在较高的频率范围内很好的抑制电源线上的噪声。

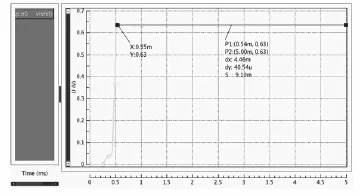

2.3 瞬态特性

2.3.1 启动波形分析

这部分采用瞬态仿真,用启动波形模拟电源上电的情况,启动波形如图5所示。

图6 TT工艺角下启动波形

图6表明,分段信号在0~250μs范围内电源电压为0,600μs上升到1.5V,仿真时间为5ms,分段信号可以较好的模拟电源上电的情况。

2.3.2 电源上电波形分析

图7为电源上电波形,采用瞬态仿真,观察电路系统的启动速度。

图7 TT工艺角下电源上电的输出波形

图7表明,电路系统的启动时间为300μs,由于电路系统的启动时间与电流是一对矛盾,本电路的电流非常小,相对的启动时间要稍长一些,要在两者之间折中。

2.3.3 不同工艺角性能参数对比

本文对电路系统进行TT、SS、FF三种工艺角仿真,对比不同工艺偏差下的仿真结果,表1是不同工艺角下性能参数的比较。

表1 不同工艺角下的典型参数总结

图8 电路系统版图

3 电路系统版图

图8为电路系统的版图,在基准的核心部分为了匹配增加了虚拟晶体管,放大器部分采用二维共质心布局,大尺寸的MOS管采用叉指结构匹配,每个模块都有独立的保护环,电路系统的版图通过了DRC和LVS验证,整体电路的面积为0.0048mm2(93um×52um),完全满足设计要求。

4 电路系统后仿真

4.1 寄生参数的提取

点击Verify-Argus-Run Argus Rce,在RCExplorer界面选择正确的配置文件,如下:

图9 寄生参数配置文件

点击RunRCExplorer,完成后生成rce—extracted文件,用于后仿真。

4.2 电路系统后仿真

电路系统后仿真中主要环节是提取版图中的寄生参数,包括寄生电容和寄生电阻,将提取的寄生参数用于后仿真,后仿真过程与前仿大致相同,最重要的环节就是寄生参数提取,如果这部分出现错误,后仿真是没有意义的。表2给出了电路系统在TT工艺角下前仿与后仿的差别。表2表明,电路系统的前仿和后仿结果近似相同,版图的匹配及布局是做的很成功的。

表2 TT工艺角下的前仿和后仿的结果比较

表3列出了本篇设计与不同带隙基准源的比较。

表3 不同带隙基准源的比较

5 结论

本文采用的是CSMC 0.18 um的标准CMOS工艺技术,仿真结果得到当温度变化范围为-40℃~80℃时,输出基准电压变化1.95mV,在-40℃~80℃的温度范围内温度系数大约为25.61ppm/℃,输入电源电压电压从1.4~2.2V变化时输出电压大约为633.8mV,线性度为18.86ppm/V。在频率为100Hz时电源抑制比为91.95dB,PSRR为45dB时的频率为46.98KHz。电路的总电流(包括启动电路)约为433.08nA,在电源电压为1.5V时,室温下电路的功耗约为649.6nW。基准电压源系统的启动时间约为300μs。整个带隙基准的芯片面积0.004836mm2。本芯片将于2016年2月完成流片。

[1]吴文兰,邢立冬.带隙基准源的现状及其发展趋势[J].微计算机信息,2010,26(6):186~188.

[2]JongMilee.A29nWbandgapreferencecircuit.ISSCC,2015,5: 100~101.

[3]LucaMagnelli,FeliceCrupi,PasqualeCorsonello.A2.6nW0.45Vtemperature-compensatedsubthreshold CMO Svoltagere ference[J].IEEE,2011,46(2):465~467.

[4]魏全,傅兴华,王元发.工作于亚阈区的纯MOS管基准电压源的研究设计[J].贵州大学学报,2012,29(6):72~73.

[5]杨盛波,唐宁覃,贤芳.一种工作在亚阈区超低功耗带隙基准源的设计[J].电子技术应用,2009,2:71~72.

[6]KenUeno.A300nW,15ppm/℃,20ppm/VCMOSVolta geReferenceCircuitConsistingofSubthresholdMOSFETs[J].200 9,44(7):2047~2053.

[7]徐冠南,陈虹,张春等.一种极低功耗的CMOS带隙基准源[J].中国集成电路,2011,2:27~29.

[8]瞿美霞.CMOS带隙基准源的研究与实现[D].合肥:合肥工业大学,2007:1~2.

[9]李帅人.基于40nm工艺的CMOS带隙基准源研究与设计[D],广州:华南理工大学硕士,2012:9~10.

[10]王忆,何年乐.模拟集成电路设计与仿真.科学出版社[M],2008:265~316.

[11]张小莹.低压低功耗CMOS带隙基准电压源设计[D].西安:西安电子科技大学硕士,2009:5~9.

[12]李仲秋.低压CMOS带隙电压源.半导体技术[J].2004, 29(4):61~62.

[13]张涛.低电压高电源抑制比带隙基准电路设计[D].武汉:华中科技大学硕士,2008:13~14.

[14]牟飞燕.低温度系数高电源抑制的基准源设计与应用[D].成都:电子科技大学硕士,2010:15~19.

[15]刘鸿雁,来新泉.一款超低噪声快速启动的CMOS带隙基准电路设计[J].电子工程师,2006,32(2):5~6.

[16]吴金,刘桂芝,张麟.CMOS亚阈型带隙电压基准的分析与设计[J].固体电子学研究与进展,2005,25(3):376~377.

[17]张春华,常昌远.CMOS亚阈偏置恒流源的分析与设计[J].2007,33(1):12~13.

This article uses CSMC 0.18μm standard CMOS process technology, a low power CMOS voltage reference was developed using 0.18μm CMOS process technology, The device consists of MOSFET circuit operated in the subthreshold region and used no resistors, the design of the circuit is composed of pure MOS transistors, does not include the transistors, using a strong-inversion of the MOS transistor instead of resistance, greatly reducing the chip area,working in sub-threshold region MOS transistors also makes the system power consumption is greatly reduced. At room temperature, the current overall circuit (including start-up circuit) is about 433.08nA, the power is 649.6nW, the layout area is 0.0048mm2, process have good compatibility with standard CMOS process.

bandgap reference; low power; subthreshold