基于XVC网络协议的多FPGA远程更新与调试

薛 乾 曾 云 张 杰

基于XVC网络协议的多FPGA远程更新与调试

薛 乾1,2曾 云1张 杰2

1(湖南大学 物理与微电子科学学院 长沙 410082)

2(中国科学院高能物理研究所 核探测与核电子学国家重点实验室 北京 100049)

同步辐射光源硅像素探测器是面向北京先进光源对X射线探测的重大技术需求所研发的新型仪器。该探测器处于辐射环境中,且多个前端电子学读出板被放置在密封的冷却容器中。为在不打开冷却容器的情况下,脱离专用的USB-JTAG (Universal serial bus - joint test action group)下载电缆对现场可编程门阵列(Field programmable gate array, FPGA)进行远端升级,本文提出了一种基于XVC (Xilinx visual cable)协议,通过以太网,利用ARM微控制器控制FPGA的JTAG接口对其进行远程更新与调试的方法。该方案附加电路少,易于拓展,同时也提高了更新可靠性。

硅像素探测器,XVC协议,ARM,JTAG接口,TCP/IP,远程更新与调试

同步辐射光源因其能量连续、准直性好、亮度高等优异性能,成为人类在微观领域认知物质结构、开展功能研究的重要工具和手段[1]。同步辐射装置也成为当前应用最广泛的大型多学科应用平台。为适应同步辐射装置的发展对探测器性能的高要求,并针对北京先进光源的实际需求,中国科学院高能物理研究所设计研发了X射线硅像素阵列探测器。

前端探测器包含6个前端模块,每个模块对应一个传感器以及8个读出ASIC芯片,芯片输出信号通过电平转换送到前端数据处理现场可编程门阵列(Field programmable gate array, FPGA)。FPGA对信号进行缓冲验证,汇总处理后通过光纤传输到后端DAQ (Data acquisition)系统。图1为前端数据处理框图。

图1 前端数据处理框图Fig.1 Flowchart of front-end data processing.

由于整个前端探测器模块放置在密封的冷却容器中,而且整个探测器处在辐射环境中,方便可靠的FPGA远程更新与调试方案成为电子学系统设计的重要方面。显然传统的基于USB-JTAG (Universal serial bus - joint test action group)更新FPGA的方式已不再适用。

目前国内外出现的FPGA远程更新的方案基本分为两大类[2]:一类是针对早期的内部没有专用远程升级电路的FPGA器件,采用单片机CPLD (Complex Programmable Logic Device)、DSP (Digital Signal Processor)、ARM (Acorn RISC Machine)等作为辅助配置器件[3],配合外部Flash和以太网芯片来实现,这些方案灵活性高但设计复杂且提高了成本;另一类是针对最新推出的FPGA器件,其自带了远程升级内核或逻辑块,只要结合外部数据配置通道,即可实现远程更新,该方案附加电路少,节省硬件资源,但却占用了FPGA的内部逻辑资源,而且只适用特定型号的FPGA。另外,上述两类方案均无法实现对FPGA的远程调试,还需要在PC端开发用于远程更新的TCP/IP软件,增加了设计复杂度。

考虑到基于JTAG的下载方式在FPGA配置、Flash PROM配置、软/硬件调试以及硬件测试方面的重要用途,本文设计了一种基于XVC (Xilinx visual cable)协议,通过以太网,使用单芯片ARM微控制器控制FPGA的JTAG接口进行远程更新调试的方案。该方案操作简单,无需额外开发TCP/IP软件,基于网络的通信能够保证足够远距离的灵活的可靠数据传输。还能对FPGA进行远程ChipScope调试。同时,通过简单的JTAG链路连接,可以同时完成多片FPGA的升级与调试[4]。

1 硬件系统实现

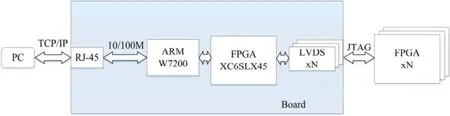

在本设计中,ARM微控制器通过模拟JTAG接口的时序对FPGA进行配置。针对多片FPGA进行远程更新的系统框图如图2。

图2 系统模块框图Fig.2 Block diagram of system structure.

系统硬件电路主要由ARM微控制器、JTAG链路模块、LVDS (Low-voltage differential signaling)模块组成。ARM选择Wiznet公司的W7200开发板作为配置控制器,一端通过网络与PC建立连接,另一端通过外设的GPIO (General purpose input output)传输JTAG配置时序。LVDS模块负责将JTAG单端信号转换为低压差分对信号,一对一发送给待更新的FPGA。多片待更新FPGA的JTAG链通过另外一块FPGA开发板上的主控FPGA芯片XC6SLX45的内部逻辑来实现,板上用9个接插件引出FPGA的9组I/O,分别连接W7200和8个LVDS模块。其中, LVDS模块和主控FPGA开发板以子母板的形式连接。

远程更新时,PC端使用iMPACT将包含配置文件的指令通过网络发送给W7200,W7200根据XVC协议接收指令并模拟产生JTAG时序,主控FPGA接收该时序并通过JTAG链路送入待配置FPGA,完成最终配置。

W7200是Wiznet公司推出的一款单芯片集成了硬件TCP/IP协议栈的ARM Cortex-M3微处理器[5]。内有20 KB的SRAM和128 KB的Flash以及32 KB的以太网RX/TX缓存,具有最高72 MHz的工作频率,有足够的能力进行数据处理。硬件TCP/IP协议支持 TCP、UDP、IPv4、ICMP、ARP、IGMP、PPPoE和以太网,这些协议在各种应用领域已经得到多年的验证。其结构如图3所示。

图3 W7200结构框图Fig.3 Schematic diagram of W7200 processor.

W7200的内核采用32位的STM32F103CB,通过SPI与W5200连接,外部拓展40个引脚,负责提供该系统的GPIO、I2C、SPI、USB以及USART接口,集成度高却具有很低的功耗。W5200为该公司推出的全硬件TCP/IP芯片,负责为该系统提供各类硬件TCP/IP协议、MAC以及PHY,支持8个独立的socket同时工作。使用该芯片的优势是通过简单的socket编程,用户便可以轻松实现所需的以太网通信,而不必要处理复杂TCP/IP协议栈控制。

2 软件设计

2.1 JTAG工作方式

JTAG是符合IEEE 1149.1标准的国际标准测试协议[6],主要用于各类芯片的内部测试和配置。现在大多数高级器件(包括FPGA、MCU、DSP以及CPU等)都支持JTAG协议。标准的JTAG接口是4线接口:模式选择(TMS)、时钟(TCK)、数据输入(TDI)以及数据输出(TDO)信号线。

JTAG工作原理是在器件内部定义一个TAP (Test Access Port)测试访问端口,外部控制器通过TAP可以访问芯片提供的所有数据寄存器和指令寄存器。使用JTAG方式配置FPGA时,通过TCK和TMS的值,选定一个需要访问的数据/指令寄存器,将其连接到TDI和TDO之间。然后由TCK驱动,通过TDI,把需要的数据/指令输入到选定的数据/指令寄存器中,同时把对应的寄存器中的值通过TDO读出来。JTAG接口在线编程和调试的特征改变了传统生产流程,配置效率高,是项目研发阶段必不可少的配置模式。

2.2 XVC协议

XVC协议是Xilinx公司推出的一款基于TCP/IP的虚拟线缆协议[7],它可发挥类似于 JTAG线缆的作用,允许用户无需使用USB线缆而是通过网络访问Xilinx FPGA的JTAG接口并对其进行高效率的远程更新与调试。该协议还具有扩展性,可进行安全连接,允许用户通过编程将其实现于不同的平台。

XVC协议内容简单,使用方便,其基本内容可总结为如下三条指令:

1) getinfo:

该指令用于获取XVC服务的版本。当接收到“getinfo:”指令时,该服务将会返回如下的字符串:“xvcServer_v1.0;<xvc_vector_len> ”,其中,<xvc_vector_len>代表了该协议一次能移位发送的字节向量的最大长度。

2) shift:[num bits][tms vector][tdi vector]

该指令表示分别以字节向量TMS vector和TDI vector的形式发送num_bits个二进制数据。其中,num_bits是一个小端格式的整数,TMS vector和 TDI vector代表所要发送的TMS和TDI的二进制数据。发送过程中,0字节的0比特位首先被发送出去,字节向量的长度会根据num_bits的值向上补齐成最接近的字节数。该指令最终应该返回与TMS vector向量同样长度的字节向量TDO vector,代表从JTAG接口返回的所有的TDO。同样也是0字节的0比特位首先被接收回来。

3) settck:[period in ns]

该指令表示将该协议通信的时钟周期设置为period 纳秒。period同样是一个小端格式的整数值。使用该指令最终应该返回实际的周期值。

iMPACT和ChipScope通过网络访问FPGA的JTAG接口的基本原理就是基于XVC协议发送shift指令,实现JTAG-Client的功能[8]。因此只要ARM微控制器根据shift指令格式分析数据,便能成功模拟JTAG时序,实现类似于JTAG-Server的功能。JTAG-Server与JTAG-Client的结构如图4。

图4 JTAG服务器与客户端Fig.4 JTAG-Server and JTAG-Client.

2.3 FPGA软件设计

在本设计中,主控FPGA负责实现8片待更新FPGA的JTAG链路。一组I/O口用于接收W7200的配置时序,另外8组I/O口分别连接8个LVDS模块的输入。一个4位的拨码开关用来控制接入JTAG链的FPGA的个数。

2.4 ARM软件设计

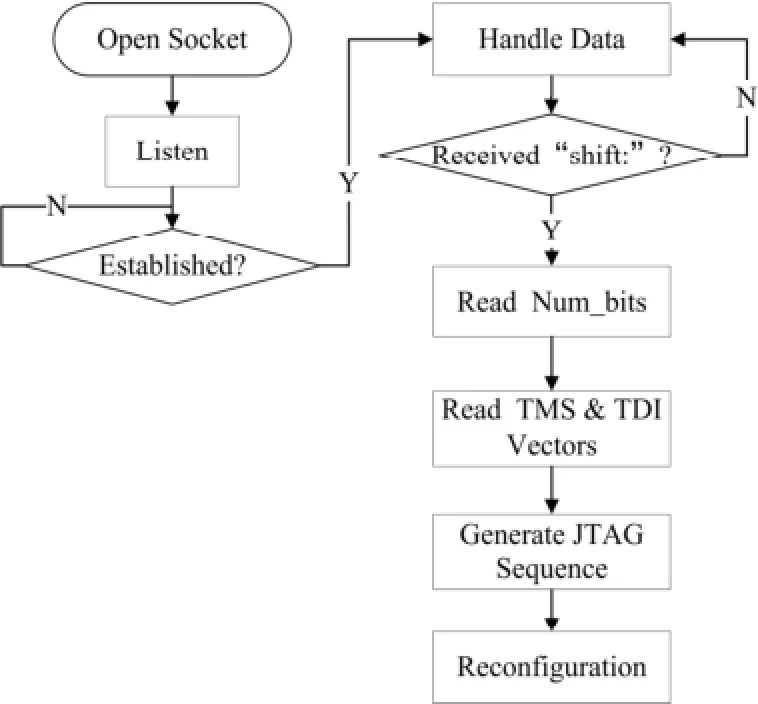

本方案使用基于JTAG的配置方式,W7200作为配置控制器,其通用I/O引脚PB12、PB13、PB14、PB15分别作为JTAG接口的TMS、TCK、TDO和TDI。W7200的工作流程如图5所示。其应用程序用C语言开发生成,Keil MDK进行编译调试。主要包括W7200初始化和指令处理两部分。

首先,W720初始化的内容包括:设置系统工作时钟、中断、GPIO/SPI、接收与发送缓存大小以及网络设置。由于iMPACT软件每次发送shift指令的最大长度为2256 byte,故设置接收缓存区RX_BUF大小为2256,而发送缓存区TX_BUF大小为1178。网络设置包括选择打开socket0进行网络通信,并设置其通信协议为TCP,端口号为5000,并为其分配IP地址和MAC地址。初始化完成后,W7200会作为TCP server打开socket0监听网络上的连接请求。

图5 更新流程Fig.5 Update process.

W7200处理指令的过程为:从 socket0的接收数据缓冲区接收6个字节,若与字符串shift:对比相同,则继续读取4字节的内容作为num_bits,通过计算将其转换为字节数nr_bytes。接着按该字节数分别读取TMS vector和 TDI vector到接收缓存区RX_BUF,然后通过for循环分别将TMS vector和TDI vector的每一位赋值给TMS和TDI引脚,同时产生周期性的TCK信号。该for循环同时将TDO引脚上检测到的输入信号写入发送缓冲区TX_BUF,循环结束后以TDO vector发送给PC。PC验证收到的TDO数据无误,继续通过shift指令发送下一个数据包。由此便实现了一个完整的JTAG数据链路,从而实现了通过网络将配置数据经由JTAG接口配置给FPGA的过程。

3 远程更新

利用iMPACT进行远程更新时的软件设置如图6所示。首先打开iMPACT软件,在边界扫描模式下选择菜单栏的output、Cable Setup,选择打开Xilinx_XVC插件,更改连接对象的IP地址与端口号,发送连接请求给W7200。

待成功建立socket连接后,初始化JTAG链,选择待配置FPGA和配置文件并双击Program,PC端便按照shift指令的格式发送配置指令和数据给W7200。配置结果如图7所示。经过验证,为一片FPGA成功配置大小为630KB的.bit文件所需时间为21 s,配置1.41MB的.bit文件所需时间为48 s,配置速率均为240KB·s−1。在相同环境下,配置不同大小的文件速率基本一致。该方案使电子学系统的远程更新和调试变得简单灵活。

图6 iMPACT下载线设置Fig.6 iMPACT cable setup.

图7 成功更新FPGAFig.7 Successfully update FPGA.

4 结语

本方案中,基于Xilinx 的XVC协议,利用PC机与ARM通过以太网通信,成功实现了基于JTAG接口的FPGA的远程更新与调试。该方案实际只需要一个ARM单芯片,无需其它额外的附加电路。在其他系统中应用时,可直接将W7200芯片固化在电路板上,方便可靠。随着互联网的发展推进,通过网络进行硬件程序的更新将变得更加普遍。

1 李默, 江晓山, 胡俊, 等. 用于同步辐射硅像素探测器的高速数据传输模块研究[J]. 核电子学与探测技术, 2014, 34(4): 474-476. DOI: 10.3969/j.issn.0258-0934. 2014.04.013

LI Mo, JIANG Xiaoshan, HU Jun, et al. The design of high-speed data transmission module for the silicon pixel detector research[J]. Nuclear Electronics & Detection Technology, 2014, 34(4): 474-476. DOI: 10.3969/j.issn. 0258-0934.2014.04.013

2 文华武. 基于以太网的FPGA远程程序升级系统的设计与研究[D]. 重庆: 重庆大学, 2012

WEN Huawu. The design and application of Ethernet based FPGA remote system update[D]. Chongqing: Chongqing University, 2012

3 王利军, 张超. 基于CPU实现FPGA远程更新[J]. 信息通信, 2013, 20(6): 44-45. DOI: 10.3969/j.issn. 1673-1131.2013.06.028

WANG Lijun, ZHANG Chao. Remote FPGA update based on CPU[J]. Information & Communications, 2013, 20(6): 44-45. DOI: 10.3969/j.issn.1673-1131.2013.06. 028

4 薛俊东, 梁昊, 陈一新, 等. μ子鉴别器电子学读出系统FPGA配置方法[J]. 核技术, 2008, 31(10): 786-790. DOI: 10.3321/j.issn:0253-3219.2008.10.014

XUE Jundong, LIANG Hao, CHEN Yixin, et al. FPGA configuration of readout system for muon counter of BESIII[J]. Nuclear Techniques, 2008, 31(10): 786-790. DOI: 10.3321/j.issn: 0253-3219.2008.10.014

5 Internet embedded MCU W7200 datasheet[OL]. http://www.wiznet.co.kr, 2015

6 徐文波, 田耘. Xilinx FPGA 开发实用教程[M]. 第二版.北京: 清华大学出版社, 2012: 80-82

XU Wenbo, TIAN Yun. Xilinx FPGA: development and application[M]. 2ndEd. Beijing: Tsinghua University Press, 2012: 80-82

7 Xilinx visual cable overview[OL]. http://www.xilinx.com/ products/intellectual-property/xvc.html, 2015

8 Kämmerling P, Akens A, Loevenich H, et al. FPGA configuration by TCP/IP and Ethernet[C]. Real-Time Conference, 15thIEEE-NPSS, 2007: 1-4

Remote updating and debugging multi-FPGA based on XVC internet protocol

XUE Qian1,2ZENG Yun1ZHANG Jie2

1(School of Physics and Electronics, Hunan University, Changsha 410082, China)

2(State Key Laboratory of Particle Detection and Electronics, Institute of High Energy Physics, Chinese Academy of Sciences, Beijing 100049, China)

Background:Silicon pixel detector for synchrotron radiation is a new device designed for the technical need of X-ray detection of Beijing advanced light source. The entire detector is placed in a radiation environment, and the multiple frontend readout boards are placed in sealed cooling containers, thus the traditional Universal serial bus -joint test action group (USB-JTAG) cables can no longer be used.Purpose:This study aims to design and implement remote updating and debugging multi-Field programmable gate array (multi-FPGA) for the detector without opening the cooling container.Methods:In this study, a network based ARM microcontroller was used to accept configuration files via network and generate JTAG sequence to FPGA by means of Xilinx visual cable (XVC) protocol.Results:The remote updating and debugging of multi-FPGA were realized.Conclusion:This method improves the reliability of remote updating and debugging of FPGAs and is easy to extend with less extra circuits.

Silicon pixel detector, XVC protocol, ARM, JTAG interface, TCP/IP, Remote update and debugging

XUE Qian, female, born in1992, graduated from Hunan University in 2013, master student of Hunan University now, engaged in the FPGA hardware design

ZHANG Jie, E-mail: zhj@ihep.ac.cn

TN919

10.11889/j.0253-3219.2015.hjs.38.120402

核探测与核电子学国家重点实验室2015年自主研究课题及开放课题资助

薛乾,女,1992年出生,2013年毕业于湖南大学,现为湖南大学硕士研究生,从事FPGA硬件设计

张杰,E-mail: zhj@ihep.ac.cn

Supported by the Independent Study and Open Issue of State Key Laboratory of Particle Detection and Electronics in 2015

2015-08-27,

2015-10-20

CLCTN919