基于通用硬件的数字脉冲压缩工程实现研究

杨守峰,秦庆兵,余 开

(安徽博微长安电子有限公司数字技术部,安徽六安 237010)

在脉冲体制雷达中,为解决距离分辨率和平均功率的矛盾,通常采用脉冲压缩技术。脉冲压缩技术的实现多基于定制硬件,而近年来,随着雷达技术的快速发展,其工程实现正逐渐由定制硬件向通用硬件发展。基于通用硬件实现各种雷达信号处理算法的方法有着算法实现灵活、通用性强等特点,故现已涌现出较多种。本文介绍了脉冲压缩的基本原理,并给出了一种基于通用硬件的工程实现方法。

1 脉冲压缩的原理

1.1 LFM 信号

线性调频信号是搜索和跟踪雷达中最常用的脉压波形[1]。线性调频矩形脉冲信号的表达式为

其中,T为脉冲宽度;K=B/T为频率变化率;B为频率变化范围,即信号的带宽;f为载波频率;rect()为矩

0形函数;u(t)为信号包络

信号的瞬时频率可写成

令f0=0,得到零中频信号,其实部、虚部就构成了实际中的两路正交信号。

1.2 频域FFT数字脉压原理

脉冲压缩理论上是基于匹配滤波的概念[2],其处理实质就是白噪声干扰假设下的一种匹配滤波。其实现主要有两种方式:时域卷积数字脉压和频域FFT数字脉压。本文基于通用硬件的工程实现所用方法为频域FFT方法。基于频域的数字脉压原理是用DFT将离散输入时间序列变换成数字谱,然后乘以匹配滤波器的数字频率响应函数,再用IDFT还原成时间离散但已压缩的输出序列。用FFT方法实现数字脉冲压缩的运算原理,如图1所示[3]。

图1 FFT脉压原理图

其中,si1[n]、siQ[n]是接收信号数字 I、Q 序列;h[n]为匹配滤波器序列。

为实时处理的需要,通常采用FFT算法,式(4)可写为

基于时域卷积的脉压方法和频域FFT脉压方法在本质上是等价的,是同一原理在时域和频域中的不同表现形式。

2 工程实现

2.1 通用硬件构成及资源

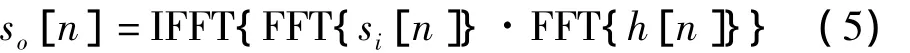

(1)硬件原理图如图2所示[4]。

(2)主要资源。主要硬件资源包括8片ADSP TS201,2 片 FPGA(EP2SGX60 和 EP2SGX30),2 片SRAM和4片256 MB的SDRAM等。

主要通信资源包括DSP与DSP之间和DSP与FPGA之间的链路口通信、DSP与EP2S30之间的总线通信,通用硬件与外部之间的光口、与背板之间连接的高速通道和CPCI总线,两块FPGA之间的LVDS及32 bit双向互连总线等。

图2 硬件原理图

2.2 软件构架及流程

(1)任务安排及数据流程图。图3所示的数据流程充分利用了通用硬件算法实现灵活的特点。首先,通过数据轮流分发机制可实现DSP可用运算时间的扩展。其次,充分利用了通用硬件DSP之间链路口灵活通信关系,实现了3个波束数据的高效融合。

以工程应用中脉冲重复周期长度为440μs、带宽10 MHz、采样率10 MHz为例,重复周期长度为440μs,采样率10 MHz决定了需要做8 192点的FFT以实现频域脉冲压缩功能。根据频域脉冲压缩的基本原理可知,其总复乘次数约为N log N-,即 75 776次复2数乘法。在TS201核时钟频率480 MHz的情况下,脉冲压缩所需时间约为630μs,其时间 >440μs,<880μs。因此,需设计成数据轮流机制。其次,工程任务中需要波束间的数据融合等功能。故在工程数据流程设计中,将三波束数据进行汇集到DSP3综合处理。

图3 数据流程图

1)FPGA的工作任务。接收雷达工作状态信息及脉压前的IQ数据[5];根据状态信息产生FPGA本身及DSP工作的时序及中断控制信息;根据状态信息设置链路口参数,并转换相应的数据分发机制;按照约定的协议通过链路口将数据分发至两簇的DSP0-2;从两簇的DSP3分别接收脉压后的数据并打包传送给下一级处理[6-7]。

2)DSP的工作任务。根据接收的雷达工作参数进行相对应的设置,如链路口参数及处理方式参数;将接收到的数据进行定浮点转化;对每个波束的数据进行脉冲压缩处理;DSP0~2的脉压数据传送至DSP3;脉压结果数据的定点化;三波束数据融合;波束之间数据的集中处理及按协议打包通过链路口传送给FPGA。

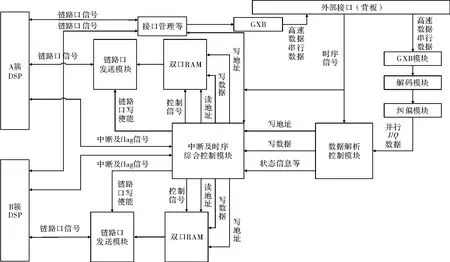

(2)FPGA程序设计方法。针对FPGA的主要工作任务,其设计原理框图如图4所示。

图4 FPGA原理框图

FPGA设计主要包括GXB高速数据解析、串并转换和数据纠偏,中断及时序综合控制实现数据轮流转换分发,最后通过双口RAM转换时钟域并按链路通信方式通过链路口发送模块传输数据到3块 DSP。FPGA实现中的核心模块为中断及时序综合控制模块。该模块根据各种任务状态实现数据的分发机制,避免了数据的读写冲突;同时,能根据任务状态信息,实现DSP时序控制,保证DSP按照两路通信协议无误地传输数据。

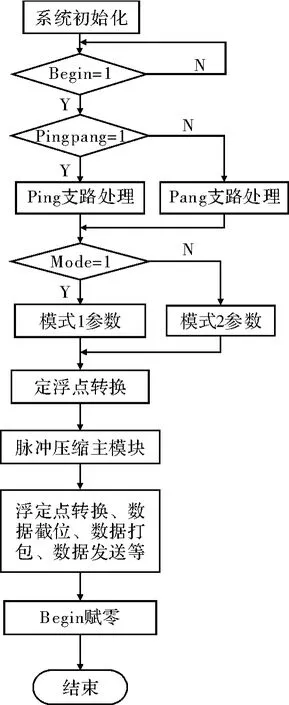

(3)DSP软件流程。DSP软件流程及频域脉冲压缩软件模块流程,如图5和图6所示。

图5 DSP主程序流程

图6 频域脉冲压缩流程图

DSP的主流程主要根据时序的安排、系统初始化、开始的判断、乒乓支路的选择、工作模式等的判断、定浮点的转换、脉冲压缩、数据定浮点转换和数据打包等流程。其中,工作模式的判断主要是为了对相应的工作参数进行判断,从而选择对应的脉冲压缩系数、存储地址等参数。

为节省运算量,缩短运算时间,工程中采用频域脉冲压缩。根据频域FFT脉冲压缩的基本原理,DSP主流程中的脉冲压缩模块包括FFT、复数相乘和IFFT3部分。

3 工程应用效果

3.1 仿真结果

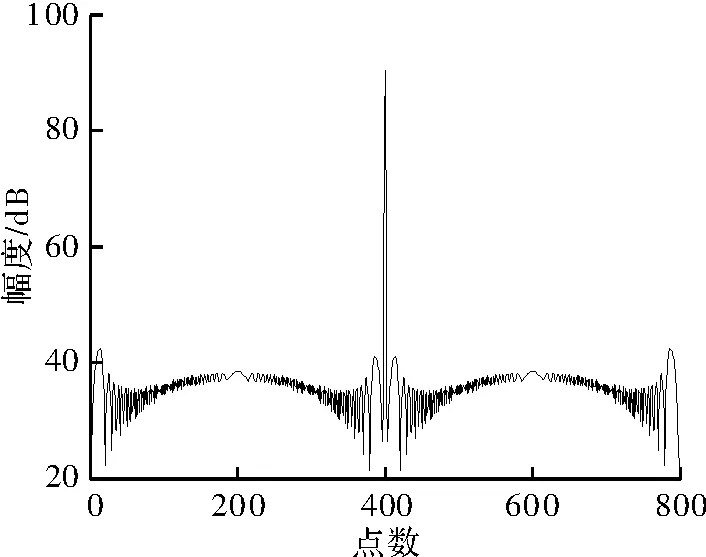

根据任务的技术要求,仿真参数为信号带宽10 Mbit·s-1,采样率 10 MHz,脉冲时宽为 40 μs,FFT点数为8 192点,加海明窗。脉冲压缩Matlab仿真结果,如图7所示。

图7 某工程脉压仿真结果

3.2 DSP 运算结果

工程应用中脉冲重复周期长度为440μs,做8 192点的FFT实现频域脉冲压缩功能。运用上述软件构架及流程,通过自检测试数据得到基于通用硬件的工程脉冲压缩结果,如图8所示。

图8 某工程DSP运算结果

工程实现中,经试验得出,在TS201核时钟频率480 MHz的情况下,脉冲压缩所需时间约为700μs,是脉冲重复周期的1.6倍,运算时间余量为0.4倍的脉冲重复周期。仿真结果表明,本文所述实现方法的任务安排合理,通用硬件资源利用充分。另外,通过对比图7和图8可得出,本文所述基于通用硬件脉冲压缩的实现结果与Matlab理论仿真结果一致,完成了既定的脉冲压缩功能。因此,上述基于通用硬件的数字脉冲压缩工程实现方案合理可行。

4 结束语

介绍了基于通用硬件频域数字脉冲压缩的基本原理及工程实现方法。而针对工程实现方法又具体介绍了FPGA和DSP主要工作任务、功能及DSP主程序的软件流程。该方法已在某型雷达上成功应用,验证了该设计方法的有效性和可行性。

[1]徐玉芬.现代雷达信号处理的数字脉冲压缩方法[J].现代雷达,2007,29(7):61 -64.

[2]范伟时,孙合敏.非线性调频脉压系统工程实现研究[J].雷达与对抗,2001(1):35-39.

[3]马晓岩,向家彬,朱裕生,等.雷达信号处理[M].长沙:湖南科学技术出版社,1999.

[4]张丽娜.某型米波三坐标雷达多通道数字脉压模块的工程实现[D].西安:西安电子科技大学,2010.

[5]闫冯军,朱德智.IQ时序故障对数字脉冲压缩的影响[J].电子科技,2010,23(4):55 -57.

[6]宋晓风.多普勒频移对线性调频信号脉冲压缩的影响[J].电子科技,2009,22(4):42 -44,49.

[7]吴志毅,唐亚川.雷达风速补偿与脉冲压缩速度补偿的设计[J].电子设计工程,2013,21(14):55-57.