双端口存储器IDT7025信号量机制在双余度系统中的实现

张斌峰 陈 帅 孙爱中

(中国航空计算技术研究所,陕西 西安 710068)

双端口存储器IDT7025信号量机制在双余度系统中的实现

张斌峰 陈 帅 孙爱中

(中国航空计算技术研究所,陕西 西安 710068)

在双余度控制系统中需要频繁的大量数据交换,传统的并行接口和串行接口设计无论在通信速率,还是在可靠性方面都不易满足要求。而双端口RAM提供2套独立的地址,控制,数据线,同时提供信号量机制,是一个较好的实现方案。它具有通讯速率高、接口设计简单等特点,因而能在这类设计中得到广泛的应用。

互斥;信号量;CCDL;双余度

飞机自动驾驶仪系统多采用数字式双余度通道系统,通过飞控计算机的系统管理以及计算能力,提高系统的可靠性。

飞控每个通道分别采集信号源及反馈信号,通过数据交叉传输链路(CCDL)进行通道间的数据交换,完成输入信号的表决,将表决后的表决值提供给各自的处理器进行控制率计算,得出的结果再通过CCDL进行传输,对输出控制信号进行输出表决,最后将输出表决值送给伺服控制系统。

1 双余度通信机制

图1 原理框图

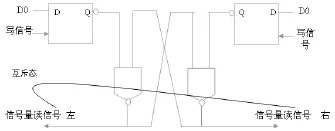

本文主要描述某飞行控制系统中如何通过(8K×16bit)IDT7025共享存储器实现双机之间CCDL通讯链路数据交叉传输的数据交互,完成双余度控制中的输入比较,输出比较。交叉通道数据传输电路的设计将双通道双口存储器分为两个区域A区和B区,双通道计算机分别将各自的表决信息存放在两个区域内;然后再分别从另一区域内取到另一个通道的信息进行表决。采用双口存储器作为交叉传输通道一方面可以节省双机交换信息的时间,另一方面则加大交换信息量。智能模块之间的通讯机制如图1所示。

2 共享存储器

数据获取及交换是多处理器系统的重要组成部分。在这类系统中,数据交换要求的通讯速率往往很高,平均速率一般在10kpbs左右,有时甚至达100kpbs以上。交叉传输包括:在数据采集之后的交叉传输。目的是为了检测双余度的计算机采样结果是否一致,传输的内容包括采样的数据及校验和;在控制律计算之后输出之前的交叉传输,目的是为了检测双余度的计算机根据输入表决监控的结果做出的输出是否一致,传输的内容是控制律计算结果、状态显示的结果及校验和。

双端口RAM芯片有两套完全独立的数据线、地址线和读写控制线,因而可使两个处理器分时独立访问其内部RAM资源。由于两个CPU同时访问时的仲裁逻辑电路全部集成在双端口RAM内部,因而需要实际设计的电路比较简单。双端口RAM内有一个总线抢占优先级比较器,只要双CPU不同时访问同一存储单元,那么较先送出地址的CPU将拥有该单元的本次访问优先权,而另一个CPU的地址与读写信号将被屏蔽掉,同时通过“busy”引脚告知该CPU以使之根据需要对该单元重新访问或撤消访问。双端口 RAM的优点是通讯速度快,实时性强,接口比较简单,两边CPU都可主动进行数据传输。

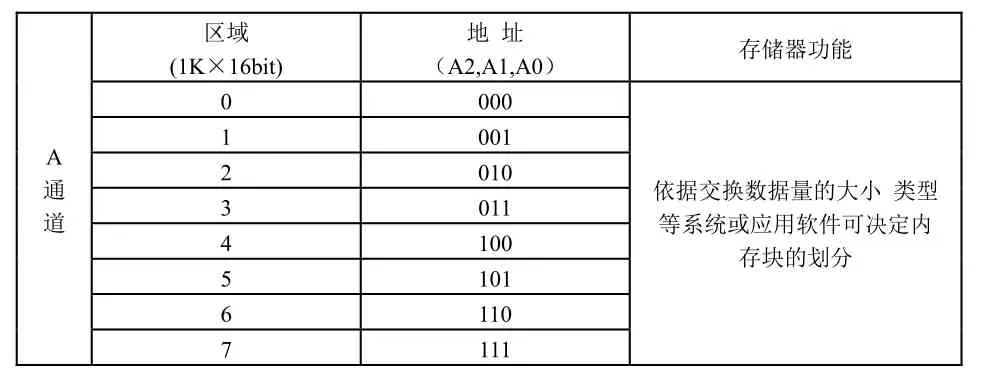

共享存储器选用双口存储器IDT7025,存储容量为8K× 16bit。双口存储器IDT7025具有防止双口竞争的功能,免去为避免双口竞争增加的硬件逻辑,通过使用芯片上的信号量可以获得芯片的控制权,只有获权的一组引脚上的信号才能访问存储器,通过信号量的使用还可以将双口存储器划分为不同的区。

3 信号量的实现

IDT7025内置8个二进制信号量。8个信号量实现8个不同资源的互斥访问。双余度每通道的处理器通过信号量的获取向另一端口的处理器声明本通道拥有对这一端口的优先存取权,此时另一通道不能对该端口存取,但是可以访问其他信号量所标示的资源。信号量硬件实现机制见图2。

图2 信号量控制原理图

A通道读出的信号量值与B通道读出的信号量值互斥。不能同时为0但可以同时为1。当左端口读出信号量值为1时,该端口可以存取。为了禁止右端口对内存的访问左端口处理器需要对二进制信号量写入‘0’以请求对该段内存的访问优先权,写入后必须进行读出操作已确认自己获得了信号量的令牌,当写入‘0’成功才能确保自己获得了对内存的单独控制权。写入未成功则任务挂起,直到该信号令牌释放。IDT7025的信号量控制机制见表1。

表1 IDT7025的信号量控制机制

双口存储器通过对信号量操作来防止竞争,对信号量的争夺可以使A、B通道中的一个获得优先控制权。

/SEM为信号量的片选信号,低电平有效;/CE为读写数据操作的片选信号,在操作信号量时此信号保持高电平;/OE为输出控制信号,由系统读信号控制;R/*W信号在读操作中保持高电平。当/SEM信号有效的情况下,任何一个通道都可以向信号量的八个锁存器中的一个进行读写操作,向锁存器的数据D0位写入“0”,如果写入成功就可以获得对一个区存储空间(1K字)的访问优先权,而另一个通道就不能对此区中任何单元进行访问,但是可以访问其它区域的单元。获得访问优先权的通道在完成访问之后可以通过向锁定区域的信号量锁存器写入“1”,双口会收回控制优先权,恢复另一通道的访问权。这种控制过程可以有效的防止出现竞争操作。表2为信号量的锁存器定义。

表2 信号量的锁存器定义

4 结束语

IDT7025存取时间20ns,16位数据宽度易扩展32位,64位以适应不同数据总线和数据量需求,同时减少了余度控制中 AB通道同步采集,对计算结果输出表决时的数据传输时间。忙标志引入,中断信号也可用于不同应用环境的原理设计。采用软硬结合信号量机制在多个飞控系统中得到典型应用,同时形成了一种设计思路,方法。

[1] 孔祥营,柏桂枝.嵌入式实时操作系统 VxWorks及其开发环境Tornado[M].北京:中国电力出版社,2002.

[2] 王梅,姬进.双余度信号容错处理与故障注入方法[J].电子科技,2013,(6):16-19.

[3] 俞健.多核 DSP图像处理系统的硬件设计[D].北京:中国科学院大学,2013.

[4] Integrated Device Technology. Inc High-speed 8k*16 dual-port static ram IDT7025S/L[M/OL].http://www.idt. com/document,2012.

Implementation of dual-ported memory IDT7025’s semaphore in redundant system

Many data exchange is needed in redundant control system.Traditional design use parallel-port or serial-port,they can’t meet Speed and reliability.Dual-ported ram suite to applications demanding the highest level of performance and reliability because of semaphore and two independedent ports with separate control,address and IO. So dual-ported ram is widely used in application of redundant control system.

Mutex; semaphore; CCDL;Dual-redundancy

V37

A

1008-1151(2015)04-0001-02

2015-03-12

张斌峰(1976-),男,陕西渭南人,中国航空计算技术研究所工程师,研究方向为计算机应用。