基于GDS的数字集成电路电磁场模型提取方法

王政集 刘 詝 粟 涛

(中山大学物理科学与工程技术学院,广州 510275)

射频电磁干扰是现代高速高密度电子系统中常见现象,是电子系统失效的主要原因之一。集成电路(IC)的射频电磁兼容性,是电子工业界关注的话题[1],也是国际标准机构关注的话题[2]。分析集成电路的射频电磁兼容性十分重要。

为保证制造出的集成电路能够正常工作,需要在设计阶段对电路的性能进行充分仿真。在设计阶段仿真 GHz波段射频电磁干扰在集成电路中的传输,需要为芯片的互连结构建立高精度的模型。电磁场仿真软件[3]可以从各种物体的三维电磁场模型中抽取出高精度等效电路。若能为芯片建立三维电磁模型,就可以得到适用于仿真射频电磁干扰的高精度模型。

现代数字类集成电路(包含以数字电路为主的系统芯片)通常包含数量巨大的走线线段、通孔、多边形等。以手工的方式,在电磁场仿真软件中画出原芯片互连结构的模型,在规模上是不可想象的,结果也是不可靠的。因此有必要研究一种方法,将芯片的设计文档直接完整的转化为三维电磁场模型。

1 电磁场模型的形式

当今国际上主流的大规模数字集成电路设计分析平台有 Synopsys,Cadence,和 Mentor。大多数的集成电路都是在上述三个平台设计完成的。主流的集成电路代工厂也主要或者仅为这三个平台提供设计工艺库。此外,我国自行开发了华大九天平台。出于后端时序仿真和信号完整性分析的需要,各个平台都开发了对芯片互连结构进行寄生参数提取的工具[4-8],见表1。这些工具以经验公式为获取参数的主要方式,其模型抽取精度和模型元件类型受到很大限制,不适合用于高频信号传输特性的分析。

表1 主要集成电路设计分析平台的参数提取功能

Q3D Extractor(以下简称Q3D)是ANSYS公司提供的用于建立等效电路的电磁场仿真软件[3]。相对与集成电路平台自带的参数提取工具,Q3D具有诸多优势:①它是高精度的电磁场仿真软件,适合高频信号分析;②它能全面提取包括电容、电阻、电感以及互感的各种参数;③它可对模型的环境、边界条件、负载等进行灵活的设置;④芯片模型可以和其他结构(如封装)模型进行合并;⑤在Q3D中建立的模型可以轻易的转化为 ANSYS其他仿真工具认可的形式,可对芯片进行力学特性、温度分布、电磁辐射等进行全面的分析[9]。

电磁场模型的形式与电磁场仿真软件密不可分。从以上分析可以看出,将芯片设计文档转化为电磁场模型时,选择 Q3D认可的形式是非常合适的。

各种集成电路设计分析平台使用的电路文档形式是不一样的。但是每个平台都会输出GDS文档作为流片用的掩膜版图数据。它是各类集成电路平台的通用电路形式。因此,我们选择将电路的GDS文档转化为Q3D模型。

2 电磁场模型结构的建立流程

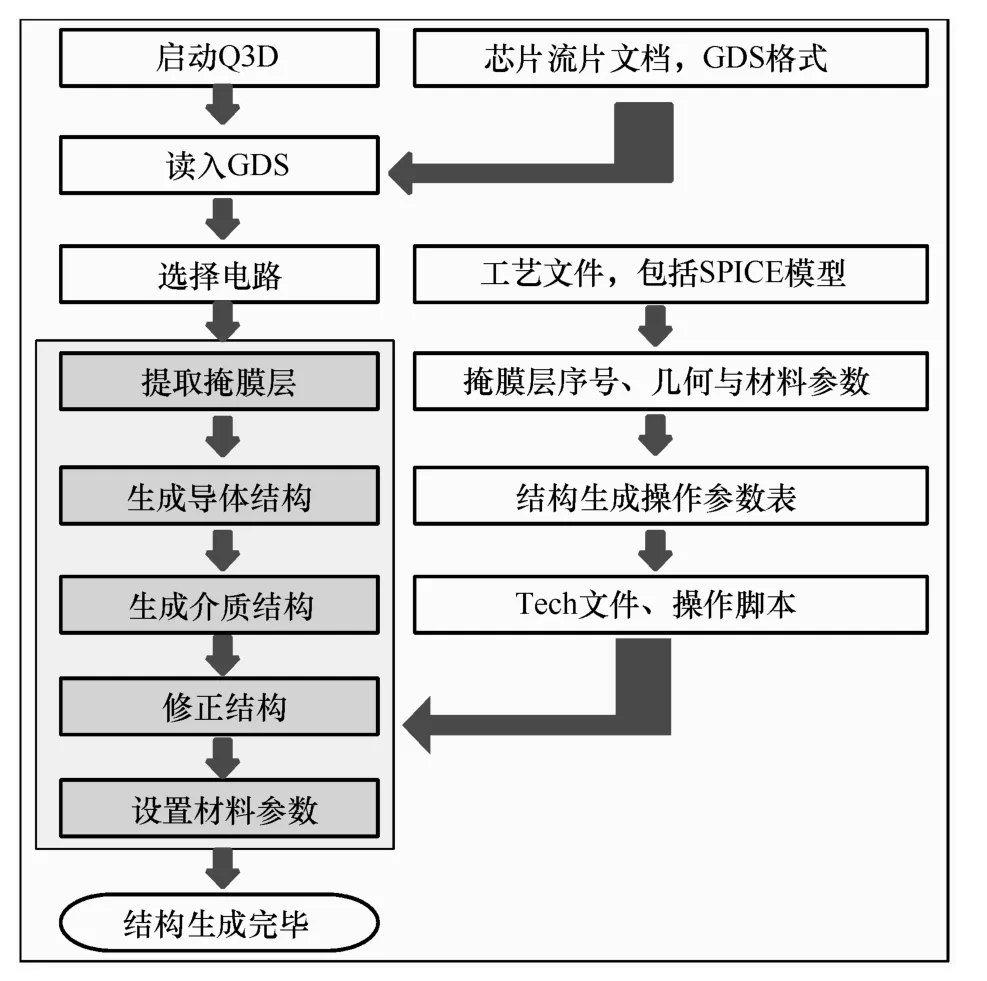

图1给出了建模的总体流程。若按照常规手动创建和修改集成电路模型成千上万个对象的方法将是不可接受的。所幸 Q3D自带一个 Iconic Python脚本接口,因此我们将通过剖析各个步骤,编写一个通用Python脚本,后续只需配置几个工艺参数,便可利用脚本实现自动化建模的全过程。下面分段描述各个阶段。

图1 芯片电磁场模型结构的建立流程

作为演示建模流程的操作样本,我们选用了中芯国际130nm设计库标准单元。使用标准单元,可以清楚地看到图示数字集成电路各结构元素的生成过程。生成功能芯片模型结构的过程与之完全相同。

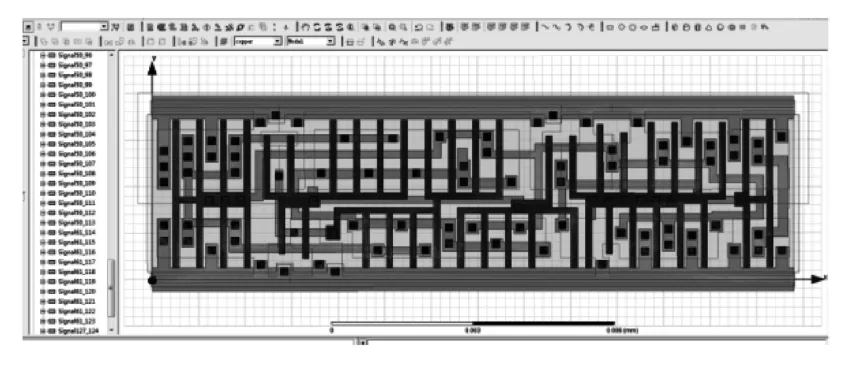

芯片的GDS文档由IC设计工具生成。它包含了电路的各层掩膜版图信息。一个GDS文档可以包含多个电路的掩膜版图。启动 Q3D,读入 GDS文档,可以看到电路的名单和掩膜层序号。选择电路名和序号,就可以将受测电路的各掩膜层导入Q3D中,得到此电路的Q3D掩膜图。图2给出一个驱动能力为4的加法器(ADDHX4)的掩膜图。每层掩膜都是平面结构。所有掩膜都堆叠在高度为0的位置,即z=0。

图2 导入Q3D的芯片掩膜层

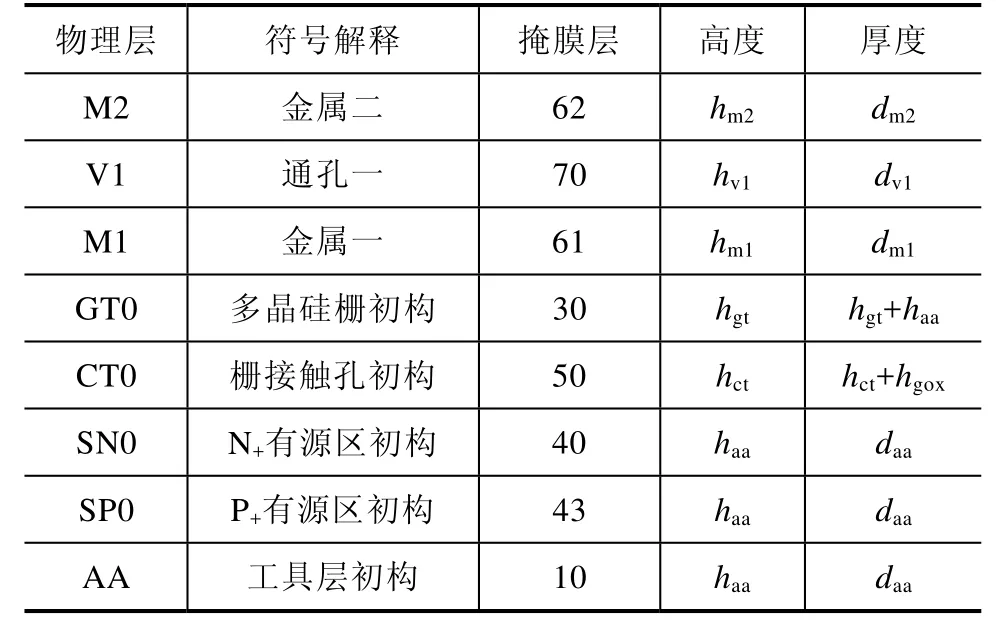

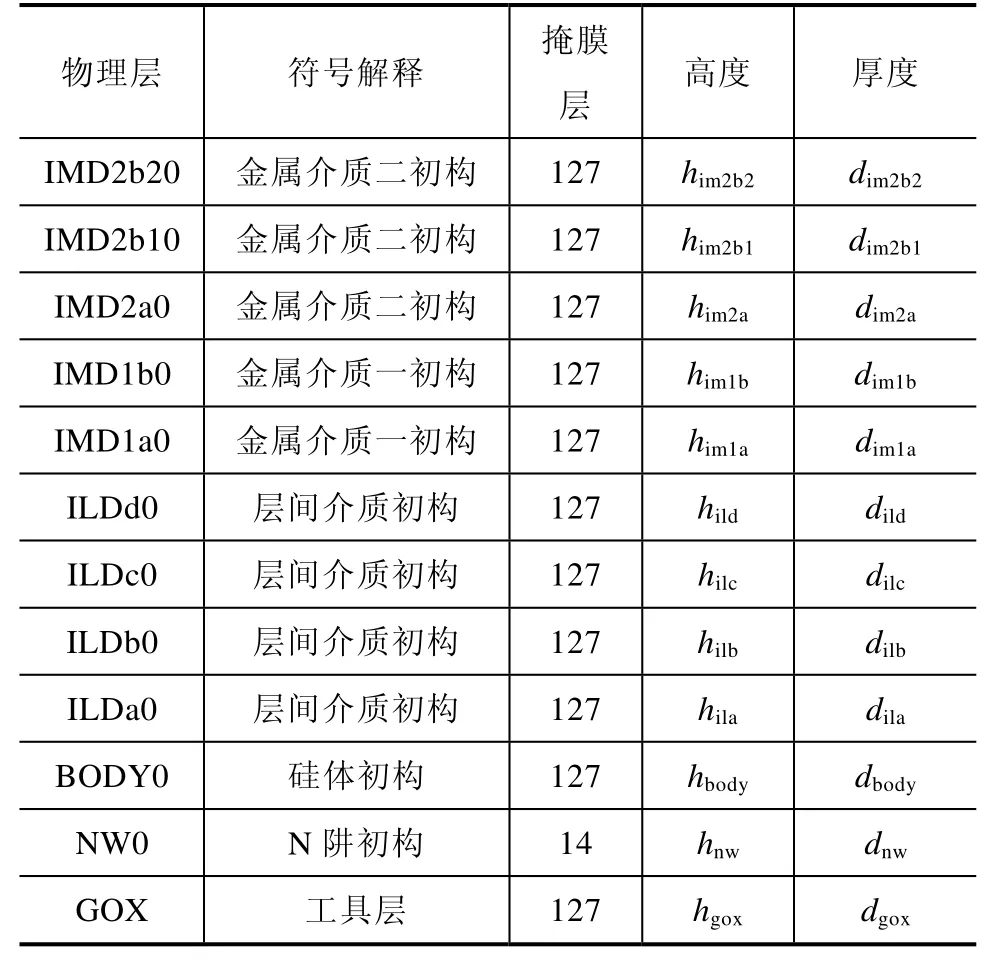

芯片是层状结构的物体。每一层由导体部分和介质部分组成。这里,有源区被视为导体。使用GDS文档中的掩膜层可以生成物理层。但掩膜层本身并不等于物理层。有些物理结构由单块掩膜生成,另一些结构则需要由多块掩膜层组合生成。在Q3D中使用掩膜层还原电路的物理结构,就如同进行一次虚拟的流片。这需要使用制程工艺信息。

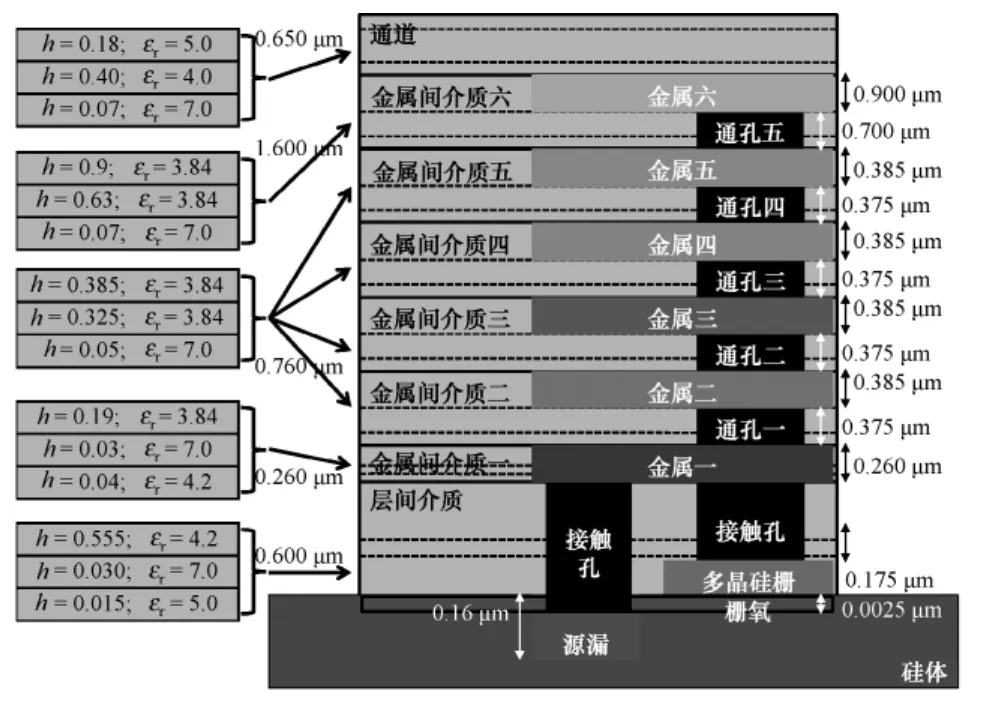

制程工艺信息包含两部分。第一部分是各物理层的位置、厚度与材料特性。这部分信息可以从工艺库中的寄生参数文件(如ITF)和SPICE模型文件中获得,由这些信息可以画出如图3所示的物理结构剖面图。

图3 制程工艺纵向截面图

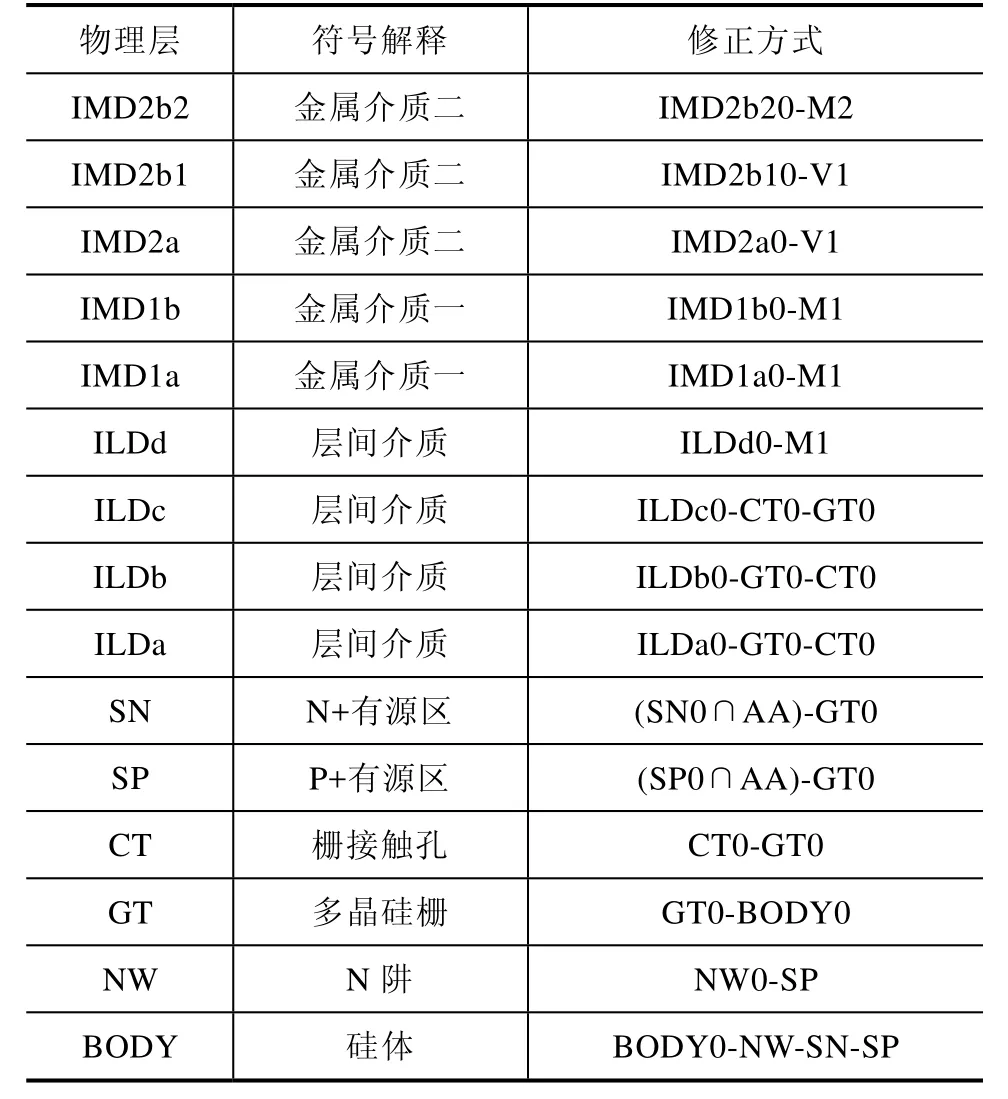

制程工艺信息的第二部分是各掩膜层的定义。使用这个定义,可以决定生成某一物理层所需要的哪些掩膜层。掩膜层的定义可以在设计规则文件和版图工艺映射文件中可以找到。根据这个文件,参考在IC设计工具中电路各物理层的规划,就可以制订出结构生成操作表。按照此表对掩膜层进行操作,可以生成符合图3规范的芯片物理结构。

芯片的物理结构包括导体和介质两部分。导体存在于介质里面。介质的外围形状取决于芯片外形,内部形状则取决于导体。因此,论文采用首先生成导体,然后生成介质的顺序来建立整个芯片的结构。

论文把生成结构的操作分为四种基本类型:①平移掩膜层,即M操作,使用Q3D中的“move”功能实现;②扩展掩膜层,即E操作,使用Q3D中的“sweep along vector”功能实现;③结构相与,即I操作,使用Q3D中的“intersection”功能实现;④结构相减,即S操作,使用Q3D中的“subtraction”功能实现。

生成导体结构的操作见表 2。每层导体参数值的来源如图3所示。为生成第k层导体,相关掩膜层将沿z轴正方向平移至hk的高度,然后往z轴负方向扩展dk成为导电立体。先把导体的高度和厚度参数写在Q3D工艺文件里,然后在提取GDS掩膜时采用脚本模式调用Q3D工艺文件(tech),就可完成生成导体的操作。需要指出的是,有些导体的结构并不完善(其符号后有0),此阶段得到的仅是初步的结构,还需要在后面进行修正。

表2 导体生成操作表

生成介质结构的操作见表 3。GDS文档里并没有介质层的掩膜,论文使用定义芯片边界的掩膜层来生成介质层。生成k层介质的步骤为,首先将边界掩膜复制后平移至在z=hk处,然后向下扩展生成厚度为dk的介质立体。这些介质立体,都是初始结构,将在下一阶段被修正。

表3 介质层生成操作表

进行结构修正的操作见表4。ILDd和IMD类的介质层要减去它所包含的金属、通孔结构。ILDa至ILDc要减去接触孔和多晶硅栅。接触孔分为两种,一种连接多晶硅栅和M1;另一种连接硅体和M1。两种接触孔的h相同,但d不一样。因此需要在接触孔掩膜扩展出的结构里减去多晶硅栅占用的区域。栅极下方的通道区,应从重掺杂区中剔除。在生成导体阶段,我们故意将多晶硅栅区扩展到硅体内有源区厚度的深度,以方便通道区的生成。N、P两个重掺杂区还要与 AA相与。栅极下还需要留出栅氧层。N阱和硅体都需要减去内部包含的其他结构。

表4 修正操作表

在完成几何结构的生成后,就需要对每个区域的材料特性进行设定。介质立体要赋予相对介电常数εk。导电立体要赋予电导率σk。芯片中的材料种类多。同为金属,不同层的电导率也会不一样。需要在Q3D里为表2至表4中的各层结构创立材料,然后将赋予这些结构相对应的材料特性,见表 5。为节省篇幅,表中用*号代替序号。

表5 材料参数设置表

经过上述过程,芯片的三维模型就被建立起来。通过我们优化的脚本,便可对同属性的一类对象进行操作,并实时输出建模进度到对应日志文件。通过配置几个参数,该脚本可适用于同一工艺的集成电路的三维电磁场建模。如上述过程的脚本,取名为SMIC130Q3D,则基于中芯国际130nm工艺的集成电路,都可以通过此脚本生成三维模型。

3 建模结果

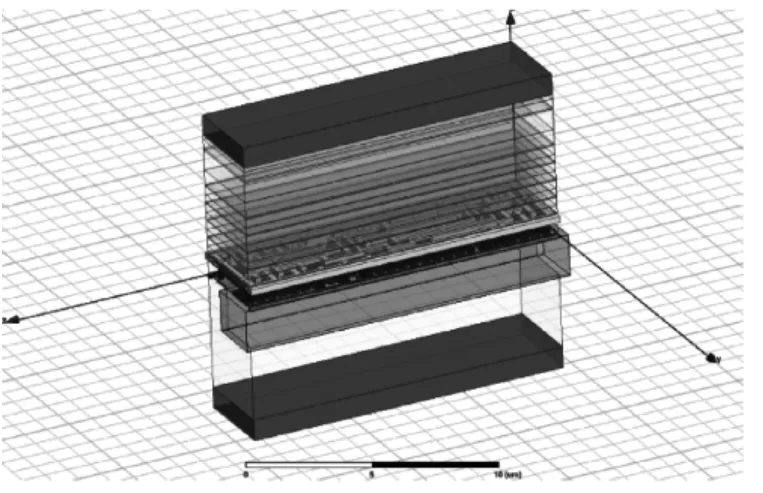

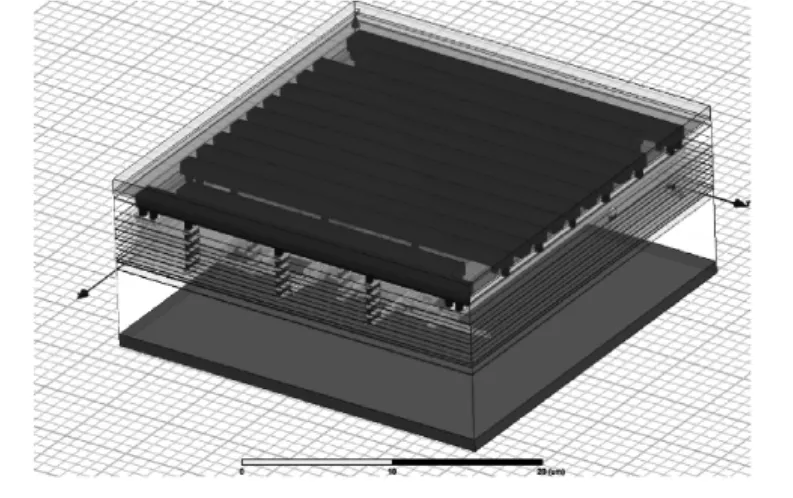

使用上述流程,分别为标准单元和功能芯片建立电磁场模型。图4为标准单元(ADDHX4)的建模结果(在 Q3D中显示)。它是一个驱动能力为 4的加法器。图5为一款功能芯片(counter)的建模结果。它是一个包含了电源网格的计数器。两款芯片三维模型的结构完整,各结构元素的位置、形状和尺寸都正确,结构元素间无重叠。通过Q3D模型检查,无错误信息。

图4 标准单元(ADDHX4)的三维模型结构

图5 功能芯片(counter)的三维模型结构

为进一步验证模型的有效性,我们对模型进行参数提取。在上述过程中,我们已经对其进行了三维建模并设定了模型材料和背景材料参数。之后我们采用自适应的网格划分法,输入误差百分比,跌代步数,每步细化百分比即可开始对其进行电磁场仿真,从而可以得到电路的电容矩阵、电阻、电感模型和等效电路。在这个过程中,求解电容时我们可以设置一系列频率进行扫描分析。在计算导体电容电感的时候,我们需要对其VDD设置源漏极,然后进行求解。求解完成之后,我们可以查看结果。

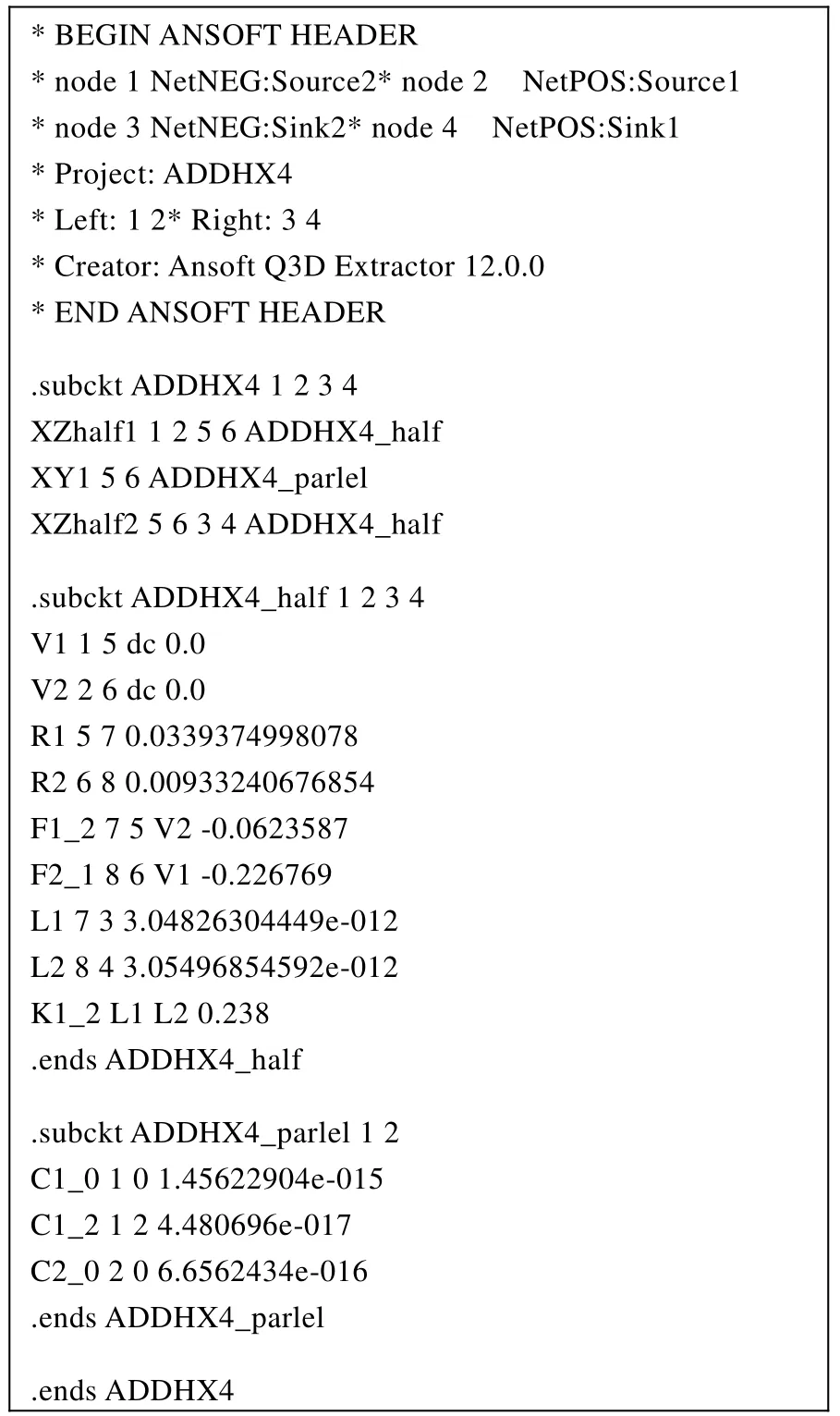

图6给出了ADDHX4的等效电路的SPICE网表。网表结构和参数均合理。功能芯片的抽取结果也合理。证明了模型的有效性。

图6 导出的SPICE网表构

4 结论

本文提出了一种建模方法,可以根据电路技术文档,自动生成集成电路复杂的互连结构的三维电磁场完整模型,并以SMIC 130nm 1P6M工艺为例对整个过程进行详细的描述。通过脚本形式可实现整个过程一键式完成。实验表明,使用此建模方法,可以使对集成电路标准单元和功能芯片建立精确的三维电磁场模型。操作规范,模型结构完整,能实现正确的参数提取,可重复。因此,此种建模方法是可靠和有效的。

[1] Joester M, Klotz F, Pfaff W, Steinecke T, Generic IC EMC Test Specification, German Electrical and Electronic Manufactures’ Association[J]. Frankfurt,Germany, 2010.

[2] Integrated Circuits-Measurement of Electromagnetic Immunity, 150kHz to 1GHz-Part 1: General conditions and definitions[J]. IEC Standard IEC 62132-1, 2006.

[3] Ansoft. Q3D extractor online help[Z]. 2012.

[4] Synopsys, StarRC User Guide and Command Reference, Version I-2013.12, December 2013.

[5] Cadence, QRC Extraction User Manual, Version 11.1 HF1, December 2011.

[6] Mentor Graphics Corporation. Calibre xRC user's manual, version 2011[Z]. 2011.

[7] Graphics M. Calibre xL user's manual, version 2011[Z].2011.

[8] Empyrean, RCExplorer, an on-chip interconnect parasitic extraction and analysis tool, http://www.empyrean.com.cn/html/en/edasolutions/rcexplorer/

[9] 杨华威, 袁广江, 肖刘. ANSYS接触单元在接触热阻仿真中的应用[J]. 微波学报, 2012(S2): 241-244.