多通道数据采集卡设计

陈光辉

(湖南科技学院 电子与信息工程学院,湖南 永州 425199)

多通道数据采集卡设计

陈光辉

(湖南科技学院 电子与信息工程学院,湖南 永州 425199)

交通管制监控,大型超市、公共场所安防领域,现代温室农业,都需要实时数据的采集与传输,能高效准确的采集到实时数据是核心。本文介绍基于PCI总线的高速多通道数据采集卡硬件设计,包括整体设计方案的解决,以及关键模块的电路详细设计和仿真。

数据采集卡;PCI9054;多通道

0 引 言

公共安全问题日益突出,大型超市内部的实时情形和监控管理[1]问题凸显,家庭轿车的普及,掌握主要路段的交通状况变得不可缺少。资源短缺、环境恶化与人口剧增的矛盾却越来越突出,如何用有限的耕地资源满足无限增长的人口需求困扰着世界各国。发展高科技现代农业[2,3],实时掌控农田土壤中的营养成分,通过及时调整土壤营养满足农作物的生长需要,达到高产。交通管制监控[4,5,6],大型超市、公共场所安防领域实时监控,现代温室农业中的温度、湿度的实时监控,数据采集系统[7,8]是监控系统的核心部分。本数据采集卡就是用于解决如何采集实时信息,跟换不同数据接受模块可以完成不同信息的采集,能有效降低设计成本。

1 硬件整体设计方案

本数据采集卡使用PCI接口芯片与FPGA相结合的方案, 系统硬件结构图如图1所示。数据采集卡只能处理数字信号,接收到的音频信号、视频信号、温度、湿度信号都是模拟信号,所以需要首先将模拟信号转换成数字信号。一次可以接收最多四通道模拟信号并完成模数转换。采集到的数据量比较大的情况下,数据来不及传输出去,就需要RAM来缓存。可以选用单独是RAM或者SDRAM来做缓存,由于本方案采用FPGA芯片,FPGA内部有一定数量的存储单元,可以直接运用这些存储单元来缓存数据,既减少开发周期,又能减少开发成本。数据采集到后,要传输给数据处理芯片,本设计采用PCI总线协议,支持32位/33MHz;本地端可编程实现8、16、32位数据宽度,传输速率最高可到132M字节/秒,本地总线端时钟最高可达50MHz,支持复用(J模式)和非复用32位地址/数据(C模式),还直接主模式,直接从模式和DMA模式。缓存到存储单元中的数据按照PCI协议传输给主机,从而完成数据的采集和传输过程。数据采集卡包括模数转换模块、数据缓存模块、数据传输模块等。

2 模数转换模块

模数转换模块主要完成对接收到的各类模拟信号转换成数字信号,选用analog公司生产的AD7819芯片。工作电压范围是2.7~5.5v,8-bit并行数据接口。在57.75μW功耗下数据后传输速度为1kSPS。总共有四个通道,可以单独选择莫一通道,也可以任意选择多个通道。通道的选择通过AD控制器,应用FPGA编程实现。DB_AD1/DB_AD2/DB_AD3/DB_AD4为采集输入信号,FIFO_out为采集到数字信号

图1. 硬件结构图

图2. AD控制器仿真

图3. 模数转换仿真数据缓存设计

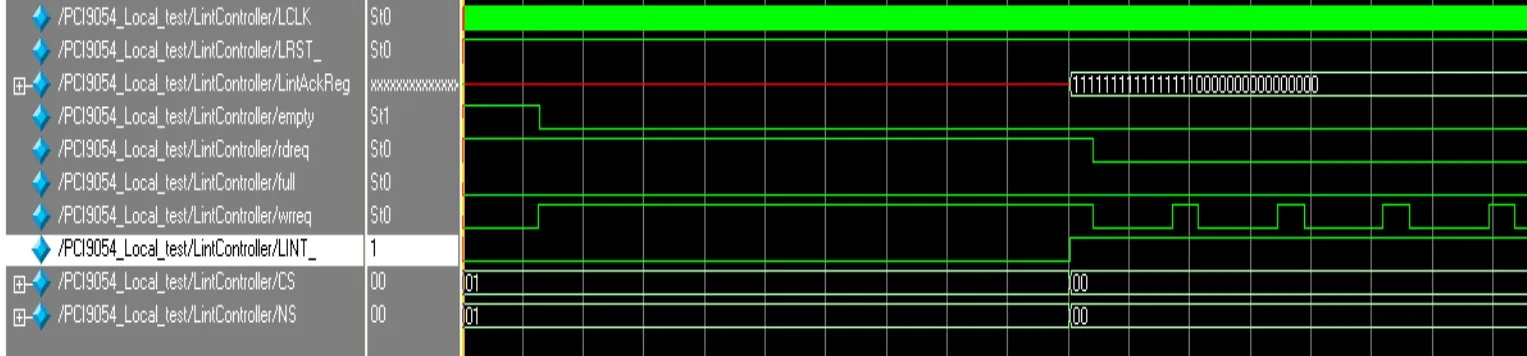

经A/D转换后的数字信号,如果数据量比较大,那么首先需要把数据缓存起来以免丢失,造成信号的不完整。可以采用单独的存储芯片,如SDRAM,SRAM等,这样可以缓存更多数据,但是这样的设计复杂度和设计成本增加,由于选用FPGA芯片来实现粘合逻辑,并且FPGA芯片中含有丰富的FIFO存储单元,读写方便,速度也快,这就正好解决数据缓存的问题。FIFO的读写要注意,不能空读,满写。这样也会造成数据的丢失。如何控制FIFO的读写,也是通过FPGA编写FIFO控制器来完成。Rdreq、wrreq为读写请求信号,empty、full为fifo空满标志位。

图4. 数据缓存仿真数据传输

A/D采集到的数据输入到FIFO中(写入FIFO),PCI9054通过读操作,读取LocalBus端的数据,也即是FIFO的读操作。当PCI9054读取FIFO中的数据时,A/D采样的数据连续不断的写入FIFO中,如果产生FIFO满时(full),此时FIFO的写信号有效(即继续向FIFO中写数据),或者当FIFO的empty有效的时候,此时读信号有效(即继续读FIFO),则产生本地端中断(LINT#)。

图5. 中断发生仿真

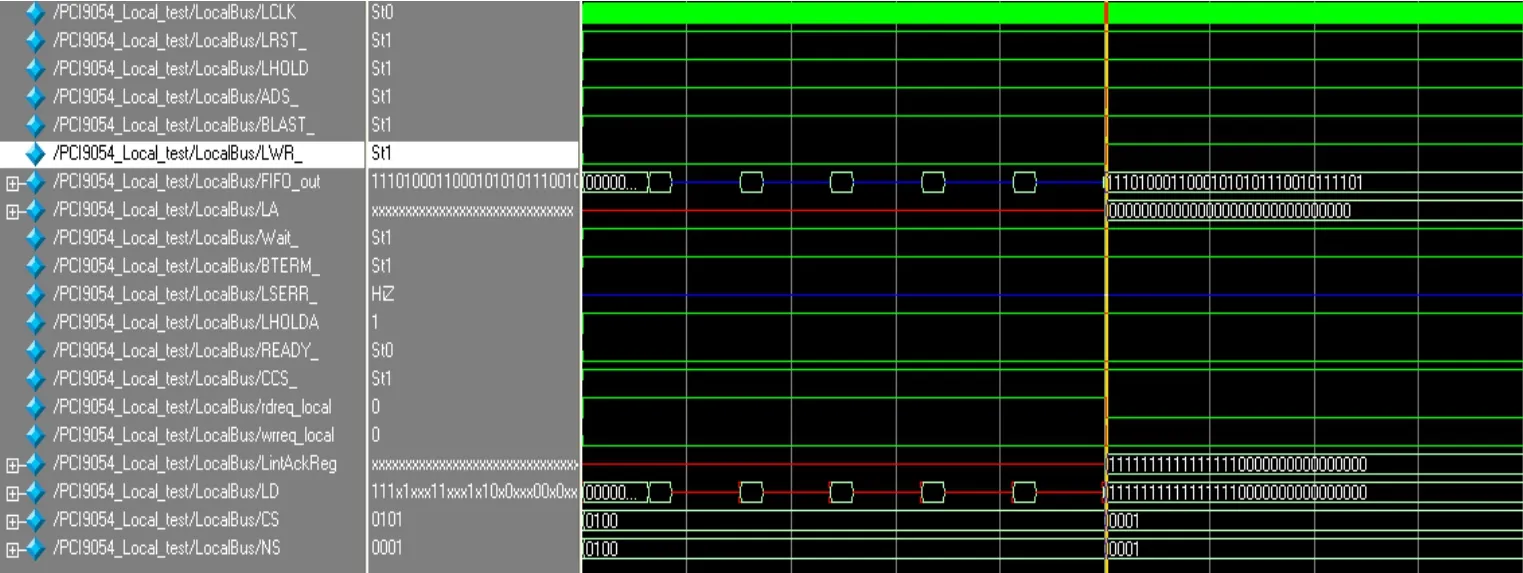

数据按照PCI总线协议传输,PCI总线支持32位/33 MHz,本地端可以传输8、16、32位宽的数据,数据传输速率可达132 MB/s。本文使用PCI9054桥接芯片在LocalBus和PCI总线之间传递信息。PLX公司生产的PCI 总线通用接口芯片PCI9054,应用PLX数据管道结构技术,适合PCIV2.1和V2.2协议规范。PCI9054提供两个独立的可编程 DMA 控制器,都支持块和分散/集中的DMA方式。本地总线支持复用/非复用32位地址数据,本地时钟最高可达50 MHz。在数据传输工程中,PCI9054既可以作为主设备去控制本地总线,发送传输数据的命令,也可以作为LocalBus的从设备把LocalBus端数据传输给PCI总线。同时PCI9054含有6个零等待可编程FIFO存储器,用以完成PCI发起读、写操作,以及PCI目标写、读操作和DMA写、读操作。正是存在FIFO存储器,数据可以大量突发传输而不丢失。

图6. 数据传输仿真图

具体过程为,当AD7819的读信号有效,就把AD7819采集到的数据传入FIFO中,当PCI9054从LocalBus端读取数据时,则FIFO的读信号有效。当PCI9054读取数据快/慢于FIFO采集到的数据时,则empty/full有效,此时产生中断,产生中断后,等待PCI控制端向Local端写一个中断信号(通过LD总线),当Local端“读到”(即当LocalBus端的LD为事先约定好的数据时,则表明PCI控制器已经接受到中断)。在AD7819数据可被读出的时候,即RD_信号有效,此时FIFO的写入信号应该有效,且一个时钟写入data后,立刻无效,等待下个AD7819可读周期,以此连续反复,则AD7819的RD_信号可以作为FIFO写入使能的判断信号。

3 奇偶校验

当PCI9054从LocalBus端读取数据时(编写程序的时候注意读信号有效),那么LD相对LocalBus端为输出数据,则在PCI9054中会进行奇偶校验,在LocalBus端自己设计奇偶校验程序,并得出一个奇偶校验位DP_local,然后把产生的奇偶校验位作为PCI9054的奇偶校验位DP[3:0]的输入,PCI9054内部应该会比较本地端输入的奇偶校验位和内部产生的奇偶校验位是否相等,而给出系统数据错误提示。

4 印制电路板制作

此印制板电路设计为4层(底层、顶层、电源层、地层),系统电压为3.3V。本设计采用屏蔽、隔离、抑制、接地保护等技术进行抗干扰处理。在 PCB 板电源加10μF的电解电容或钽电容和0. 1μF的电容去除高频或者低频干扰,在芯片电源与地之间加0. 1μF去耦电容。

5 结束语

本文设计一款多通道的数据采集卡,最多能同时采集4路不同数据。使用FPGA来实现数据采集卡中的粘合电路,通过现场可编程器件设计的灵活性可以方便改变数据采集卡的应用场合。如,可以进行通道的选择,数据采集类型的选择等等。此数据采集卡是本人在公司所做项目,已经可以完成音频和视屏信号的采集应用。

[1]裴喜龙,童莉.基于PCI总线的高速数据采集卡系统设计与实现[J].北京:微计算机信息,2006:1-5.

[2]王勉.高效设施农业发展现状及趋势分析[J].经济论坛,2012,(02) :108-111.

[3]部琴.农业经济发展方式转变浅析现代经济信息,2011,(10).

[4]北京欧立信经济信息咨询中心,2008-2009年中国智能交通行业市场研究分析报告,2008.

[5]王海涛,黄文杰,朱永凯,田贵云,姬建岗.基于聚类分析与神经网络的车牌字符识别[J]数据釆集与处理,23(2):238-242,2008,(2).

[6]路雪超,刘桂雄,冯云庆,申柏华.一种基于车牌特征信息的车牌识别方法[J]华南理工大学学报(自然科学版),31(4):70-73, 2003,(4).

[7]景志,马琰森.基于PCI9054 的数据转换模块设计[J]电子设计工程,2011,(1).

[8]韩士胜,吴华春.基于PCI总线的多通道数据采集卡的设计[J]仪表技术,2009,(5).

(责任编校:宫彦军)

TP29

A

1673-2219(2015)05-0037-04

2014-12-08

湖南科技学院校级项目资助(项目编号13XKY103)。

陈光辉(1983-),男,四川资阳人,湖南科技学院电子与信息工程学院教师,主要研究方向:集成电路设计与验证,系统设计,数字信号处理。