基于FPGA的超清户外LED屏数据流控制系统*

李志坚 吴朝晖 李斌

(华南理工大学电子与信息学院)

基于FPGA的超清户外LED屏数据流控制系统*

李志坚吴朝晖李斌

(华南理工大学电子与信息学院)

针对现有LED控制系统视频数据采集卡与视频数据接收卡分离的问题,设计基于FPGA的超清户外LED屏数据流控制系统。该系统把高清视频数据采集、高速视频数据控制模块、高速数据缓存模块、非易失性存储模块、多路串行视频数据输出模块和通信控制模块集成在一块电路板,具有高度集成、超大带宽、超低延迟的特点,可实现1080P全彩色,120帧/秒的视频播放,系统延迟在2帧以内。

FPGA;LED显示;高速数据流控制

0 引言

目前,大型LED显示屏在户外广告、舞台布置等领域应用广泛[1-2]。不断出现的应用需求,推动了LED显示屏控制技术的发展。大带宽、高实时性是LED高清显示屏控制技术的发展趋势。

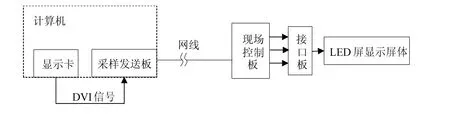

现有的LED显示屏同步控制系统如图1[3]所示,一般包括采样发送板和多个级联的现场控制板。采样发送板接收视频源数据,并在完成数据格式转换之后,通过网线或者同轴电缆传送给现场控制板[4-5]。在分辨率和实时性要求不高的应用中,该方案具有很好的性能。但要实现高分辨率和高保真性显示,现有的方案只有在视频源与发送卡之间增加图像分割设备,并通过多通道并行的方式才可能实现。

图1 典型LED屏控制系统框图

本文基于FPGA设计超清户外LED屏数据流控制系统,把高清视频数据采集、高速视频数据控制模块、数据缓存模块、非易失性存储模块、多路串行视频数据输出模块和通信控制模块集成在一块电路板上,省去了专门的图像分割和数据分发设备。

1 系统性能设计

1.1系统输出带宽设计

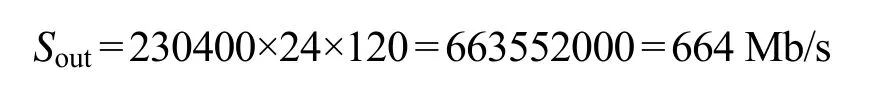

LED屏视频数据流控制系统的核心任务是根据所控制的LED显示屏的拓扑结构,把来自于视频源的高速串行视频数据并行化,以实现高清LED屏的高刷新频率。本系统的目标高清LED显示屏包括并行的9个LED阵列。每个LED阵列的像素数目为230400个。因此,本系统设计9个并行视频数据输出端口。若播放24位真彩图像,为保证120 Hz的帧频,每个视频输出端口最小带宽为

系统中,控制器除了分配视频数据外,还需要对显示控制单元进行参数配置和状态回读,因此实际数据量将略高于Sout。

基于上述通信数据量分析,并考虑协议开销,系统视频输出端口带宽应不低于700 Mb/s,可采用CAT5、CAT5E或者CAT6网线连接。考虑成本等因素,本模块输出端口采用CAT5类网线接口。

1.2系统输入带宽设计

如上所述,每个显示控制单元的输入带宽为700 Mb/s,数字收发模块的视频输入口带宽最小为

在此基础上,考虑10%的通信裕量,数据收发模块视频输入端口带宽应不低于7 Gb/s。

在接口设计方面,HDMI接口能满足上述的视频传输带宽要求。

1.3系统存储容量设计

LED显示屏是逐点顺序显示的,它利用人眼视觉延迟的特点,通过一次快速发送全屏所有点的图像实现全屏图像显示更新。因此,为确保图像正常显示,在发送之前,必须先确定显示屏的走线方式或走点顺序。确定走点顺序的过程称为LED屏描点,它通过间隔一段时间(如1 s)发送一个点,然后记录其位置即可确定。

控制系统在向LED显示屏发送数据时,严格按照描点文件顺序发送各像素的灰度数据。为实现上述功能,控制系统必须在本地缓存一帧视频数据。此外为了匹配每个环节的输入输出速度,也需要对视频数据进行缓存,以实现诸如乒乓存取等操作。

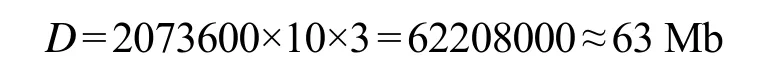

系统控制的像素总数为1920×1080=2073600个,若所有像素统一编制,则地址位宽为21位。因此,描点文件缓存空间为

前端数据收发模块必须在本地缓存一帧视频数据,数据大小为

此外,为匹配不同速度,要在视频数据处理中间增加乒乓操作,需要消耗一定的存储资源。FPGA本身的网表文件也需要存储在收发模块本地。因此,收发模块中的存储容量包括上述的所有部分,应不低于120 Mb。

2 系统架构

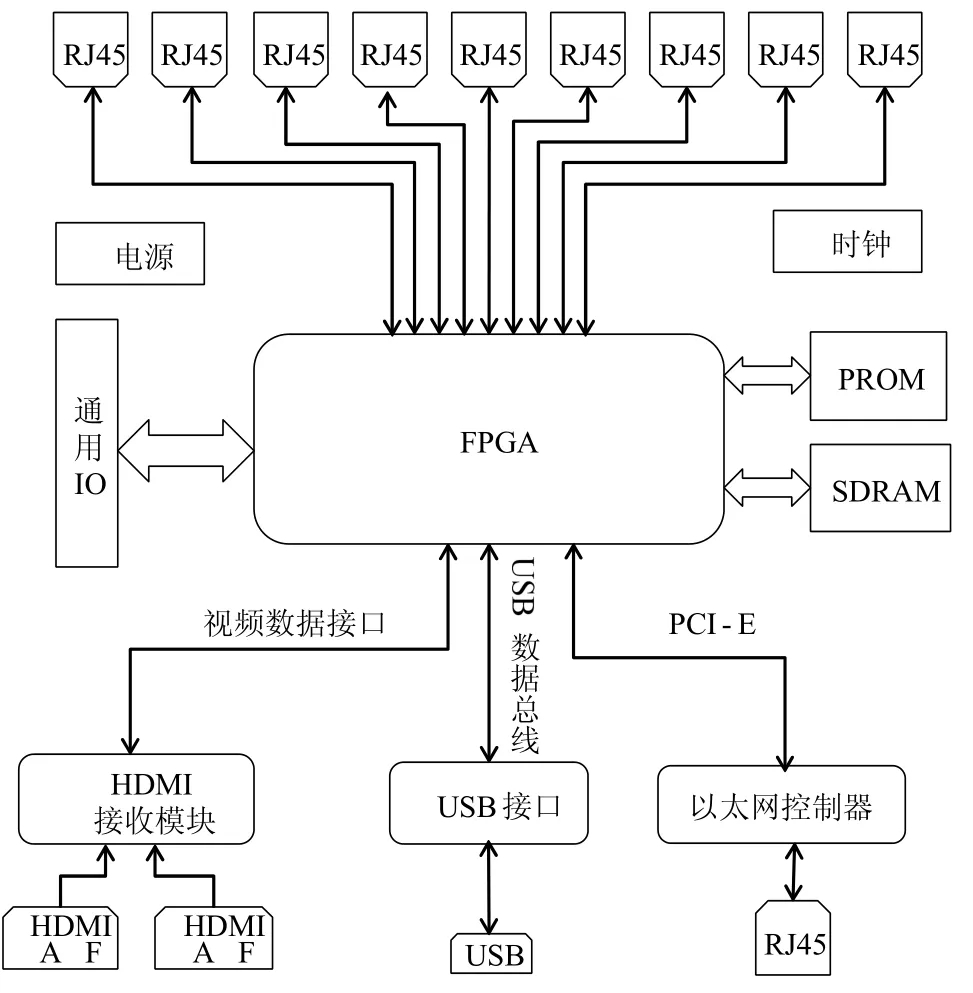

根据上述性能设计要求,系统架构如如图2所示,包括HDMI接口模块、板上缓存单元,高速串行传输模块、中央控制模块、USB、LAN和通用IO口。系统还预留用于移植嵌入式操作系统的系统存储单元。

图2 系统架构

HDMI接口模块从视频源的HDMI接口采集高清视频数据信号。HDMI主要基于转换最小差分信号(transition minimized differential signaling,TMDS)技术传输数字信号。

板上缓存单元主要用于缓存视频数据处理中间结果,实现输入输出带宽匹配。系统采用大容量DDR-3 SDRAM实现视频数据的高速存取。

根据系统最终规模以及前端LED频的控制接口,本系统的视频输出口包括12路CAT-5网线端口,其中9路正常输出,3路备用。

中央控制模块是本系统的核心,主要功能包括视频处理、高速数据流控制和通信控制功能。其中,视频处理包括伽马矫正等常用处理方法,也包括针对不同目标显示屏的图像重构。这里图像重构是指中央控制器对目标LED显示屏进行描点操作,建立视频数据与目标LED屏像素的映射表,并基于此映射表对每一帧图像进行图像重构。高速数据流控制是指中央控制器接收来自HDMI接口模块的视频数据,采用乒乓操作的方式把当前处理结果存入SDRAM,同时从SDRAM中读取上一帧已处理的视频数据,并把这些数据通过高速串行传输模块馈送给LED屏。通信控制是指中央控制模块通过网口、USB口和通用IO接口接收来自远程控制系统的控制命令,并把本机状态信息通过这些接口反馈给远程控制系统。

3 系统实现

根据上述分析设计,系统围绕超大规模FPGA构件应用系统,系统内部拓扑如图3所示。

图3 系统内部拓扑

3.1HDMI接口

根据前文分析,视频接口带宽应不低于7 Gb/s。考虑通信裕量,系统视频接口带宽设置为7.5 Gb/s。本系统采用ADV7619[6]芯片实现高速视频数据流的接收。该芯片可支持最高达1080 P 36位深色/2160 P 8位的高清电视格式和最高达4 k × 2 k(3840 × 2160,30 Hz)的显示分辨率,能够满足系统1 k × 2 k(1080× 1920,120 Hz)显示分辨率及刷新速率。

3.2FPGA

FPGA选型考虑以下几点:1) 本系统的缓存采用DDR SDRAM,因此所选FPGA应支持DDR-III接口开发能力;2) 由于本系统需高速处理视频数据,在LED屏分辨率较高时,要消耗大量的逻辑资源,低成本的Cyclone系列FPGA无法满足项目需求,因此本系统采用Arria V GX系列FPGA[7]。

Arria V GX使用28 nm低功耗工艺实现最低静态功耗。在中端应用中,总功耗是最低的,还提供速率高达10.3125 Gb/s的低功耗收发器,设计了具有硬核IP的优异架构,从而降低动态功耗。与前一代中端FPGA相比,Arria V器件的平均功耗降低了40%。

单片FPGA满足项目IO需求的封装为F1152和F1517。但在实际设计时,由于不同接口的电平标准不一致,FPGA的IO利用率不能达到100%,同时考虑到大封装扇出困难,本系统采用主从FPGA的方式来实现。

主FPGA完成视频数据的接收、显示屏描点、DDR3存储器接口等功能,需求的逻辑资源比较高,且要求具有DDR3存储器接口硬核和PCIE硬核,因此采用5AGXFB7D6F35C6N,该芯片为F1152封装。从FPGA主要完成视频数据的多路分发,拟采用5AGXBA5D6F27C6N,该芯片为F672封装。主从FPGA之间从高速串行接口交换数据。

3.3SDRAM

本控制模块的目标屏分辨率是1920×1080 P,在无压缩情况下,一帧图像的数据量为1920×1080×30 = 62 Mb。为匹配收发速率,同时完成描点功能,控制器需采用乒乓操作。因此,控制模块视频数据缓存容量不低于130 Mb。这个存储要求,目前在单片FPGA内部尚不能实现,需在片外扩展大容量存储器。

同时,为保证120 Hz帧频,片外存储器实际吞吐率应不低于7.5 Gb/s,即240 MDW/s(1 DW = 32 b)。

能达到上述吞吐率要求的片外存储技术包括SRAM和DDR SDRAM。因大容量SRAM价格昂贵,本系统采用片外扩展DDR SDRAM的方案实现视频数据高速缓存。

为了保证1080 P的LED显示屏分辨率和120 Hz的帧频,作为视频数据缓存的DDR SDRAM访问带宽应不低于7.5 Gb/s,同时考虑数据格式转换和数据对齐,DDR SDRAM访问带宽应不低于10 Gb/s。

考虑硬件的稳定性,系统采用DDR3 SDRAM,工作频率为800 MHz。在具体选型上,采用H5PS5162GFR-S5C[8]。该芯片是DDR3 SDRAM,工作时钟800 MHz,存储容量512 Mb,数据位宽为16 B。设计时,采用两片并联形成1个32 B数据总线。

3.4其他电路

系统视频输出口采用网口形式,所用的PHY芯片选型主要考虑1000 b/s的传输带宽。从技术支持的角度,本系统采用RTL8211芯片。

USB接口主要完成系统参数配置和系统调试,本系统拟采用CY3014芯片,该芯片具有1个可进行完全配置的并行通用可编程接口GPIF II,它可与任何处理器、ASIC或 FPGA连接。

网络控制器采用RTL8111C-GR以太网控制器,该芯片内部集成了兼容IEEE 802.3 10/100/1000 Mb/s媒体接口控制器(MAC)、10/100/1000 Mb/s以太网收发模块(PHY)、PCIE总线控制器和嵌入式存储单元。

4 结语

LED全彩同步控制系统具有高性能、实时显示、节能、环保等优点,是现代信息发布的重要媒体。本文改变传统设计发送卡与接收卡分开的结构,把视频数据采集、分割、格式转换和发送集成在一张卡上。系统充分利用可编程逻辑的控制性能强,开发灵活和资源丰富的特点,以高性能FPGA为核心,结合高速缓存DDR3 SDRAM技术,设计了高度集成的超清户外LED屏数据流控制卡。设计带宽达到7.5 Gb/s,能满足1080 P高清视频放送,传输延迟不超过1桢。系统具有成本低、显示面积大、显示稳定、刷新率高、规模可扩展等特点,是目前市面上具有竞争力的显示控制方案。

[1] 李韬.LED电子显示屏控制系统设计[J].科技与创新,2015(18):73,76.

[2] 赵红艳.LED 显示屏控制系统的分析与设计[J].电子技术与软件工程,2015(4):82.

[3] 刘丽莎 朱桦 韩秀清.基于网口传输的LED同步屏控制系统及其FPGA实现[D].电子设计工程,2010,18(2):63-66.

[4] 魏洵佳.超高清LED显示屏单卡网线控制系统设计[J].北京信息科技大学学报,2012,27(3):68-72.

[5] 王燕.多LED显示屏协同控制系统设计及应用[J].西安工程大学学报,2015,29(2):187-194.

[6] www.analog.com,Dual PortXpressview3 GHz DMI Receiver ADV7619 datasheet[Rev.C].

[7] www.altera.com,Arria V GX, GT, SX, and ST Device Datasheet[Rev.3.3].

[8] www.hynix.com, DDR3L Device Operation.

Ultra-HD Outdoor LED Screen Data Flow Control System Based on FPGA

Li ZhiijanWu ZhaohuiLi Bin

(School of Electronic Engineering, South China University of China)

In current LED control systems, the video data acquisition card and video data receiving card are separated from each other. The ultra high definition outdoor LED screen data flow control system is designed based on FPGA. In the proposed system, the video data acquisition, high speed video data controller and buffer, non nonvolatile memory, multi serial video data output module and communication control module are integrated on a single circuit board. The system is characterized by high degree of integration, ultra large bandwidth and ultra low delay. It can achieve 1080 P full color, 120 frames per second video playback, with the system delay in 2 frames or less.

FPGA; LED Display; High Speed Data Flow Control

李志坚,男,1981年生,讲师,主要研究方向:高速数字信号处理及系统设计、RFID应用技术。E-mail: Lizhjian@scut.edu.cn

广州市科技计划项目产学研专项(2014Y2-00018);荔湾区产学研合作项目(20144815023)。