一种滞回比较器设计

薛腾飞,朱 江,乔 明

(1. 电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054;2. 辽宁锦榜电气有限公司,沈阳 110141)

一种滞回比较器设计

薛腾飞1,朱江2,乔明1

(1. 电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054;2. 辽宁锦榜电气有限公司,沈阳 110141)

比较器广泛应用于模拟信号到数字信号的转换过程中,在模-数转换过程中,对输入进行采样后的信号通过比较器以决定模拟信号的数字量。滞回比较器也叫迟滞比较器,以其优越的抗噪声能力在比较器中占有重要地位。描述一种滞回比较器,使用少量元件节省成本,滞回电压阈值设计灵活,同时用P管作差分输入管,有较高的共模输入范围,转换速率快。使用0.18 μm CMOS工艺分别对转折点压差为200 mV的设计进行仿真,仿真结果与设计预期相符合。

模数转换;抗噪声能力;滞回比较器

1 引言

比较器常用于保护电路,模拟输入信号和参考电压作为输入信号,输出数字信号作为控制信号。通常情况下,比较器工作在噪声环境中并且在阈值点检测信号的变化[1]。一般的快速比较器会对噪声产生响应,输出端也存在噪声,而滞回比较器具有很强的抑制噪声能力,从而输出符合要求的低噪声数字信号。

本文分析了滞回比较器的原理和优势,介绍了一种通过外部正反馈实现的同相迟滞比较器结构,并提出了一种通过内部正反馈实现的同相滞回比较器设计,最后用0.18 μm、2.5 V的CMOS工艺对设计进行了仿真分析。

2 滞回比较器原理

滞回比较器的输入阈值是输入或输出的函数,当输入电平经过阈值时输出会发生改变,同时输入阈值会随之降低,所以在比较器的输出又一次改变状态之前必须回到上一阈值。当输入由负值正向变化的时候,到达转折点VTRP+时输出由VOL变化为VOH,此时转折点发生变化,即输入由高到低变化时,只有达到VTRP-输出才会由VOH翻转到VOL。

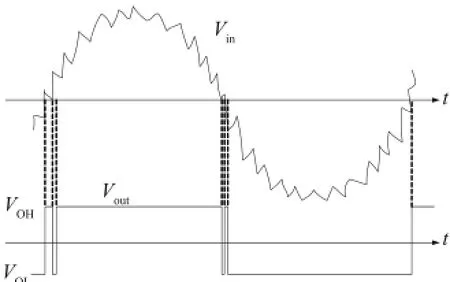

滞回比较器的优点如图1和图2所示,工作在噪声环境中时,如果滞回比较器的迟滞电压幅值大于噪声幅值,就可以很好地抑制噪声的输出,在保护电路中工作时可以很好地防止电平抖动引起的误翻转。

图1 非滞回比较器对噪声输入的响应

图 2 滞回比较器对噪声输入的响应

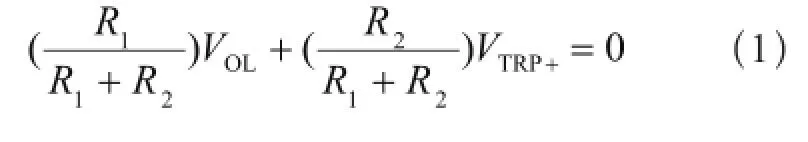

图3为利用外部正反馈得到的同相滞回比较器,如图所示比较器的最大输出电压和最小输出电压分别为VOH和VOL,两个转折点分别为VTRP-和VTRP+。VIN由负值增加到达上转折点VTRP+时,

这种结构一般VOL为负值,因此VTRP+是正值。同理求解下转折点:

从而滞回阈值为:

3 本文设计的滞回比较器

本文中设计的滞回比较器基于0.18 μm、2.5 V的CMOS工艺,常用于过温、过压、过流、欠压保护电路中。利用外部正反馈得到的比较器不利于集成,功耗也比较高。因此本文设计了一种新型的利用内部正反馈实现的滞回比较器。

图3 基于外部正反馈的同相滞回比较器

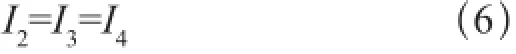

如图4所示,滞回比较器的工作原理为:采用两级开环比较器结构,两级比较器的输出电压V1外接M8和M9构成的反相器作为输出缓冲级,同时M8和M9组成的反相器可以接很大的容性负载而不影响比较器的响应速度,M10和M11构成的电流镜为比较器提供偏置电流,PMOS管M2和M3是差分输入管,并且M2和M3的共源节点构成串联电流反馈通路,是一条负反馈通路[2,3],而连接M12和M13的栅-漏极电压是正反馈通路,当正反馈系数大于负反馈系数时,电压的传输曲线就表现出迟滞的特性。因此在设计过程中PMOS管M2和M3与NMOS管M12、M13要选择合适的宽长比。

图4 基于内部正反馈的滞回比较器

假设使用正、负电源(在实际应用中使用的是2.5 V的电压),比较器在应用中M3的栅极电压为一般基准电压,为了阐述的方便,令PMOS管M3的栅极接地。M1、M4、M12、M5和M13中的电流分别设为I1、I2、I3、I4和I5。当M2的栅极输入远低于0时,M2导通,M3截止,M1中的电流I1大部分被M2吸收,此时M7栅极为低电平,V1为高电平,经过M8和M9构成的反相器翻转后,Vout输出低电平。NMOS管M14和M11作为开关管,故此时M11截止,M14导通,M12和M13中均没有电流流过,即I3和I5均为0;随着M2的栅极输入电压Vin逐渐升高,I1一部分被M3吸收,量值为I4与I5之和,V1降低,Vout升高,M2中电流的一部分流过M12,量值为I2和I3之和;Vin继续升高重复上述正反馈过程,直至达到翻转点VTRP+时,M11导通,M14截止,M4中电流等于M5中电流。超过这一点时比较器才发生翻转。

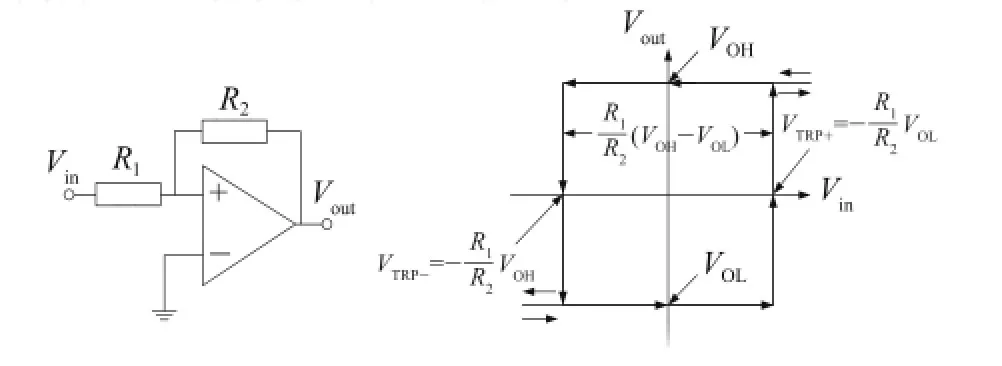

设定M1、M6和M10宽长比相等,M2和M3宽长比相等,M4、M5、M12和M13的宽长比相等。故Vin达到翻转点VTRP+时有:

I5=0(7)

由式(6)和式(7)可知,此时M2中电流为I2与I3之和,是M3中电流I4与I5之和的两倍。设定M2中电流为I+,M3中电流为I-,根据饱和区MOS管的I/V特性公式[4](忽略沟道调制效应):

VTRP+是正值。

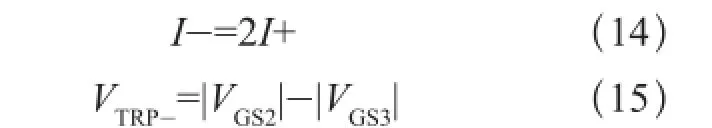

同理可计算负转折点,当Vin从高电平逐渐降低,当达到负转折点VTRP-时,有M11截止,M14导通,M5中的电流与M13和M4中的电流相同:

故此时

VTRP-是负值。

4 仿真分析

本文设计的电路采用0.18 μm CMOS工艺,用Hspice对电路进行仿真,两种典型的电源电压 2.5 V和1.8 V分别进行了直流仿真,偏置电流20 μA,设定M2和M3的宽长以期得到转折点压差为200 mV,VTRP+和VTRP-量值分别为100 mV和-100 mV的设计;在2.5 V电源电压下进行了交流分析、直流温度扫描和瞬态仿真。

直流传输曲线的仿真结果如图5所示:上半部分为电源电压2.5 V的直流仿真结果,两个转折点分别在0.9 V和1.1 V左右,下半部分为相同的电路结构在1.8 V电源电压下的直流仿真结果,转折点的电压同样在0.9 V和1.1 V,转折点电压差之间的误差在5 mV以内,滞回电压阈值的线性调整率为5 mV·V-1,所以本设计的滞回电压阈值对电源电压不敏感,可以工作在不同的电源电压之下。

图5 直流传输曲线的仿真结果

图6给出了本文设计的比较器交流仿真的幅频特性曲线。比较器常用在大信号的使用中,模型为一压控电压源,比较器的增益决定了比较器与理想比较器的接近程度。从图中可以看出,1~10 MHz的低频增益为81 dB,即增益在10 000以上,在10 MHz之后才开始衰减,接近理想的比较器。

图6 幅频特性的交流仿真结果

图7给出了比较器的温度特性仿真结果,0 ℃、25 ℃、45 ℃、85 ℃四种温度下的直流仿真结果显示最坏情况下转折点的偏移小于10 mV,即温度系数小于0.11 mV·℃-1,这是因为在转折点计算公式中涉及到PMOS晶体管的迁移率μ,而μ依T-2.20变化[5],故转折点电压因温度而变化,但是在比较器的应用中是可以接受的。

图7 温度特性仿真结果

图8给出了室温下比较器响应时间的仿真,比较器的输入激励和输出响应之间存在一个时延,成为比较器的传输时延,仿真结果显示在上升过程中从Vin/2到Vout/2的传输延时为12 ns;在下降过程中从Vout/2到Vin/2的传输延时为18 ns,响应速度比较高。

图8 响应时间仿真结果

5 结束语

本文设计了一种结构简单、响应速度快的滞回比较器,比较器采用PMOS差分对管作为输入管,有比较高的共模范围,在1.8 V~2.5 V的典型电源电压下,滞回阈值电压的线性调整率为5 mV·V-1,并且改变正反馈电路中M12和M13的参数就可以根据需要得到所需的滞回电压阈值,灵活性高。比较器的主体部分是二级开环比较器,增益高、响应速度快,室温下翻转过程中的传输延时为18 ns。

[1] Allen P E, Holberg D R. CMOS模拟集成电路设计[M].北京:电子工业出版社,2005. 379-385.

[2] J Millman, C C Halkias. Integrated Electronics: Analog and Digital Circuits and Systems [M]. New York: McGraw-Hill, 1972.

[3] A S Sedra, K C Smith. Microelectronics Circuits [M]. New York: Oxford University Press, 1998.

[4] 拉扎维. 模拟CMOS集成电路设计[M]. 西安:西安交通大学出版社,2002. 13-16.

[5] 施敏. 半导体器件物理[M]. 西安:西安交通大学出版社,2008. 21-23.

Design of a Hysteresis Comparator

XUE Tengfei1, ZHU Jiang2, QIAO Ming1

(1. State Key Laboratory of Electronic Thin Films and Integrated Device, University of Electronic Science and Technology of China, Chengdu 610054, China; 2. Liaoning Jinbang Electric Co., Ltd., Shenyang 110141, China)

Comparator is widely used in conversion of analog signal to digital signal. In analog-to-digital conversion, the input signal is sampled by comparator to determined the output digital signal. Hysteresis comparator also called sluggish comparator with superior anti noise ability plays an important role in comparator. The paper describes a hysteresis comparator with simple structure and hysteresis voltage threshold design flexibility. At the same time PMOS are the differential input transistors and the comparator has high common mode input range and large slew rate. The design with turning point of voltage difference 200 mV is simulated with 0.18 μm CMOS process and the results are accord with the desired outcome.

analog-to-digital conversion; anti noise ability; hysteresis comparator

TN402

A

1681-1070(2015)03-0026-03

薛腾飞(1989—),男,河北邢台人,硕士研究生,主要研究方向为模拟集成电路设计。

2015-01-12