基于PowerPC8640处理器的通用处理模块设计

张伟栋,赵 红(.中国航空计算技术研究所,陕西 西安 70065;.西安火车站,陕西 西安 7004)

基于PowerPC8640处理器的通用处理模块设计

张伟栋1,赵红2

(1.中国航空计算技术研究所,陕西 西安 710065;2.西安火车站,陕西西安710014)

随着新一代飞机机载电子设备综合化、智能化的发展,系统对机载电子设备的处理能力需求越来越高。借鉴国外高性能嵌入式计算机的设计原则,设计了一种基于高性能处理器PowerPC8640的通用处理模块,并对部分功能单元的设计进行描述。该模块具有数据处理能力强、功能扩展性强、通用性强、集成度高、高速外部串行总线接口等特点,具有较高的应用价值,目前该模块已经应用于多种机载电子设备中。

PowerPC8640;通用处理;嵌入式处理;ASAAC结构

0 引言

随着新一代战机的出现和战技指标需求的不断攀升,机载航电设备作为航空电子产品中的重要一员,其功能和性能也要得到不断的完善和提高,同时体积和重量却要求不断减小,以满足战机的作战需求。功能的完备和性能的提高带来了大量数据的处理需求,需要高性能的处理器完成相关的任务,体积和重量的减少要求产品上的器件密度越来越高。本文主要介绍基于 Power-PC8640处理器的高性能高集成度的通用处理模块的设计,它采用通用化设计思想、标准的ASAAC结构以及可配置性的设计,可用于多种机载电子系统[1]。

1 系统概述

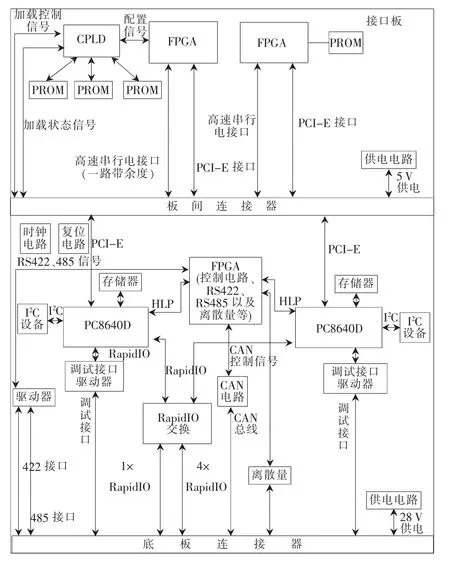

本文所描述的通用处理模块是基于 PowerPC8640高性能处理器,设计采用两片 PowerPC8640,周边配置有存储器(包括DDR2、Flash和NvRAM)、看门狗、高速Rapid IO接口、高速串行接口、CAN总线、离散量接口、422接口、485接口、温度监控、RTC和调试接口等资源。模块设计采用两块印制板,其结构图如图1所示。

2 模块平台介绍

2.1PowerPC8640处理器简介

PC8640属于 PowerPC的处理器,目前已在国外数据处理与信号处理中采用。一片PC8640中提供1个e600内核,主频最高可达1.25 GHz,e600内核提供1 MB的高带宽、低延迟的L2 cache,设计中主频设为1 GHz。

图1 通用处理模块结构图

PC8640有两个64位的 DDR2控制器接口,最高工作频率533 MHz。PC8640处理器使用e600核和高速内部互连技术来平衡处理器的性能与I/O系统的吞吐率。

PC8640配置了两种灵活的高性能 I/O接口。一种是×1、×2、×4、×8 PCI Express接口,采用 PCI-E总线实现板级高性能设备的串行点对点互连;另一种是1×、4×线串行 Rapid IO接口,由于 Rapid IO总线具有软件开销小、配置简单、硬件纠错等特点,且支持存储器映射和包传输机制,非常适合作为底板接口。

PC8640还配置了4个以太网控制器,支持10 Mb/s,100 Mb/s和1 000 Mb/s速率通信。每个以太网控制器可以转换为FIFO模式实现高效ASIC互连。

此外 PC8640还配置有 UART接口、中断控制器、DMA控制器、GPIO等资源[2]。

设计采用两片PC8640处理器,每片处理器的存储器资源、调试接口、温度检测、RTC资源独立,其他资源如离散量、422接口、485接口等资源是共用的。

2.2其他资源设计

模块的存储器包括 DDR2存储器、Flash存储器和NvRAM存储器。PC8640对外提供DDR2接口和HLP总线接口。PC8640的DDR2接口外接64位数据宽度的1 GB 的DDR2 SDRAM;PC8640的HLP总线接口外接Flash和NvRAM。

PC8640对外提供两路I2C总线,分别连接实时时钟和温度监测芯片,提供RTC和温度监测功能。

PC8640对外提供调试接口,包括串口、以太网接口和JTAG接口,用于处理器以及软件的调试。

处理器 PC8640集成两个高速串行I/O接口(Serdes1 和Serdes2),设计中将每个处理器的两个Serdes接口设置为×4 PCI-E模式和×4 Rapid IO模块。Serdes1接口连接处理器和高速串行接口,用于实现高速串行接口通信控制,接口为 PCI-E总线;Serdes2接口连接处理器和Rapid IO交换芯片,接口为RapidIO总线。Rapid IO交换芯片配置为 3个 4×Rapid IO接口,10个 1×Rapid IO接口。4×Rapid IO接口其中 2路接处理器,1路引到底板;1× Rapid IO接口10路引到底板上。

高速串行接口实现2路,其中一路协议处理采用固定的逻辑版本;另外一路协议处理根据系统应用需要,可通过处理器控制加载不同的逻辑版本。两路高速串行接口的传输介质为光接口,通过光电转换芯片连接到底板连接器。

422、485接口采用IP核在FPGA内部实现,处理器通用HLP总线控制422、485接口的收发数据。

模块对外提供5路CAN总线接口,采用协议芯片实现,CAN总线接口挂在处理器控制FPGA下,接口采用SPI接口。

模块对外提供多路差分的TTL输入输出信号、多路LVDS输入输出信号、多路LVTTL输入输出信号、多路MLVDS输出信号以及多路Aurora总线接口。

底板连接器为带光纤接口的数字连接器,A腔包含2芯光纤接口和135芯低频接触件,B腔包含252芯低频接触件。

3 设计要点

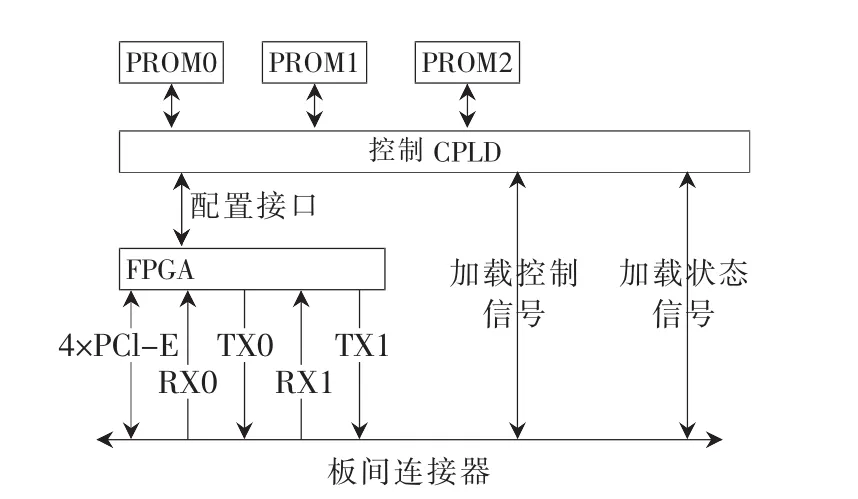

3.1高速接口重加载设计

由于本文设计的是通用处理模块,高速串行接口也要适应多种机载电子设备,不同设备的配置共包括:2路高速串行接口、1路双余度的高速串行接口、1路单余度的高速串行接口等。高速串行接口的逻辑规模很大,因此将高速串行接口设计为2路,一路可重加载,另一路为固定的逻辑。下面说明高速串行接口重加载的设计实现。

加载控制电路的设计框图如图2所示。

图2 加载控制电路

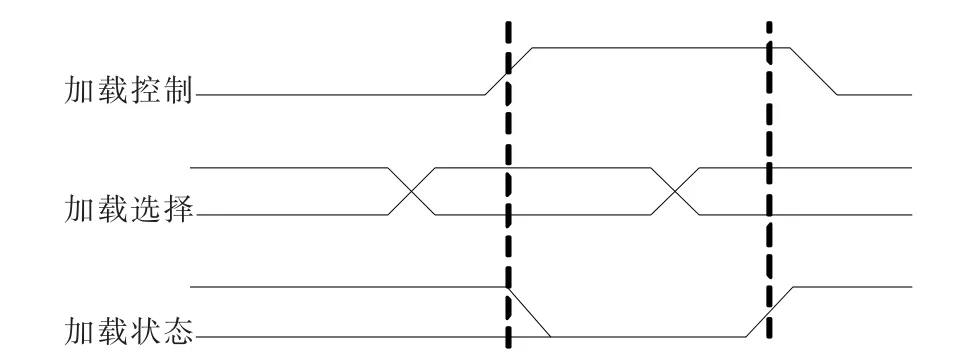

加载控制、状态信号采用3.3 V电压,通过处理板FPGA控制,输出给CPLD,实现对逻辑重加载的控制。加载控制信号通过3个控制离散量分别表示3个不同逻辑状态,通过一个控制信号指示逻辑重载开始,通过处理器控制。加载控制时序如图3所示。

图3 加载控制时序图

加载及控制流程说明如下:

(1)处理器的控制FPGA和CPLD中,重加载设计默认状态都为001,CPLD上电后固定加载PROM0中的逻辑;

(2)处理器启动后,根据系统要求,首先判断加载的默认状态高速串行接口逻辑是否为系统所需要的,如果是,则处理器不再发起重加载,如果不是,则先设置加载控制离散量状态(每位设置为“1”,表示加载对应位的PROM中的逻辑;为“0”,表示不加载),然后将加载控制离散量置位为“1”,启动加载,此时处理器软件检测逻辑加载状态信号,在该信号为“1”后,表示加载完成,可对设备进行初始化;

(3)CPLD在加载控制信号的上升沿启动加载,通过控制FPGA的Program_B信号控制逻辑重载[3];

(4)CPLD在完成逻辑加载后 (判断 FPGA给出的Done信号为“1”),处理器发起逻辑复位操作,在复位结束后,将加载完成状态离散量置位为“1”;

(5)处理器软件在判断逻辑加载完成,将加载控制信号重新置位为“0”,以便于下次可用于逻辑重载。

3.2软件设计

由于设计的是通用处理模块,在软件方面也需要满足多种机载电子设备的要求。处理器、存储器资源、接口资源在不同设备中是相同的,软件也完全相同。而高速串行接口在不同的设备中有不同的需求,驱动不同,因此在软件设计时,考虑到多种设备中使用同一款软件,需将不同的高速串行接口驱动固化在 Flash的不同地址,根据系统设备需求,加载相应的软件驱动,具体实现如下:模块加电后,处理器需到 Flash取指令,初始化模块,引导运行操作系统以及应用程序。因此在模块初始化完成后,设置选项,通过不同的参数选择不同软件驱动,以适应不同设备的需求。如参数设置为0,模块操作系统启动后,加载第一种设备的高速串行接口驱动以及其他驱动,这样应用程序启动后可直接调用相关的驱动函数。如果参数设置为1,模块操作系统启动后,加载第二种设备的高速串行接口驱动以及其他驱动,参数设置为2,加载第三种设备的高速串行接口驱动以及其他驱动。该参数固定在Flash中,不会随着模块下电而消失,用户只需要设置一次,下次模块上电后,会根据已经设置好的参数加载相应驱动,如需改用其他设备,只需要修改一次参数即可。

4 结论

本文结合高性能的 PowerPC8640处理器的特征,设计了一种双处理器的通用处理模块,对外提供高速串行接口、CAN总线、Rapid IO总线、422接口、485接口、多种形式的离散量接口以及处理器的调试接口,高速串行接口可适用于多种电子设备。该模块设计的目的是为了满足新一代飞机多种机载设备的需要,与系统中其他设备进一步综合,使机载设备整体性能达到最优,该模块具有很大的应用价值。

[1]汤艳飞,文敏华.基于MPC8640D处理系统的技术研究[J].航空计算技术,2012,42(1):120-122.

[2]FreescaleSemiconductor,Inc.MPC8640DRM [EB/OL].(2008-07-xx)[2014-10-31].http://www.freescale.com.

[3]Xilinx,Inc.Virtex-5 FPGA Data Sheet[EB/OL].(2008-07-xx)[2014-10-31].http://www.xilinx.com.

The design of general processing module based on pow erPC8640

Zhang Weidong1,Zhao Hong2

(1.Aeronautic Computing Technique Research Institute,Xi′an 710065,China;2.Xi′an Railway Station,Xi′an 710014,China)

With the development of the integrated and intelligent new airborne electronic equipment,system demands higher processing capacity.Referring to the design principle of high performance embedded computer abroad,a general processing module of high performance processor based on PowerPC8640 has been designed,and the design of part functional unit are described.This module has strong processing scalability,versatility,high integration and high speed external serial bus interface,and has high application value.The module has been applied to a variety of airborne electronic equipment.

PowerPC8640;general process;embedded computer;ASAAC

TP336

A

1674-7720(2015)06-0032-03

2014-11-27)

张伟栋(1984-),男,硕士研究生,工程师,主要研究方向:数据处理技术。