Cortex-M4ARM 处理器的USB2.0主机系统设计

王静娇,翟刚毅,杨阳,刘剑

(中国船舶重工集团公司 第七二四研究所 信号系统部,南京211153)

王静娇(助理工程师),研究方向为数据通信;翟刚毅(高级工程师),研究方向为雷达数字信号处理;杨阳(助理工程师),研究方向为数据通信电路设计;刘剑(工程师),主要从事雷达数字电路板设计。

引 言

低功耗、低成本、外围接口丰富、使用简单的ARM 处理器,在电子模块的故障检测、监控和辅助功能中的应用越来越广泛。与ARM 接口的USB外设(如USB下载电缆、无线通信模块、人机交互模块等)的应用也越来越多,这些外设往往不提供针对ARM 的主机驱动程序,需要用户自行开发。

本文以TI公司基于ARM Cortex-M4内核的TM4C129 XNCZAD 为 核 心 构 建 了USB2.0 主 机 系 统,实 现 了 与USB2.0设备的高速数据交互。

1 基于ULPI接口的USB2.0硬件设计

图1为系统硬件结构框图,其中核心处理器为TI公司的TM4C129XNCZAD,工作时钟可达120 MHz,提供150DMIPS的性能,具有1024KB Flash和256KB 单循环系统SRAM,支持UART、I2C、CAN、以太网、USB等通信接口并具有丰富的GPIO 口[1],完全满足USB2.0主机开发需求。USB 外置PHY 芯片为SMSC 公司的USB3320,支持高速、全速、低速3种USB通信模式。

图1 系统硬件结构框图

1.1 ARM 处理器USB模块

TM4C129XNCZAD 的USB 控制器支持USB 主机、设备、OTG 三种点对点USB通信,符合USB2.0标准,支持控制、批量、等时、中断4种传输模式。图2所示为该芯片的USB模块结构框图,该模块具有16个端口,1对控制端口和7对输入/输出端口;4KB专用端口内存,端口通道均可以进行DMA 传输,DMA 控制器可直接访问FIFO,而无需通过CPU 接口。

另外,芯片内置USB PHY,并设有ULPI接口,可以通过USBPC.ULPIEN 进行设置选择。默认使用USB内置PHY,但仅支持全速或低速通信,通过USB0DM 和USB0DP连接USB电缆。若设置USBPC.ULPIEN 为1,则使能ULPI接口,连接外部USB PHY 和USB控制器,从而扩展为USB2.0。

1.2 基于ULPI协议的USB2.0设计

TM4C129XNCZAD处理器中USB模块内部的PHY为USB1.1,为了满足高速USB 传输需求,采用ARM 芯片上预留的ULPI接口外接PHY 芯片,从USB1.1全速传输升级为USB2.0 高速传输,本文采用SMSC 公司的USB3320作为ULPI PHY 芯片。

图2 TM4C129XNCZAD处理器USB模块结构框图

ULPI(UTMI Low Pin Interface)是低引脚UTMI的简称,UTMI(USB2.0 Transceiver Macrocell Interface)为USB2.0的传输宏接口。UTMI PHY 主要通过一系列的控制信号来实现与作为LINK的USB控制器之间的交互,而ULPI将UTMI接口的信号线从32条减少至12条。ARM处理器和PHY 结合成为USB2.0的主机端,需要把PHY也配置为host主机模式,具体电路如图3所示。ARM 处理器提供了ULPI接口,若ARM 配置为ULPI模式,则ULPI clk引脚能提供60MHz时钟输出给PHY芯片。

图3 USB模块硬件连接图

2 USB2.0主机软件开发

软件的工作流程为:ARM 处理器首先进行系统初始化,包括对USB模块的初始化(即ULPI接口配置等),然后等待USB主控制器的外部中断,当USB设备连接主机后,由USB主控制器通过外部中断信号通知ARM 处理器,ARM 处理器与USB主控制器完成设备的枚举、配置,并开始USB数据传输[2]。

2.1 ULPI接口配置

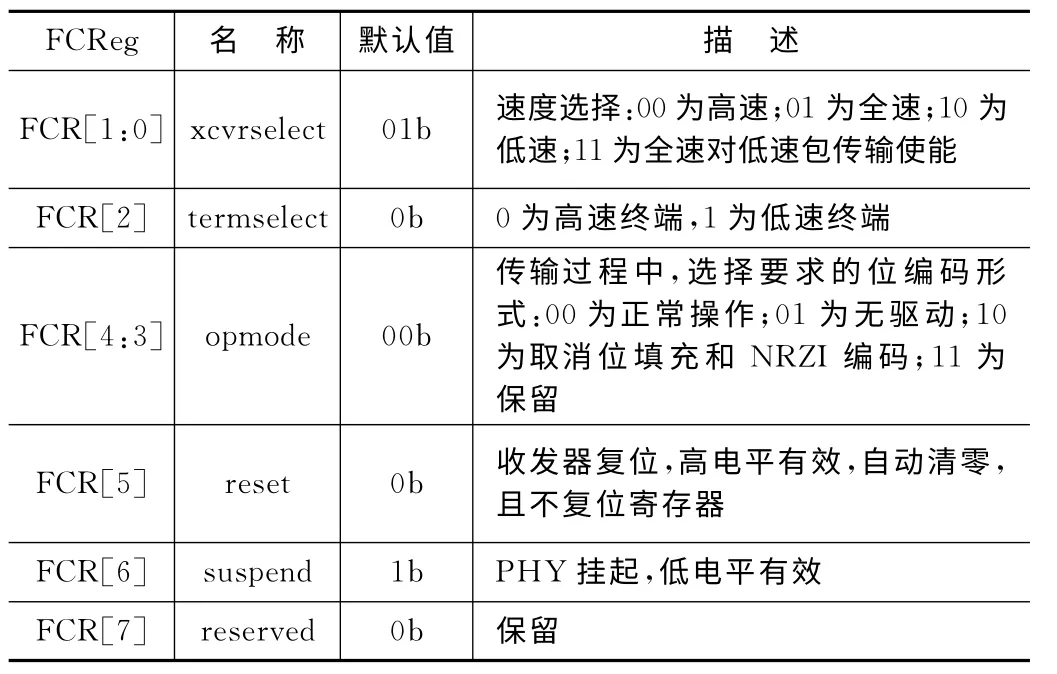

首先,USBULPIEnable()函数使能ARM 处理器的ULPI接口。ULPI接口的工作模式分为同步模式、低功耗模式、6/3引脚FS/LS串行模式、Carkit模式[3],通过USBULPIConfig()函数配置PHY 芯片的寄存器,可以使其工作在对应模式下。本文中USB3320主要工作在同步模式下。ULPI提供了24 个寄存器,其中功能控制寄存器(Function Control Reg,FCR)用于实现对PHY 端UTMI功能的基本配置。FCR占用地址0x04h~0x06h,0x04h地址可读可写,而0x05h和0x06h地址实质并不存在,只是分别实现了对寄存器相应位的置位和清0 操作。函数USBULPIRegRead()和USBULPIRegWrite()分别实现了寄存器的读写,具体功能控制寄存器位的描述如表1 所列。FCReg的初始值为0x41h,本文中PHY芯片工作在USB2.0高速模式、正常操作状态,所以将其设置为0x40h。

同步模式中ULPI定义了由LINK 端(ARM)发出的发送命令字TX CMD 和PHY 端发出的接收命令字RX CMD。一个TX CMD为一个字节,包括2位的命令码和6位的命令负载码,ARM 处理器需等到DIR 信号为低电平时才能发送TX CMD,后接需要传输的数据,寄存器的读写就是通过发送TX CMD 来实现的。而RX CMD 体现了线上状态(Linestate)、连接、OTG 状态信息等,它传达给ARM USB接收信息和中断事件两种信息。USB接收信息即一次USB传输后,PHY 要发送带Linestate内容的RX CMD来表示EOP(End Of Packet);中断事件则包括Hostdisconnect、vbus、IdGnd等,当检测到这些事件时,PHY 芯片就会发送RX CMD给LINK 端。

表1 功能控制器位描述

2.2 USB2.0主机驱动开发

USB主机模式主要涉及USB驱动初始化、USB设备枚举、USB数据传输过程。

(1)USB驱动初始化

进行USB驱动初始化,在USB_Init()函数中先配置USB模块的引脚,包括ULPI接口引脚类型等,接着使能USB模块,并通过USBStackModeSet()将其设置为主机模式,注册主机类驱动,打开类驱动实例[4],然后初始化USB控制器,并使能USB中断。ARM 的USB模块初始化成功后,使能ULPI接口,并复位USB3320设备,对其进行配置。

(2)USB设备枚举

ARM 作为USB的主机端,需要周期性地调用USBHCDMain()监听USB设备状态。当USB设备通过PHY芯片连接上ARM 处理器后,PHY 发送RXD CMD,从而产生连接中断事件通知ARM 处理器;ARM 处理器调用枚举驱动对USB设备进行枚举:先复位设备,接着检测设备运行在低速、全速还是高速模式,再获取USB设备描述符并重新分配地址,然后获取配置、字符串描述符等,最后为设备驱动程序选择配置。

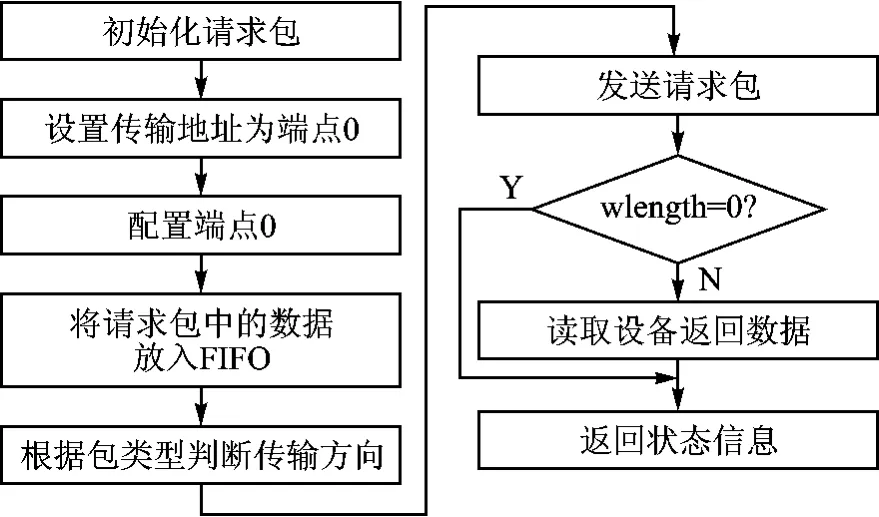

USB设备的枚举主要是主机通过控制传输来实现,每个设备都支持通过端点0管道完成控制传输。控制传输使主机和设备之间能够交换有关设备能力和类似厂商专有的信息,包括设置阶段、数据阶段(可无)、状态阶段。设置阶段由一个设置事务构成,将整个传输确定为控制传输,并发送设备请求及设备完成请求所需的其他信息。一个设置请求包含bmRequestType(1字节)、bRequest(1字节)、wValue(2字节)、wIndex(2字节)、wLength(2字节),共5个字段、8个字节,用于指示设备请求类别以及是否具有数据阶段,具体由USBHCDControlTransfer()函数实现,流程如图4所示。

图4 控制传输流程图

(3)USB数据传输

批量传输可以发送大量数据而不阻塞总线,FPGA 调试主要涉及到比特流和捕捉的数据,适合采用批量传输。批量传输由一个或多个IN 或OUT事务构成,分为批量读数据bulkIn和批量写数据bulkOut。所有的总线传输都是传到设备端口或者从设备端口发送,端口和主机控制器之间需要建立管道来进行数据传输,这里分别通过IN 和OUT 端口,在枚举期间也需要分别对每个端口建立管道。函数USBbulkIn()通过读取通向IN端口的管道进行读操作,函数USBbulkOut()则通过OUT端口的管道进行写操作,USBbulkOut()函数的实现流程如图5所示,USBbulkIn()函 数类似。

图5 批量读流程图

结 语

本文通过外接USB PHY 扩展了TM4C129XNCZAD芯片的USB模块,并通过编写USB核心驱动程序实现了USB2.0 设备的枚举、数据传输,完成了基于ARM 的USB2.0的主机开发。本系统应用在FPGA 远程调试中,可以实现FPGA 下载电缆在ARM 上的枚举、数据14 传输等功能,成功地进行FPGA 的加载和调试,并可以广泛应用于其他USB设备的连接。

[1]Texas Instruments Incorporated.Tiva TM4C129XNCZAD Microcontroller Data Sheet,2013:58-61.

[2]Jan Axelson.USB开发大全[M].李鸿鹏,译.北京:人民邮电大学出版社,2011.

[3]郑拓.USB2.0主机端(ULPI)的FPGA 设计[D].太原:太原理工大学,2011.

[4]李纪伟.基于ARM 的嵌入式系统研究及USB驱动程序设计[D].成都:电子科技大学,2005.