基于FPGA的数字频率计设计

荆科科

【摘 要】设计是以FPGA为处理模块,以VHDL做为描述语言。20MHz的晶振做为主时钟,外部两个按键分别是使能按键和复位按键,便于进行人工控制。该设计通过直接测量的方法对被测信号的频率进行检测并显示。详细介绍了系统的各个设计模块,并对调试过程进行说明。该设计可以做成便携式手持设备用于测量手机中的实时时钟信号频率,还可以对音频信号的频率进行检测。

【关键词】FPGA;频率计;VHDL;模块设计;元件例化

0 引言

频率计是根据其应用来设计的。频率计数器最常见的应用是确定发射机和接收机的特性。发射机的频率必须进行检验和校准,才能符合有关规章制度的要求。频率计数器能对输出频率和一些关键的内部频率点(如本振)进行测量,查明无线电发射时候是否满足技术指标。

频率计数器的另一些应用包括计算机领域,在此领域中的数据通信、微处理器和显示器中都使用了高性能时钟。对性能要求不高的应用领域包括对机电产品进行测量。本设计采用FPGA作为控制核心,利用直接测量法对被测信号的频率进行测量显示。

1 设计要求

1)设计4位十进制数字显示的频率计,其频率测量范围为10k—9999kHz;

2)要求量程能够自动转换;

3)当输入的信号小于10kHz时,输出显示全0;当输入的信号大于9999kHz时,输出显示全F。

2 设计原理

本设计利用直接测量法进行测量计算,用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率,也就是周期性的被测信号在单位时间内变化的次数。

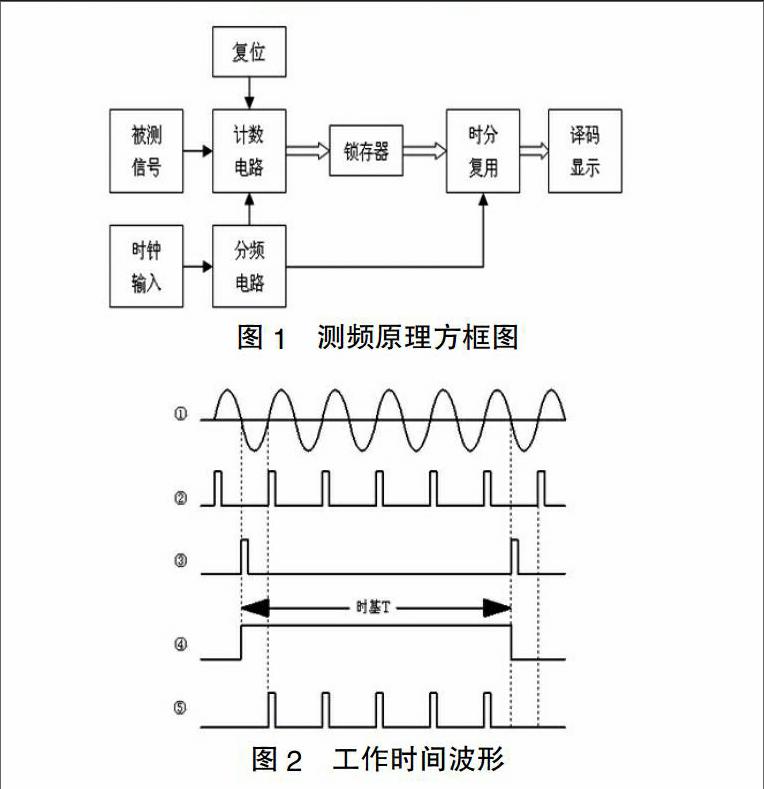

计数器是严格按照f=N/T的定义进行测频,其对应的测频原理方框图如图1所示。工作时间波形如图2所示。

频率计的系统主要由被测信号、计数器电路、锁存器电路、时分复用、译码显示、时钟输入和分频电路组成

2.1 整体设计思路

本设计以频率为20MHz的晶振作为主时钟,在设计中,需要用到的信号有频率为5Hz的闸门信号,25Hz的按键消抖延时信号以及200Hz的数码管动态显示扫描信号;这三种信号由分频器产生。分频器产生的5Hz频率的信号传输到计数器,计数器对闸门信号进行分析,在高电平期间计数器对被测信号的周期进行计数,当闸门信号为低电平时停止计数,将记录的数据传输到锁存器。锁存器对数据锁存后,计数器即可清零,为下一次计数做好准备。锁存器再将本次记录的数据传输到显示模块,显示模块对待显示数据进行译码后输出到数码管进行显示。计数器在正常工作状态下,不断记录新数据,最终传输到显示模块,使频率计实时更新数据。现将每个模块的设计原理介绍如下。

2.2 计数器的设计

计数器的功能主要是在基准时间内对被测信号的周期进行计数如图3所示。

其中enable是使能信号,高电平有效。cp3是闸门信号;input是被测信号;reset是复位信号,低电平有效;play0~play3是4位BCD显示输出,用于显示0~9的数值;decimal是小数点输出位。

使能信号enable由外部按键控制,当为高电平时计数器开始对被测信号进行测量;复位信号reset同样由外部按键控制,当输入低电平时系统复位;闸门信号cp3由经硬件描述语言编写的分频器对外部20M晶振进行分频产生,cp3是周期为0.2s的方波信号;计数器正常工作时,当检测到外部有被测信号input输入时启动计数功能;在闸门信号cp3的高电平时段内即0.1s对被测信号计数。计数器内部含有数据存储单元play0~play3,将单位时间内检测到的被测信号频率进行记录保存,待传入显示模块。除了以上信号外,计数模块还包含两个溢出标志信号overflow和low,当被测信号的频率小于10kHz或大于9999kHz时,频率计显示全“0”或全“F”。

2.3 锁存器的设计

该部分电路用于对计数器的数据进行锁存,保证计数模块的数值能正确的输出进行显示。本模块内部包含一个进程语句,敏感信号为闸门信号cp3和复位信号reset。当语句检测到闸门信号cp3出现下降沿时,锁存器将由计数器传输过来的信号进行锁存,从而释放计数器,使计数器能够进行下一轮的计数,实现数据的实时更新。锁存器的方块图如图4所示。

2.4 分频器的设计

该模块中输入端口cp_20m为20MHz外部晶振输入端,分频器利用硬件描述语言对晶振信号进行分频,最终输出3个不同频率的信号,即cp1、cp2和cp3。在进行硬件描述时,先对晶振的20MHz信号进行50000分频产生内部信号cp(频率为400Hz的信号)。信号cp1为cp的2分频输出频率为200Hz用于动态扫描显示的时基信号;信号cp2为cp1的8分频输出频率为25Hz,用于按键的消抖;信号cp3为cp1的40分频输出频率为5Hz,即形成一个0.1S的闸门时间,做为计数器的闸门信号等。分频器方块图如图5所示。

2.5 显示电路的设计

该模块是描述动态扫描数码管显示代码。其中cp1是一个200Hz的扫描频率。p0,p1,p2,p3是从锁存器传输过来的4个待显示十进制数,信号show为送入到数码管的输出字形码信号,sel为数码管的位选信号。low和overflow为两个溢出状态标志信号。在代码中利用cp1的上升沿触发进程语句,进程语句中先判断位选信号该显示哪一位;例如显示第一位时,对位选信号赋值sel<=“0001”,然后对第一位数据p0进行译码,输出到数码管的字形端进行显示,以此类推,每5ms(cp1为200Hz)显示一位数据,四位数据循环显示使数码管稳定显示数据。

2.6 顶层文件的设计

顶层文件的设计可以先用原理图输入法,对各个模块进行正确连线,待调试无误后,再根据原理图输入法,采用元件例化的方法对顶层文件进行描述。顶层原理图如图6所示。

3 调试技巧

在调试过程中以各个模块为单位,编好代码后先进性波形图仿真,对各个模块的波形图进行分析,如存在问题及时对代码进行分析修改;若波形图不存在问题再进行整体电路的描述设计。若直接进行整体设计再分析的话,很难判断错误出现的位置,导致设计效率的降低。另外在对计数模块进行波形仿真时,建议先将起初的50000分频适当修改为500分频,并在设置被测信号的频率时也相应的降低频率。若不进行修改,在进行波形仿真时,软件要仿真运算很长时间,同样会降低效率。当对计数模块的波形分析无误后再改回原代码的50000分频既可。

4 硬件配置

本设计的硬件测试是基于GW48系列SOPC/EDA实验开发系统现代DSP实验开发系统,该设备的显示模块采用动态扫描时,其数码管的硬件引脚配置如图7所示。

数码管的字形码分别对应管脚:a:173;b:169;c:168;d:167;e:166;f:165;g:164;h:163四位数码管的位选端分别对应管脚:个位:162;十位:161;百位:160;千位:159。

【参考文献】

[1]谭会生.EDA技术及应用实践[M].2版.湖南大学出版社,2010.

[2]潘松,黄继业.EDA技术实用教程[M]..3版.科学出版社,2006.

[3]潘松,黄继业.EDA技术实用教程——VHDL[M].4版.科学出版社,2010.

[责任编辑:邓丽丽]