宇航用静态随机存储器验证方法研究与应用

肖爱斌,王斐尧,王文炎,隽 扬,张雷浩,张皓源(. 中国空间技术研究院,北京 00094;.中国电子科技集团公司第58研究所,江苏 无锡 4035)

宇航用静态随机存储器验证方法研究与应用

肖爱斌1,王斐尧1,王文炎1,隽 扬2,张雷浩1,张皓源1

(1. 中国空间技术研究院,北京 100094;

2.中国电子科技集团公司第58研究所,江苏 无锡 214035)

摘 要:在研究静态随机存储器故障模型以及常用功能验证方法的基础上,提出采用March SOF算法结合故障注入的EDAC测试程序作为宇航用带EDAC功能SRAM存储器的验证方法。该方法将March SOF算法扩展为32位字定向算法,同时增加数据保持故障以及EDAC功能的测试,可以对宇航用SRAM进行全方位功能验证。采用实际电路,对该方法进行实现和验证,验证结果表明了方法的可行性和有效性。

关键词:静态随机存储器SRAM;错误检测与纠正EDAC;功能验证;March算法

1 引言

受宇宙空间中辐射的影响,航天器上的静态随机存储器(Static Random Access Memory,SRAM)可能会发生单粒子翻转效应(Signal Event Upset,SEU)。SEU可能会造成存储器某一位的数据从一个稳态变化到另一个稳态,而存储器的数据变化又会使星载计算机系统的指令或是数据出错,严重时可能导致整个星载计算机系统的崩溃。因此需要寻找一种办法来纠错或是容错[1]。实现星载计算机SRAM容错或纠错的办法有很多,采用带EDAC功能的SRAM存储器是最直接的办法。

随着工艺尺寸的不断缩小,存储容量的不断扩大,SRAM存储器的测试复杂度越来越大,为提供合格的存储器产品,必须针对各种电路故障,优化测试向量,提高产品的测试覆盖率。本文通过考虑SRAM存储器的故障模型,采用March SOF算法结合故障注入的EDAC专用测试程序作为带EDAC功能SRAM的测试方法。将March SOF算法扩展为32位字定向算法,字定向的March SOF算法对SRAM的常见故障模型有比较高的覆盖率,结合故障注入的EDAC专用测试程序,可以对带EDAC功能的SRAM进行全方位功能验证。

2 SRAM存储器故障模型

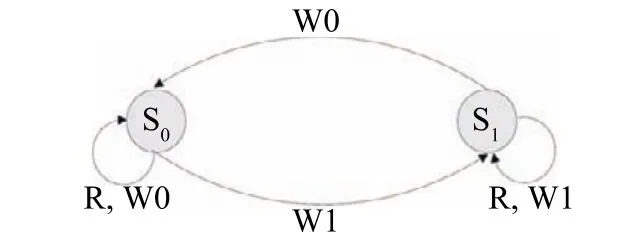

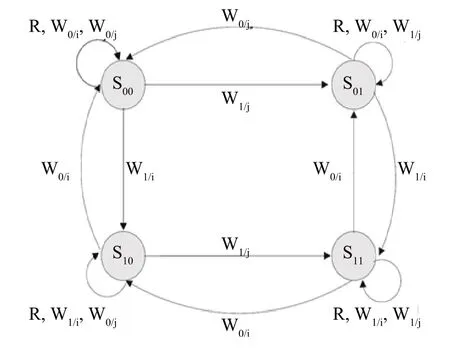

SRAM的故障模型[2~4]包括固定故障、转换故障、耦合故障、地址译码故障、读破坏故障、错误写通故障、数据保持故障等。每种故障均可通过一些特定的测试程序来进行检测。正常存储单元工作状态如图1所示。

图1 正常存储单元工作状态

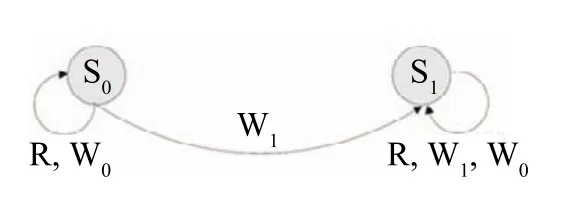

固定故障如图2所示,一般由制造缺陷引入,表现形式为单元或连线的逻辑值总为某个固定值,不随着输入的变化而变化。

转换故障如图3所示,一般由于单元的比率设计不合理导致,这样在读写操作发生时,单元会发生不可控制的翻转,导致读写错误。检测这两种类型的故障,只需要分别执行数次相反的写和读操作(写0 读0,写1读1),即可以根据写读结果一致性判断电路相关部分是否存在故障。

图2 存储单元固定0/1故障示意图

图3 存储单元转换故障示意图

在存储阵列中存储单元不是孤立存在的,由于寄生电容、电阻等的影响,对单元的读写操作,有时也会影响到邻近的单元存储值的变化,这就是所谓的耦合故障,如图5所示。通常是由于工艺参数不稳定,导致存储单元的管子阈值电压发生变化引起的。针对这种类型的故障,可以对地址进行多次不同的读写,然后比较每次读写数据的差异。

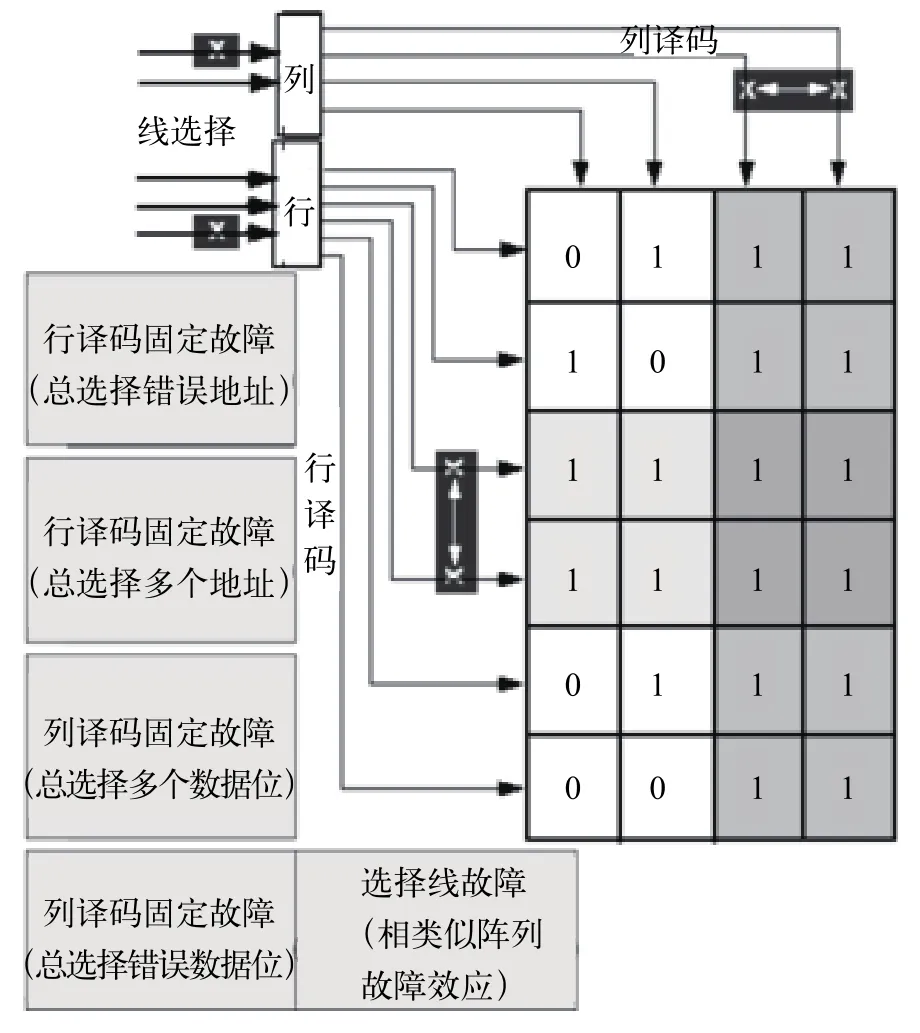

译码选择故障分为行译码固定故障、列译码固定故障、选择线故障。行/列译码固定故障会引入行地址选择错误,如总选择单个行故障或总选择多行故障。

这类故障主要是在制造过程中出现开路或短路造成的。它的表现形式大多是固定故障形式,故检测方法与固定故障的相类似,分别执行数次相反的写和读操作(写0读0,写1读1),根据写读结果一致性判断电路相关部分是否存在故障。

图4 正常存储单元的写读操作示意图

图5 存储单元耦合故障示意图

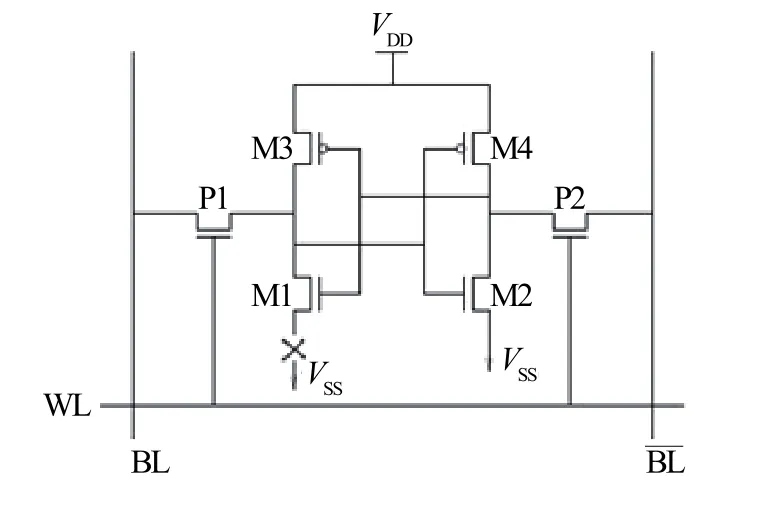

存储器具有读保持的功能,即在读操作过程中,存储单元内的数据是保持不变的,但如果制造过程中存在缺陷,会使存储器单元的数据在读过程中发生翻转,丢失了原来保存的数据,发生读破坏故障。

如图7所示,当执行读操作时,位线BL上的电荷会通过P1和M1放电,但若M1的源端没有与地相连,此时读操作会将节点A上的数据冲掉(由0变1)。该类故障的检测比较简单,只需对发生故障的单元进行一次写后,再执行多次读操作,会发现每次读出的数据都在变化,如此即可检测是否存在故障。

图6 地址译码故障示意图

图7 读破坏故障示意图

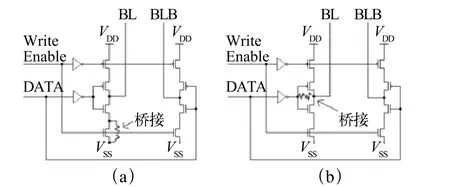

错误写通故障发生在写控制电路的数据输入端与位线之间相连的地方,一般是写控制电路出现桥接,致使数据输入端直接与位线相连通,如图8所示,最终导致整条位线上的读操作发生故障。这种故障会使整列单元的读操作失效,故检测时按列遍历执行先写后读即可。

图8 错误写通故障的两种类型

数据保持故障是电路制造过程中产生的寄生电阻、电容等致使存储单元发生异常,在待机模式下,存储单元不能保持原有数据的一类故障。要检测这类故障,需要在测试中引入一段等待时间。这段时间内存储器片选无效,不做任何操作,随后使片选有效,读取单元数据,比较进入待机模式前写入数据与读出数据的一致性就能判断是否发生该类故障。

3 SRAM存储器验证方法分析

在存储器测试方面,考虑到大容量存储器的测试时间较长,因此需要选择既能覆盖故障又能不太费机时的测试方法。目前在存储器测试技术上有全0全1测试、正反棋盘格测试、March测试等多种算法。

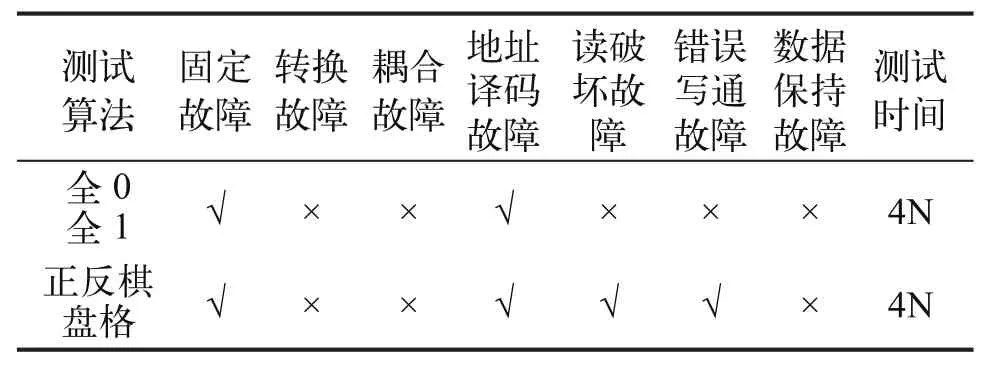

全0全1测试算法对行列中的每一位存储单元进行全0和全1的写入读出操作,可以完成存储单元固定故障和部分地址译码故障的检测。此算法测试时间比较短,能很快检测存储器的功能,但是故障覆盖率很低。

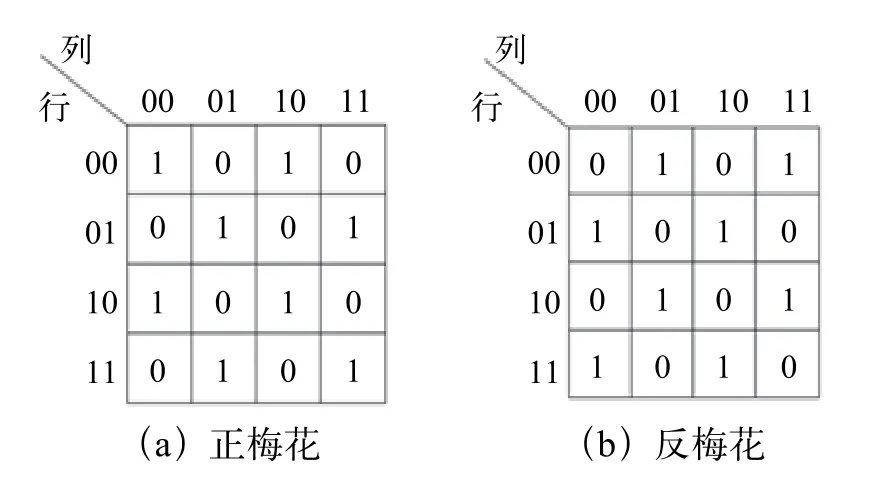

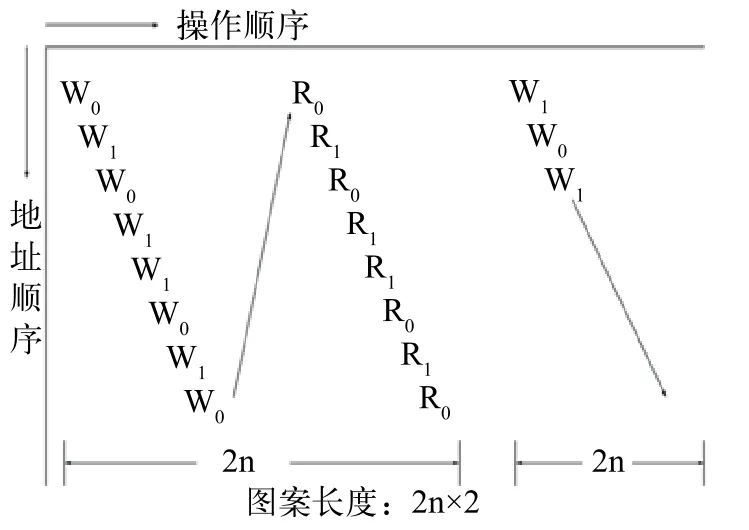

正反棋盘格测试算法与全0全1算法类似,不同的是它对行列中的每一位存储单元进行正反棋盘格写入读出操作,所以它不仅能快速检测存储器的固定故障,还能检测地址译码故障和读写故障。由于只是写入数据不同,故该算法的测试时间与全0全1测试算法相同。棋盘格的测试图形如图9所示,操作顺序见图10。

图9 正反棋盘格测试

图10 棋盘图案法的操作顺序

两种测试算法的比较结果见表1,正反棋盘格测试算法在故障覆盖率上要远胜于全0全1测试算法。

因此在测试时,如果只想大致了解存储器的情况,快速排除一些常见故障(固定故障),正反棋盘格测试算法相对较好。

表1 两种测试算法的比较

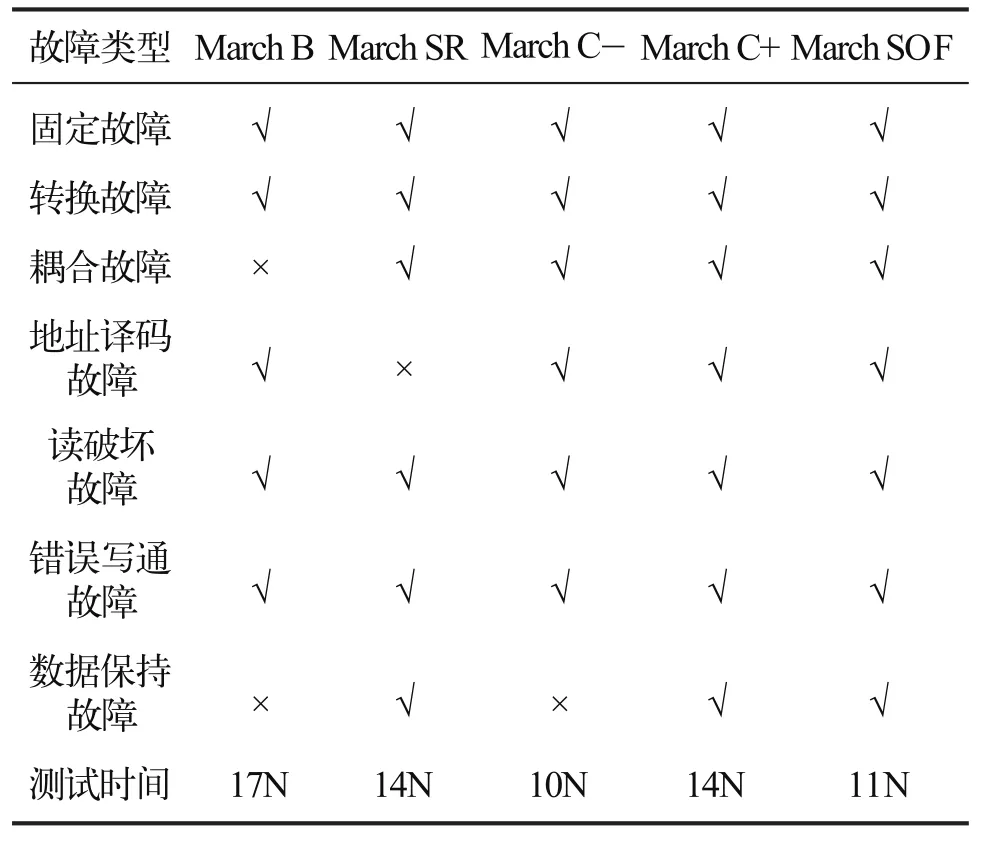

测试存储器推进法(March测试算法)广泛应用在存储器的生产测试中。它先将存储单元写成全“0”状态,然后从最低地址到最高地址连续地读“0”和改写“1”为止。接着,在数据相反的情况下,由最高地址到最低地址重复上述过程。具体的测试序列跟实际测试相关,测试序列不同,所能检测的故障也各异。为此出现了很多种March序列,传统的有March B、March SR、March C-、March C+和March SOF等测试序列[3~4]。为了选用故障覆盖率比较高的序列,我们着重分析比较了这几种算法的优劣。表2是5种March算法的测试序列,它们每一步执行的操作都不相同,序列的长短与测试时间成正比。

表2 测试算法与测试序列

表3是5种March序列对典型故障的覆盖率情况。从表中可以看出,March B所需要的测试时间最多,测试的故障覆盖率也比较差,而March C-是耗时最少的序列,但它也不能覆盖所有典型的故障;March SOF和March C+的测试时间相对于March C-而言稍长些,但其对故障的覆盖率却是最高的。在传统的March测试中一般都选取March C-,但为了检测所有的故障,March SOF和March C+应该是比较好的测试序列。

表3 测试序列与故障检测情况

4 带EDAC防护的SRAM存储器功能验证

4.1带EDAC防护的SRAM存储器

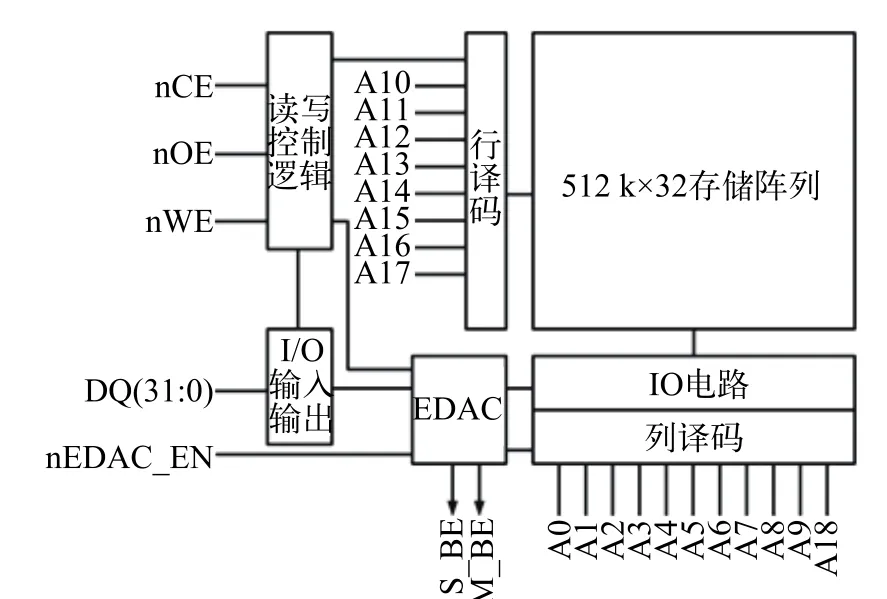

航天器用JMR512k32型带EDAC防护的SRAM存储器是一款高性能抗辐照SRAM,存储容量为16 M(512 k×32)位,内置两组EDAC模块,每组EDAC均可实现纠1检2的功能并指示位错误类型。器件通过片选信号(nCE)及写使能信号(nWE)、输出使能信号(nOE)可实现器件读写操作,内置两组(22, 16)的EDAC(纠1检2)模块,可实现对高低16位的编解码纠检错,通过nEDAC_EN信号选择该功能模块的使能。

器件分为阵列、译码、控制、数据读写与EDAC 5个大部分。阵列部分是所有存储单元的集合,它是单元按顺序排列起来的单元块。译码部分的作用是将输入的地址信号转换成可以在单元阵列中选中恰当单元的字选和列选信号。控制部分的作用是完成读写的逻辑控制及产生异步时序控制信号。数据读写电路的作用是完成数据阵列与单元之间的通信。EDAC的作用是对数据位进行错误检测与纠正,两组EDAC SRAM模块具备独立的两组(22, 16)编码解码设计,每组均具备纠1检2功能。

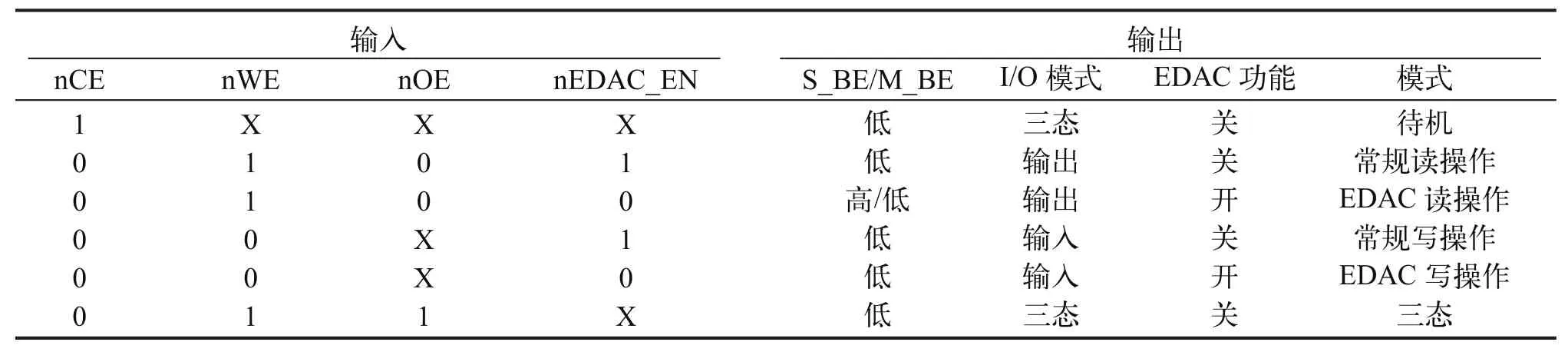

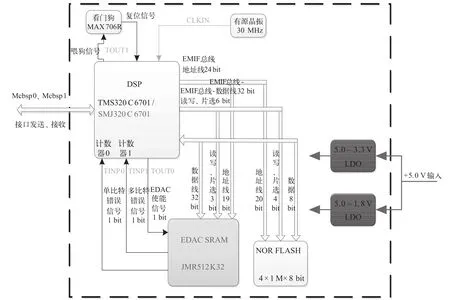

电路功能框图如图11所示,器件的真值表如表4所示。

图11 JMR512k32功能框图

4.2功能验证方案

根据第3章的分析,考虑测试算法复杂度和故障覆盖率,March SOF算法是较好的选择[5]。其算法的复杂度为11N(N为存储器存储单元数),对固定故障、转换故障、耦合故障、地址译码故障、读破坏故障、错误写通故障、数据保持故障的故障覆盖率为100%。

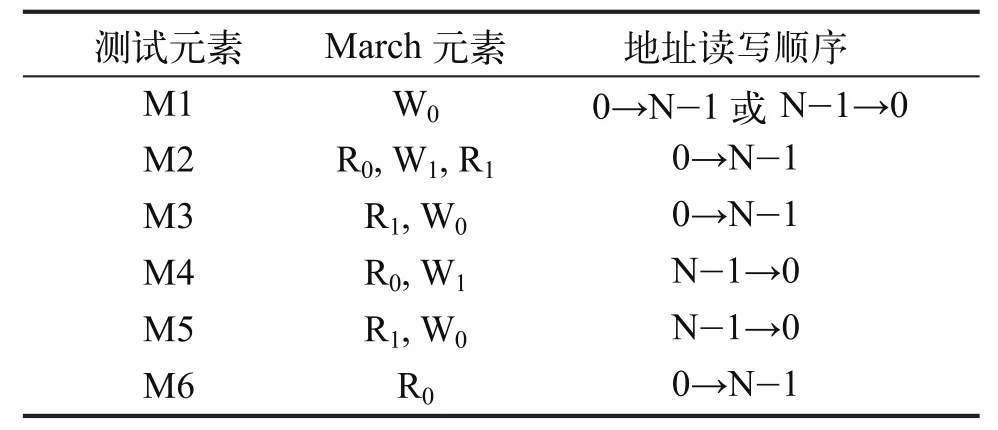

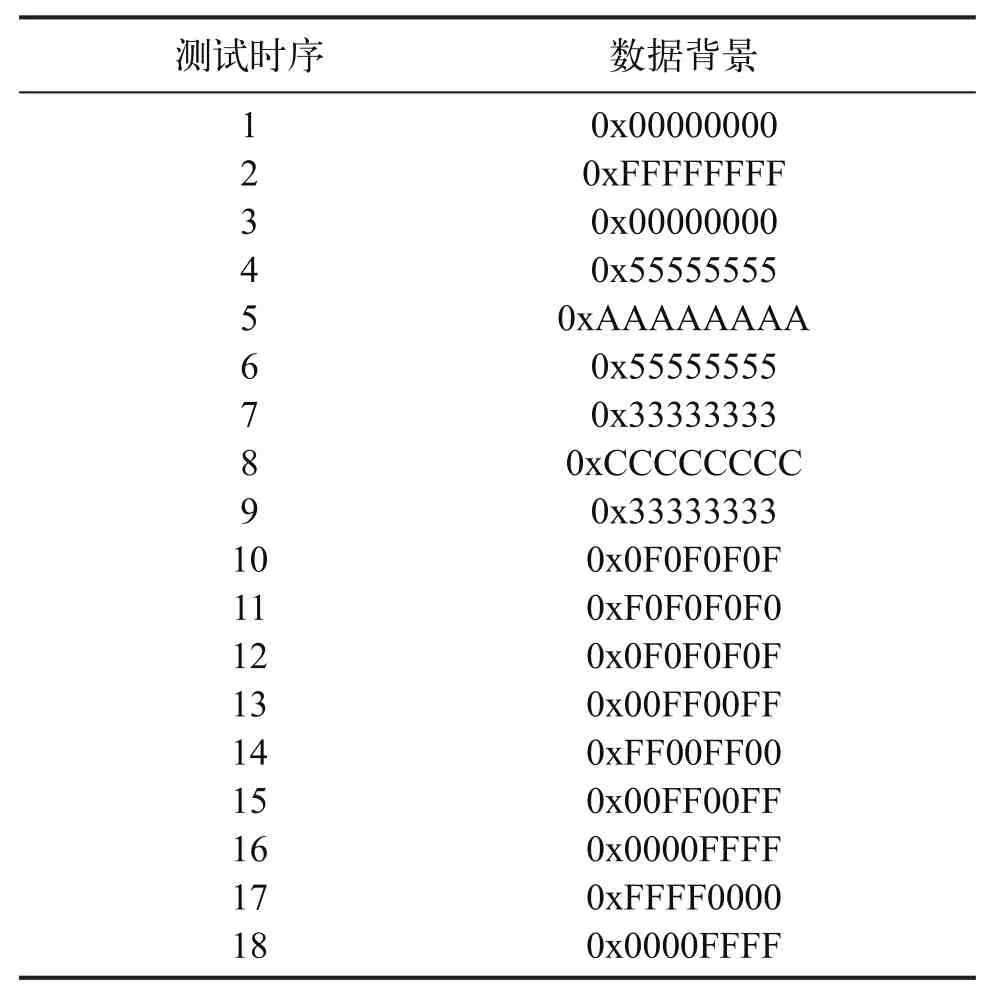

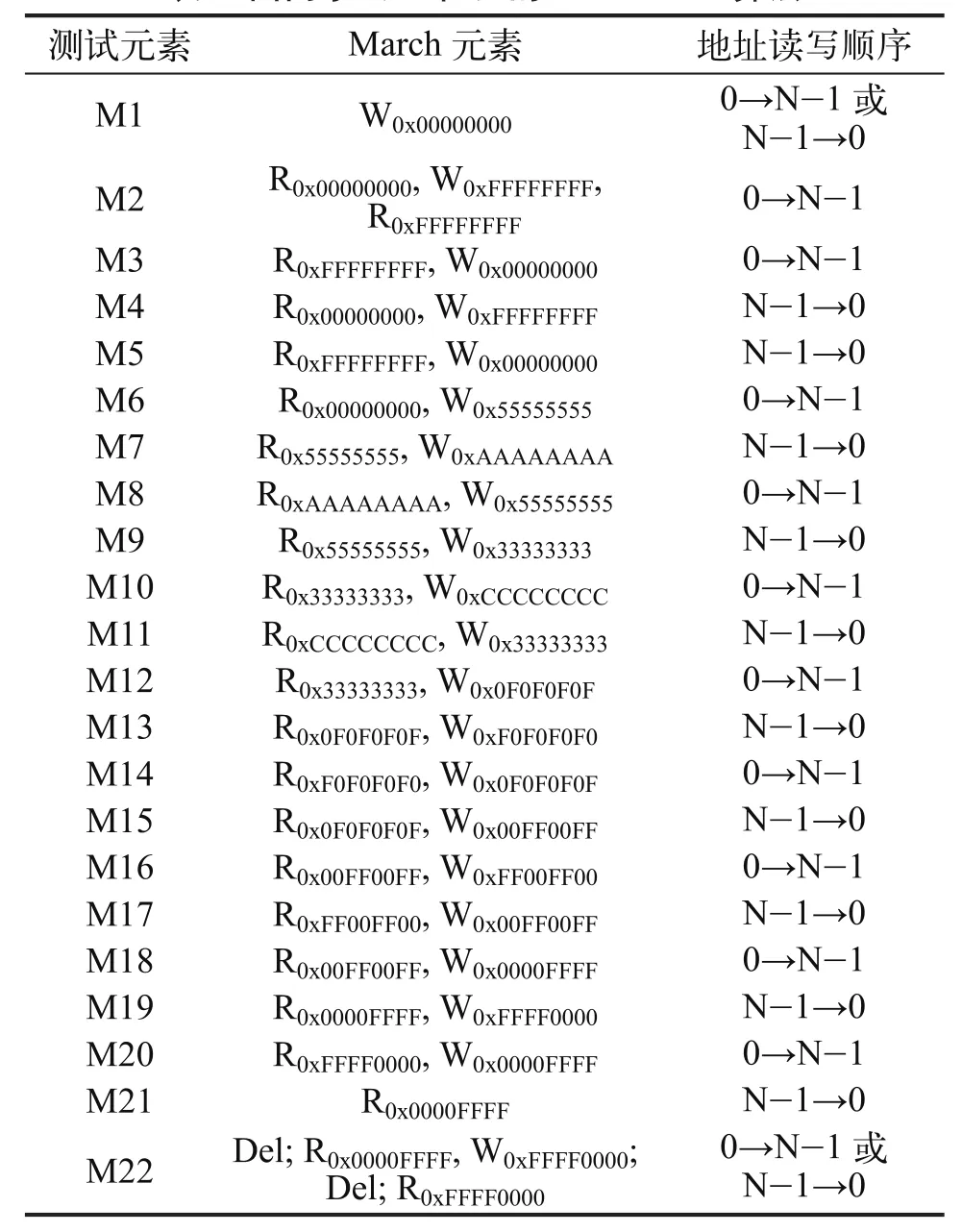

表5介绍的是面向“位”存储器的March算法,而JMR512k32存储器是按32位进行存储的。对于面向32位存储器的March测试算法,可通过对面向“位”的存储器测试算法修改测试数据背景时序得到。根据文献[6]所述,使用任意一个数据背景就可测所有的固定故障、转换故障、地址译码故障、读破坏故障、错误写通故障和字间耦合故障,对于32位的存储器,测试字内的耦合故障的数据背景时序如表6所示。

表4 器件真值表

表5 面向位的March SOF算法

对于数据保持故障,March元素中只需包含Del就可覆盖数据保持故障(Del为延时元素,通常设为100 ms[3]),并且对于面向“字”的存储器,只需对其中一对互为反码的数据背景进行数据保持故障测试。因此,经优化后,面向“字”的March SOF算法如表7所示。对于EDAC功能的验证,采用故障注入的方式进行,具体方法如下:

先将EDAC功能打开,连续写入三个地址的数据;之后将EDAC功能关闭,改写其中一个地址的数据,可以改写单位,也可以改写多位;然后将EDAC功能打开,回读3个地址的数据,对比读出数据的正确性,同时观察翻转标志信号;重复以上步骤直至覆盖所有地址空间的每个数据位,包括单错和双错两种情况。

表6 字内的耦合故障测试数据背景时序

4.3方案实施

JMR512k32验证板由数字信号处理器(TMS320C6701)、存储器(SRAM、FLASH)、看门狗芯片和电源转换器组成;JMR512k32验证板测试程序运行在TMS320C6701内部存储器,测试程序实现对FLASH芯片的读写和擦除功能、看门狗芯片喂狗功能和JMR512k32 SRAM的测试功能,JMR512k32仅作为数据存储器。

表7 面向字(32位)的March SOF 算法

JMR512k32验证板SRAM测试方法包括March算法测试、SRAM检错测试(1位注错测试)和SRAM纠错测试(2位注错测试),具体的测试流程如下:

(1)系统初始化包括中断控制器初始化,定时器0、定时器1初始化,Mcbsp串口通信初始化和变量初始化;

(2)测试过程1:开启JMR512k32的EDAC模式,进行March算法测试含表7所示的22个测试步骤,每个测试步骤的测试结果用Mcbsp串口发送给上位机Labview测试程序;

(3)测试过程2:关闭JMR512k32的EDAC模式,进行March算法测试含表7所示的22个测试步骤,每个测试步骤的测试结果用Mcbsp串口发送给上位机Labview测试程序;

(4)测试过程3:1位注错测试,先进行低16位测试,然后进行高16位测试,最后进行低16位和高16 位同时测试;每个测试步骤的测试结果用Mcbsp串口发送给上位机Labview测试程序;

(5)测试过程4:2位注错测试,先进行低16位测试,然后进行高16位测试,最后进行低16位和高16位同时测试;每个测试步骤的测试结果用Mcbsp串口发送给上位机Labview测试程序;

(6)重复步骤2~ 步骤5。

采用本功能验证方案,该器件进行了25.5次(时间12天)的热循环试验,器件功能正常。

图12 JMR512K32验证板原理框图

5 结论

本文采用March SOF算法与故障注入的EDAC专用测试程序相结合的方法,对存储器进行了全方位完备的测试。首先通过March SOF算法对固定故障、转换故障、耦合故障、地址译码故障、读破坏故障、错误写通故障、数据保持故障达到100%覆盖率,之后通过故障注入的EDAC专用测试程序进行EDAC功能验证。实践证明,这种测试法能快速检查出存储单元固定0/1故障、转换故障、邻近单元读写干扰故障(耦合故障)、译码选择故障和数据保持故障等典型故障,最终通过较快速与完备的手段完成该器件的测试,保证了测试质量与效率。

参考文献:

[1] 林博. 存储芯片纠检错电路设计与FPGA实现[D]. 哈尔滨:哈尔滨工业大学,2007.

[2] Rob Dekker. A realistic fault model and test algorithm for static random access memories [J]. IEEE Transactions on Computer-Aided Design, 1990, 9(6): 567-572.

[3] Van de Goor AD J. Using March Tests to Test SRAMs [J]. IEEE Design and Test of Computers, 1993, 10, 8-14.

[4] Sultan M Al-Harbi. An efficient methodology for generating optimal and uniform march tests [A]. VLSI Test Symposium 2001 Proceedings [C], 2001. 231-237.

[5] Van de Goor AD J. March LR, a test for realistic linked faults [A]. 14th IEEE VLSI Test Symposium [C]. Princeton, 1996. 272-280.

[6] Van de Goor AD J.March tests for word-oriented memories [A]. Design Automation and Test in Europe Proceedings [C], 1998. 501-508.

肖爱斌(1982—),男,湖南邵阳人,硕士,毕业于中国空间技术研究院计算机应用技术专业,目前在中国空间技术研究院从事航天器用电子元器件质量保证工作。

4 结论

本文介绍了最大压力约0.1 MPa下的压力传感器封装中的波纹膜片的结构优化设计。利用了有限元分析方法对不锈钢波纹膜片的厚度、波纹深度和波纹数目进行了分析与对比。通过对封装后的压力传感器样品的测试,反映了不锈钢波纹膜片各个参数值的不同对压力传感器输出性能的影响,表明了较小的膜厚与波纹深度、较多的波纹数目有助于提高压力传感器的性能,从而验证了对波纹膜片优化设计的可靠性与可行性,为波纹膜片的设计提供了有价值的参考。

[1] 付兴铭,谭六喜,姚媛,刘胜. 压力传感器封装中波纹膜片的结构优化[J]. 传感器与微系统,2007, 07: 80-81, 84.

[2] 刘春香,刘喜平,苗淑杰,李荣智. 圆弧形波纹膜片的设计计算[J]. 机械工程师,2012, 12: 15-16.

[3] 郭长旭,庞士信,张治国. 波纹膜片性能分析[J]. 仪表技术与传感器,2010, 04: 9-10, 55.

[4] 付兴铭. 汽车用扩散硅压力传感器的设计与封装研究[D]. 华中科技大学,2007.

[5] 刘春香,王东胜,段成燕,王金玲,郭丽娟. 深度传感器中波纹膜片的设计[J]. 黑龙江科技信息,2013, 29: 29, 256.

[6] 袁鸿. 波纹膜片非线性力学进展[J]. 暨南大学学报(自然科学版),2009, 30(05): 18-21.

[7] 刘元浩,赵立波,赵玉龙,蒋庄德,田边,孟超. 基于压力传感器封装的波纹膜片的结构研究[J]. 传感器世界,2008, 12: 12-15.

Research and Application of the Validation Method of Static Random Access Memory for Space Application

XIAO Aibin1, WANG Feiyao1, WANG Wenyan1, JUAN Yang2, ZHANG Leihao1, ZHANG Haoyuan1

(1. China Academy of Space Technology, Beijing 100094, China; 2. China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214035, China)

Abstract:On the basis of research on the failure model and normal function validation method of SRAM, the article presents EDAC test program based on March SOF with failure injection for validation of EDAC SRAM for space application. This method expands March SOF algorithm to 32-bit directional algorithm, and also adds data-hold failure and EDAC function tests, which completes the SRAM function validation. The validation result shows the feasibility and efficiency of this method with real circuits on board.

Key words:SRAM; error detection and correction; function validation; March algorithm

中图分类号:TN402, V446

文献标识码:A

文章编号:1681-1070(2015)05-0014-07

收稿日期:2015-04-27

作者简介:

王俊杰(1989—),男,浙江宁波人,硕士研究生,主要研究方向为传感器封装技术;

秦会斌(1961—),男,山东人,教授,博士,主要研究方向为新型材料与器件、现代传感器设计及应用。