宽动态可变增益放大器的设计*

郭安强,刘倩倩,金亚梅,王志伟(苏州大学电子信息学院,江苏 苏州 215006)

宽动态可变增益放大器的设计*

郭安强,刘倩倩,金亚梅,王志伟

(苏州大学电子信息学院,江苏 苏州 215006)

摘 要:在通信接收机中,当接收的信号强度变化很大时,要求接收机前端的增益随接收信号强度在很宽的范围内自动变化,以输出稳定信号,因此高性能接收机对可变增益放大器提出了更高的要求。设计基于BiCMOS工艺,采用差分输入共射级结构,对宽动态可变增益放大器进行了研究与设计,通过MOS开关改变集电极和发射极电阻以及延迟控制技术,达到宽动态增益的效果。仿真结果表明,三级放大器的增益动态范围为0~65 dB,频率范围为20~90 MHz。

关键词:BiCMOS;宽动态;可变增益放大器

1 引言

随着无线通信技术的飞速发展,无线收发机在现代通讯领域中占据了重要的地位并获得了广泛的应用,如GPS导航、手机通讯等。信号在空气中传播,因路径等因素不同产生不确定的衰减,最后到达接收机中信号的强度可以相差几十分贝,因此接收机前端的高频放大器和中频放大器需要根据接收到的信号强度不同自动调节放大倍数,以保证后续电路的信号幅度相对稳定。

为了满足不同接收机的需要,可变增益放大器一直是业内研究的热点。文献[1]中采用TSMC 0.18 μm RF CMOS工艺设计实现了一种对数增益线性控制型的宽带可变增益放大器,工作频率范围430~2 330 MHz,增益调节范围-3.3~9.5 dB;文献[2]提出了一种针对超外差结构无线宽带接收机的新型可变增益放大器,该放大器工作在50~600 MHz的频率上,增益可调范围为-28~42 dB;文献[3] 在AGC环路中采用带共模反馈的VGA结构,包含一个改进的具有采样保持功能的峰值检测电路,构造出一种新型的指数控制电路。

为了满足宽动态可变增益的需要,本文将通过控制不同MOS管的导通状态,同时改变放大器的负载电阻和射极电阻,双管齐下,达到宽动态改变放大器增益的目的。此外,本文将采用 BiCMOS工艺,使放大电路不仅具有CMOS电路高集成度低功耗的优点,同时具有双极电路高速强电流驱动能力的优点。

2 电路设计

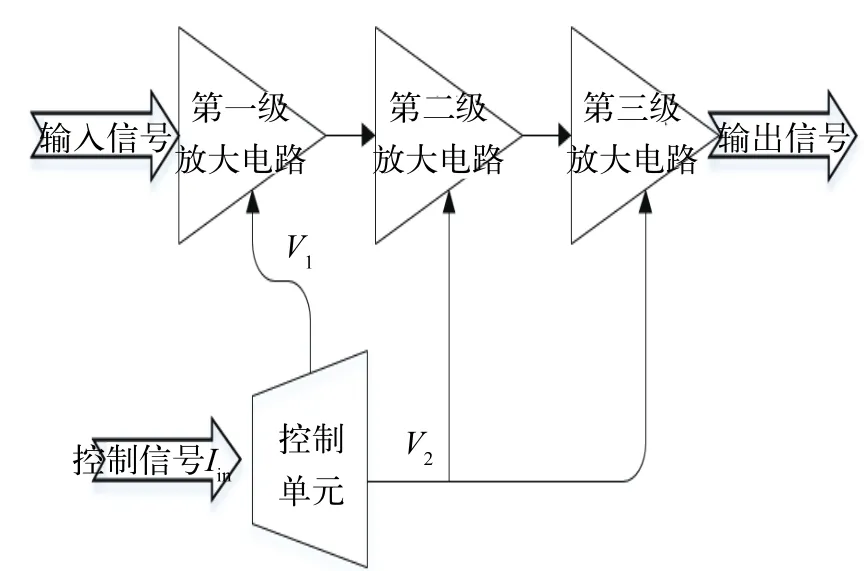

单级放大电路不易达到高增益的设计要求,因此考虑采用三级放大电路级联实现。三级放大电路的增益通过控制电路产生的延迟控制信号控制,实现增益宽动态范围调节,可变增益放大电路的总体结构如图1所示。

图1 三级可变增益放大器结构图

2.1可变增益的实现原理

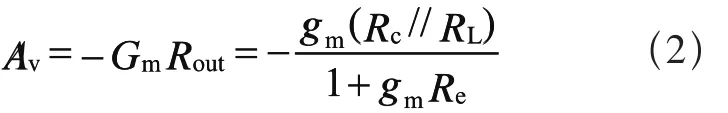

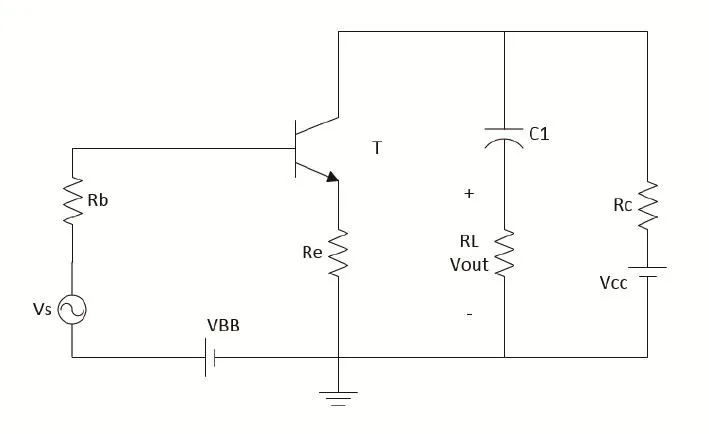

为了宽动态改变放大器的增益,本文采用带负反馈的共射极放大器作为基本的放大电路。BJT组成的共射极放大器的原理电路如图2所示,线性工作时电压增益Av=-GmRout,其中Gm表示输出与地短接时电路的跨导,Rout=Rc//RL表示输入电压为零时的输出电阻[4]。

图2线性工作时有:

共射极放大器的电压增益:

图2 共射极放大器原理图

由式(2)可知:当Rc增大时,电路跨导增大,Av随之增大;当Re增大时,电路输出电阻减小,Av随之减小[5]。因此其他参数不变,通过改变Rc和Re的大小可以实现可变增益放大。

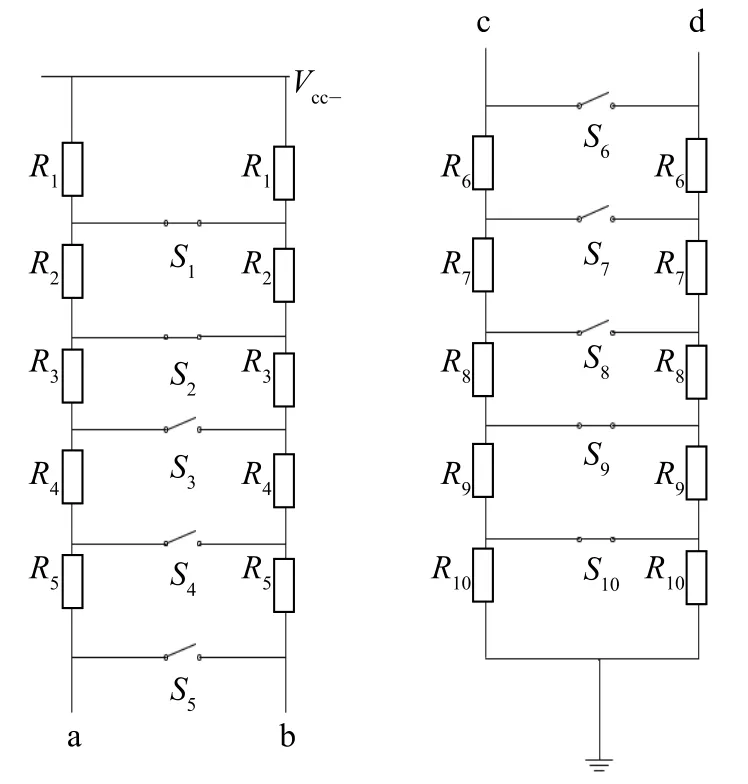

可变电阻Rc和Re可以通过图3所示的MOS开关控制的电阻阵列实现,其中的开关S由MOS开关实现。MOS器件是压控电流型器件,如NMOS,当Vg逐渐升高时,P衬底中的空穴被赶离栅区形成一个耗尽层。当界面电势达到阈值电压Vth时,源漏之间的栅氧下就形成了载流子沟道,晶体管导通[6]。即当时,MOS导通,否则MOS截止,MOS管等效为一个开关。当开关依次闭合或者依次断开时,a、b对Vcc的等效电阻以及c、d对地的等效电阻相应地变化。

图3 MOS开关控制的电阻阵列

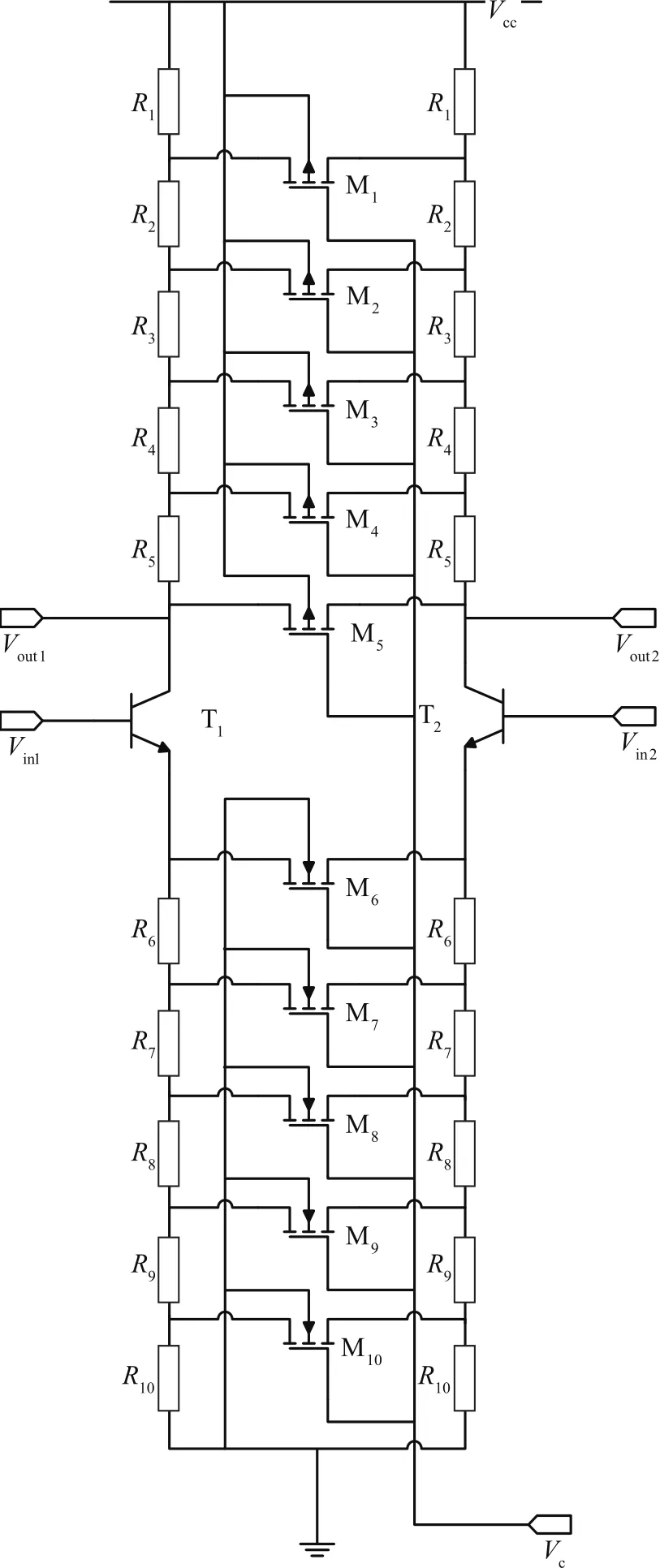

2.2单级放大电路的实现

为了有效地抑制噪声,单级放大电路的设计中采用了BJT构成的差分结构,采用图3所示的等效电阻实现集电极电阻和射极电阻,最终实现的差分结构高增益宽动态增益范围的单级放大电路如图4所示。其中Vc接延迟控制信号,控制MOS管依次导通或者关闭。

由于电阻的串联分压作用,每个MOS管的源极电位Vs各不相同,加上控制电压Vg=Vc之后,|Vgs|不同,每个PMOS和NMOS的导通情况并不一致,等效于一列随控制电压开闭的开关,如图4所示。

图4 单级放大电路

Vc较低时,S6~S10全部断开,S1~S5全部闭合,发射极电阻达到最大值:Re=R6+ R7+ R8+R9+R10,集电极电阻达到最小值:Rc=(R1//R1)+(R2//R2)+(R3//R3)+(R4// R4)+(R5//R5)=。随着Vc增大,S5~S1依次断开,集电极电阻开始增大,由逐步增加到R1+R2+R3+R4+R5。Vc继续增大时,S5~S1全部断开,S6~S10依次闭合,集电极电阻达到最大值:Rc= R1+R2+R3+R4+R5,发射极电阻由R6+R7+R8+R9+R10减小到(R6//R6)+(R7//R7)+(R8//R8)+ (R9//R9)+(R10//R10)=。 MOS开关呈现出递进变化的形式,不同的控制电压对应不同的负载电阻和跨导,达到同时改变Rout和Gm的效果。由式(2)可知,Vc越大,增益越大。

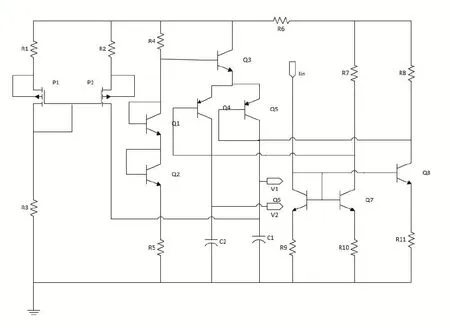

2.3延迟控制电路的设计

由图1可知,当放大器接收到的信号比较微弱时AGC不起控。当接收到的信号强度比较大时,通过放大器的输出检波及误差放大电路产生控制电流Iin。控制电路根据Iin强度的不同产生相应的控制电压V1、V2,分别控制第一级和第二、三级放大电路的增益,使放大器的输出信号相对稳定。延时控制电路如图5所示,当输入电流Iin较小时,流过Q7和Q8的电流较小,而流过Q4和Q5的电流增大。Q5一路增加的电流主要由P1、P2提供,对C1的电荷影响较小,此时V1基本保持不变,控制着第一级VGA增益保持不变。Q4一路没有补偿,V2值因电容C2的放电而下降,率先降低二、三级电路增益。当输入电流继续增大,流过Q8的电流增大,P2路不能完全满足补偿Q5一路产生的电流差,此时电容C1开始放电,V1值下降,第一级VGA也起作用,使电路总的增益继续下降。利用本延迟控制电路可根据输出反馈信号的大小自动控制放大器的增益,保证放大器输出信号相对稳定。

图5 延时控制电路

3 仿真结果及分析

图1所示的三级放大电路中的第一级采用图4所示的差分放大电路。第二、三级采用与图4相同的结构,同时采用图5所示的延迟控制电路。整个放大器的设计是基于CSMC 0.5 μm BiCMOS工艺实现的。

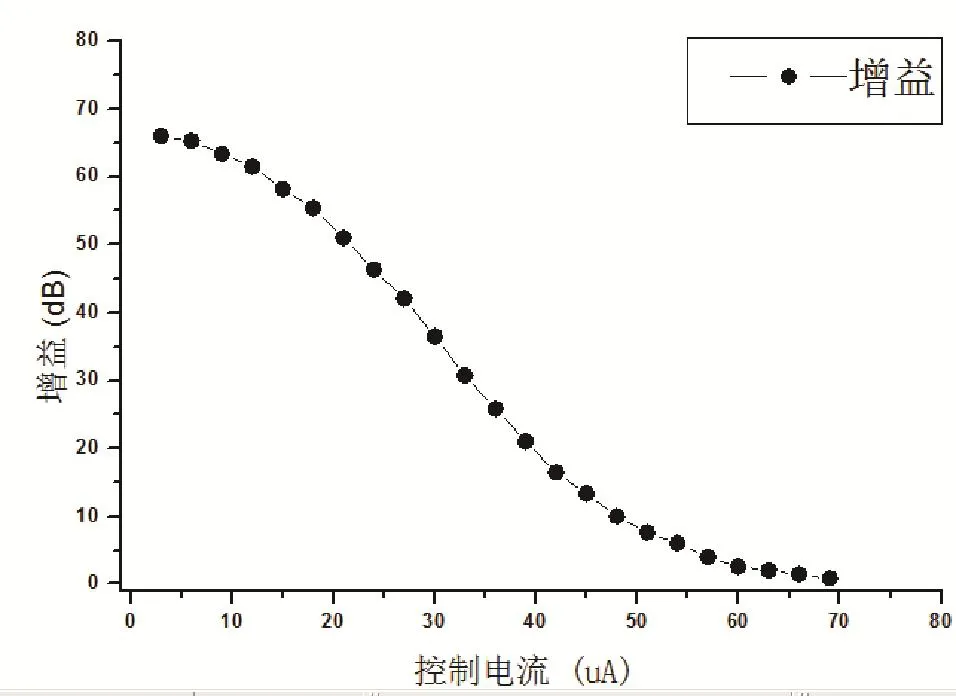

为了研究图1所示放大器的增益随控制信号变化的动态范围,基于CSMC 0.5 μm BiCMOS工艺库文件,工作频率为40 MHz,使用Cadence仿真工具做交流小信号分析,控制电流在5 μA到68 μA的范围内扫描,仿真结果如图6所示。由图中可以看出,在控制电流从5 μA增大到68 μA的过程中,三级放大器的增益由65 dB下降到接近0 dB,也就是说,随着输入控制电流的增大,电路总增益会下降,增益变化范围约为65 dB,表明放大电路的增益具有宽动态特性。

图6 增益-控制电流曲线

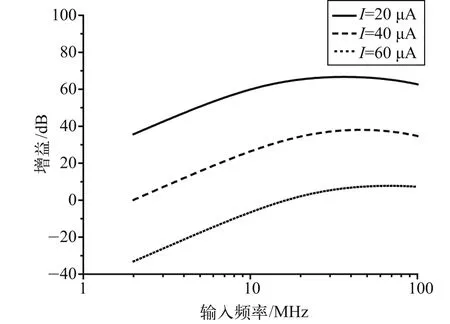

放大器的增益随频率变化,为了研究放大器的频率特性,设定控制电流为不同值时做交流小信号分析,即得到对应控制电流的放大器增益幅频特性曲线。图7给出了控制电流分别为20 μA、40 μA、60 μA时交流小信号仿真结果,仿真结果三种情况的3 dB带宽分别为10~100 MHz、16~90 MHz和20~100 MHz。工作带宽取上述三者公共部分,即放大电路的带宽为20~90 MHz。

4 结论

本文基于CSMC 0.5 μm BiCMOS工艺设计了一种MOS开关控制电阻阵列的三级差分结构可变增益放大器,通过开关电阻网络改变共射级的等效跨导和输出电阻,通过延迟控制电路的控制,实现了高增益宽动态增益范围的放大电路。电路仿真表明:三级放大电路的工作频率范围为20~90 MHz,增益动态范围为0~65 dB,放大电路具有良好的线性性能。

图7 增益-频率特性曲线

参考文献:

[1] 郭峰,李智群,陈东东,李海松,王志功. 宽带CMOS可变增益放大器的设计[J]. 半导体学报,2007, 12.

[2] 郑吉华,李永明,陈弘毅. CMOS宽动态的可变增益放大器[J]. 半导体学报,2003, 8.

[3] Liu Xiaowei, Xu Xiaowei, TAN Xiaoyun. The Design of Automatic Gain Control in Self-Excitation Drive Circuit of Gyroscope [C]. Chinese Journal of Sensor and Actuators, 2007.

[4] 康华光,陈大钦,张林. 电子技术基础[M]. 北京:高等教育出版社,2012.

[5] R Jacob, Baker, Harry W Li, David E Boyce. CMOS Circuit Design, Layout, and Simulation [M]. Beijing: China Machine Press, 2006.

[6] Razavi B. Design of Analog CMOS Integrated Circuits [M]. Boston: McGraw-Hill, 2001.

Design of Wide Dynamic Variable Gain Amplifier

GUO Anqiang, LIU Qianqian, JIN Yamei, WANG Zhiwei

(Soochow University, Suzhou 215006, China)

Abstract:In order to obtain the stable signal, it demands the gain of receiver automatically change when the received signal changes within a wide dynamic range in the communication receiver. It means that high performance receiver should put forward stricter requirements to variable gain amplifier. The paper researches and designs the structure for wide dynamic variable gain amplifier. Based on BiCMOS, this essay aims at the research and design of the wide dynamic variable gain amplifier with the differential input common emitter structure. The MOS switch which changes the resistance of collector and emitter together with delay control technology contributes to the wide dynamic gain. The chip is simulated by using Cadence’s Spectre software and implementted by using CSMC 0.5 μm process. Simulation results indicate that dynamic range of gain is from 0 to 60 dB; it receives the frequency from 20 MHz to 90 MHz, and has the power dissipation less than 20 mW.

Key words:BiCMOS; wide dynamic range; variable gain amplifier

中图分类号:TN402

文献标识码:A

文章编号:1681-1070(2015)05-0024-04

收稿日期:2015-03-04

*基金项目:江苏省大学生创新创业省级重点项目(201310285035Z)

作者简介:

郭安强(1992—),男,江西永丰人,就读于苏州大学电子信息学院微电子系电子科学与技术专业;

刘倩倩,女,河南周口人,就读于苏州大学电子信息学院微电子系电子科学与技术专业;

金亚梅,女,江苏南通人,就读于苏州大学电子信息学院微电子系电子科学与技术专业;

王志伟,男,江苏泰州人,就读于苏州大学电子信息学院微电子系电子科学与技术专业。