基于高速DDFS的高精度DAC的设计

张 涛,万书芹,苏小波,于宗光

基于高速DDFS的高精度DAC的设计

张 涛,万书芹,苏小波,于宗光

(中国电子科技集团公司第58研究所,江苏无锡 214035)

设计了一种应用于高速数字频率合成器的高精度DAC。电路采用6+8分段式电流舵结构进行设计,高6位为温度计编码,低8位为二进制编码,设计中采用Q2旋转漫游算法排布电流源阵列,双路归零编码控制输出。基于SMIC 0.13μm 1P6M数模混合CMOS工艺设计实现,芯片面积2.66×2.54mm2,测试结果积分非线性误差INL≤1.5 LSB,微分非线性误差DNL≤0.8 LSB,在1 GHz时钟采样频率,401 MHz输出频率处,SFDR为88 dBc。

数模转换器;电流舵;双路归零;INL、DNL

0 引 言

数模转换器(DAC)是一种用于将输入的多位数字信号转换为模拟信号输出的器件,作为数字信号领域与模拟信号领域的接口得到广泛应用。高速高精度DAC器件更是成为现代电子系统中不可或缺的重要组件,民用领域可应用于无线基站、自动控制、医疗电子、视频显示、宽带通讯等,在国防军事领域也广泛用在雷达、通讯、电子战等各个方面[1,2]。近年来随着数字技术的飞速发展,对于高速高精度的DAC的需求更是迫切。我国从70年代起开始研究DAC技术,虽然开发出DAC有百余款,但是真正得到大批量市场应用的并不多,开展高精度DAC的研究工作,缩短与国外技术差距,无论是对于国民生产还是国防建设都起着重大推动作用。

文中介绍了基于0.13μm工艺设计的一款高速,高精度、高稳定性DAC,电路经测试及上机试用,各项技术指标达到预期设计目标,性能稳定。

1 DAC结构

DAC主要用于将数字输入信号转换为模拟信号输入,输入多为并行的二进制编码形式,输出形式多为电流型或电压型输出。电路内部多含有基准电压源或基准电流源,根据比例换算为全1的满幅值输出,总体功能上DAC器件可以将输入的数字信号量化模拟信号。

对于理想的数模转换器可将N位的数据输入码(DN-1,DN-2……D1,D0)转换为等比例电压(或电流)输出,其关系应该符合下式:

式中K是比例因子;VREF为基准电压源;D为数字输入码。

式中D0为最高有效位;DN-1为最低有效位,合并式(1)和式(2)可以得到DAC输出的输出公式:

上式(1)~(2)表明DAC的输出来自于输入信号乘以基准电压值的系数,由一系列的二进制权值分量叠加而成。权值间的匹配度与DAC的转换精度相关,获得更高匹配度和更好的输出单调性是DAC的设计重点。

当前DAC的架构主要有电压定标型、电荷定标型、电流定标型。其中以电流定标型架构性能最佳,根据编码方式的不同电流定标型DAC又可分为三种类型:二进制码架构、温度计码架构和分段式架构。采用二进制编码架构不需要额外的译码电路,可有效降低设计的复杂度,但该结构在高精度电路中应用将导致高位权值电路过大,难匹配。采用温度计编码结构的DAC,每变化1 LSB只会有一个电流源打开或关闭,故输出电流时抖动较小,可获得较好的DNL和INL特性,缺点是精度每提高一位,电流源阵列的数量将要增长一倍。

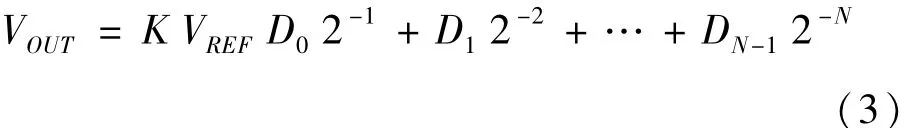

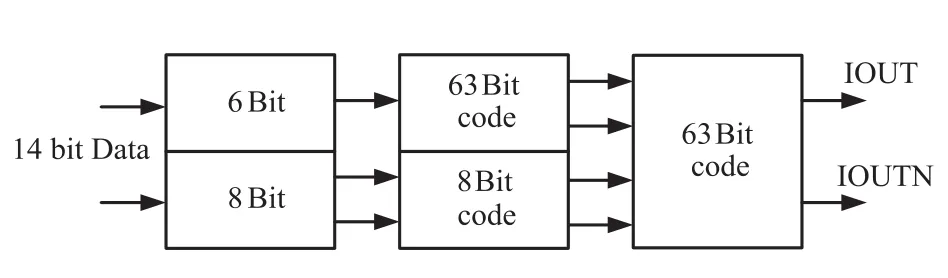

为了平衡速度、精度、面积及功耗,电路的架构中采用分段式架构,结构如图1所示,时钟管理模块提供参考时钟给数据输入缓冲和译码模块,译码的开关信号用于控制8+6分段电流源阵列的开合,电路内置片内基准源,可以提供1.2 V的基准电压,最终输出为电流型输出,典型应用时外接50欧的负载电阻。

图1 电路结构图

2 电路设计

2.1译码器设计

该电路译码器部分设计为低8位二进制码+高6位温度计码设计,低8位采用二进制码直接控制电流源,高6位由温度计译码为63位码控制电流源,图2为14位译码示意图。

图2 译码器示意图

DAC译码器主要将数字输入信号转换为数字编码用于控制电流源开关阵列,以选择需要导通的电流源管。14 BIT信号采用6+8的两段译码结构,高6位用温度计编码方式,为了抑制开关电流源间的开关时序串扰,采用了全差分结构开关电流源,所以得到互补的63位温度计编码。低8位信号采用普通二进制编码以减少电路规模,可得到14位二进制编码。译码器最终输出为(63+8)×4=284位的双路归零[3]脉冲码。

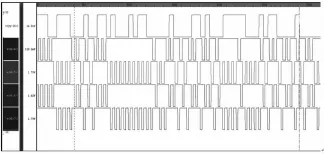

TZ方式是将整个完整的时钟周期分为两个部分,前半周期,RTZ的输出与输入相同,后半周期,RTZ的输出恢复到零。RTZ电路可以减小码间干扰和D/A转换器的SINC滚降,降低重构滤波器的复杂性,提高SFDR。然而当输出大幅度信号时,采用RTZ编码方式引起输出信号在半个时钟周期内的大幅度变化,更容易使后面所驱动的电路进入线性区,并使DAC的输出对时钟抖动更加敏感,增加后续滤波器的滤波难度。为克服RTZ编码方式的缺陷,可以采用双路归零编码(DRTZ)方式[4],即在原RTZ的输出波形基础上添加一个延时半个时钟周期的相同RTZ波形,两个波形叠加得到DAC的最终输出。图3为采用HSIM5.0,模型TT,仿真温度25摄氏度的仿真条件下开关编码转换为双路归零码的仿真波形,可以看出译码器将单路开关信号yy<14>转换为4路归零码信号kk<4:7>。

图3 DRTZ编码波形图

2.2电流源及阵列设计

电流源单元阵列是电流舵结构DAC系统中关键单元之一,电流源单元的电流匹配很大程度上影响了DAC的INL和DNL,并且会因为传输非线性而降低系统的SNR和SFDR。

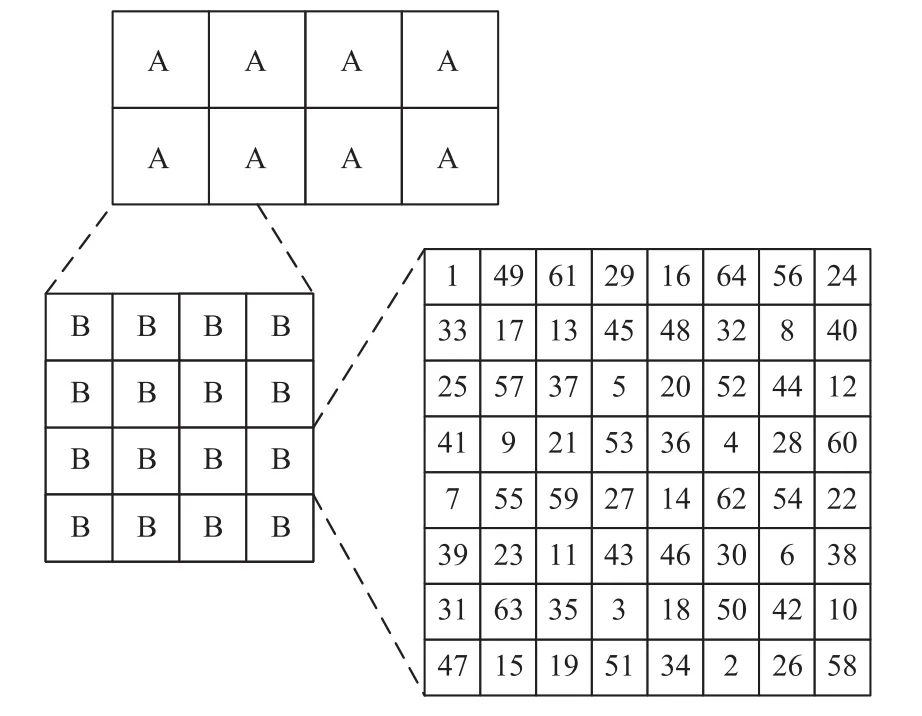

电流源阵列设计是电流舵型DAC电路设计中的关键,如第二章中所分析的,由于工艺造成的系统失配会严重影响到DAC的线性度指标,对动态指标也会产生间接影响。目前有多种方案可以对匹配误差进行优化设计,如行列开关方案、分层开关方案、动态匹配技术及校准技术等等。在本电路设计中,电流源阵列排布基于Q2旋转漫游的方法,共有8× 16=128个小阵列构成,将63组MSB的电流源依次分布到每个小阵列的2-64号位,而每个小阵列中的1号位用于布局B0~B7的电流源,最终电流源阵列布局规则如图4所示。

图4 电流源阵列布局

3 测试结果

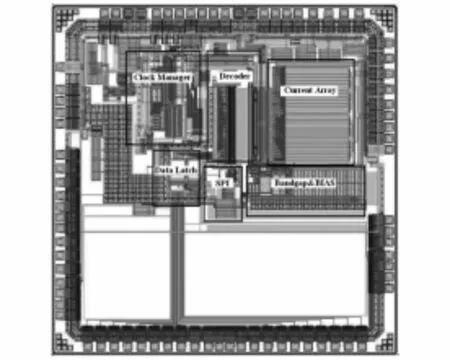

电路设计基于性能、成本、功耗及成品率等综合因素考虑,采用业界较为成熟的SMIC公司提供的一层多晶硅、六层金属0.13μm CMOS工艺实现。整体芯片面积为2.66×2.54 mm2,工作电压采用1.2 V,3.3 V双电源。

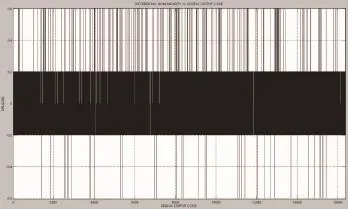

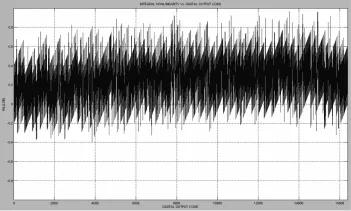

图5为芯片的整体版图,由图可见各子模块的分布和面积大小。图6为在系统频率1 GHz,输出频率401 MHz条件下SFDR的是测试结果,窄带SFDR约为88 dBc,宽带SFDR约为67 dBc。图7、图8分别为微分非线性误差DNL,小于0.8 LSB,积分非线性误差INL≤小于1.5 LSB。

图5 芯片整体版图

图6 SFDR测试图

图7 DNL测试结果

图8 INL测试结果

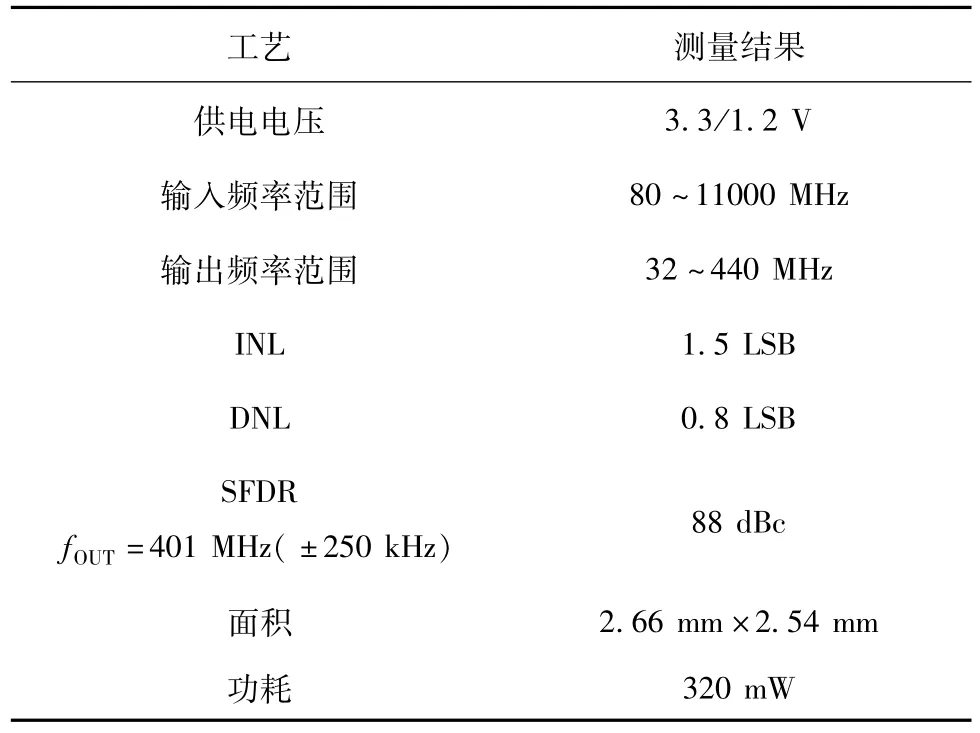

表1为DDS整体电路的性能参数指标。

表1 主要性能参数实测值

4 结 语

基于SMIC 0.13μm 1P6M数模混合CMOS工艺设计了14位、1 GHz DAC电路,经流片验证及测试,在1.8 V/3.3 V供电、常温条件下,芯片最高时钟频率可达1 GHz,窄带SFDR≤88 dBc,宽带SFDR≤-67 dBc。INL≥1.5 LSB,DNL≤0.8 LSB。

[1] Dong Hyun Ko,JiHoon Jung.A Design of 14-bits ADC and DAC for CODEC Applications in 0.18μm CMOS Process[J].4th IEEE International Symposium on Electronic Design,Test and Applications,2008:3-6.

[2] Mercer D.A Low Power Current Steering Digital to Analog Converter in 0.18 micron CMOS[J].ISLPED 2005 Digest of Technical Papers.

[3] 须自明,万书芹,于宗光等.内嵌14位DAC的高速直接数字频率合成器的设计[J].中国电子科学研究院学报,2011,6(1):31-35.

[4] Robert W.Adams,Acton;Khiem Quang Nguyen,Tewksbury,Dual Return-to-rero Pulse Encoding in A DAC Output Stage[P].United States Patent:6061010,2000.9.

Design of DDFS-Based High Accuracy Digital-to-analog Converter

ZHANG Tao,WAN Shu-qin,SU Xiao-bo,YU Zong-guang

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi214035,China)

An embedded 14-bit1-GS/s digital-to-analog converter(DAC)for Direct Digital Frequency Synthesizer(DDFS)application is presented.The DAC is implemented using a segmented current-steering architecture,with the top 6bits and the remaining 8 bits.It uses the novel Q2 Random Walk switching scheme to obtain reduce tuning.The output stage of dual return-to-zero scheme is used to enhance the dynamic performance of spurious-free dynamic range(SFDR).The DAC core is fabricated in a 1P6M0.13um 1P6Mstandard CMOS technology,occupies a die area of only 2.66×2.54 squared mm.The measured differential non-linearity lies between-0.8 LSB and 0.8LSB,integral non-linearity lies between-1.5LSB and 1.5LSB.And the SFDR is 88 dB at401MHz output of1GHz sampling clock rate.

Current steering DAC;Current-steering;Dual return-to-zero;INL;DNL

TN4

:A

:1673-5692(2015)06-632-04

张 涛(1981—),男,江苏南昌人,硕士,高级工程师,主要研究方向为数模混合电路研发;

E-mail:i040410103@126.com

万书芹(1977—),女,江苏兴化人,博士,高级工程师,主要研究方向为数模混合电路研发;

苏小波(1984—)男,江苏南通人,硕士,工程师,主要研究方向为数模混合电路研发;

于宗光(1964—),男,山东潍坊人,博士,教授,主要研究方向为集成电路的设计开发。

10.3969/j.issn.1673-5692.2015.06.013

2015-06-12

2015-11-10

333高层次人才培养工程专项资助(2007124);广东省部产学研合作引导项目资助(2009B090300416)