基于FPGA的PLC动态并行执行定时器的设计

黄仕林,李克俭,蔡启仲

(广西科技大学电气与信息工程学院,广西柳州 545006)

基于FPGA的PLC动态并行执行定时器的设计

黄仕林,李克俭,蔡启仲

(广西科技大学电气与信息工程学院,广西柳州 545006)

PLC内部设置有众多的定时器,通常在工程应用中只使用了部分定时器。因此应用ARM-FPGA架构的PLC系统,设计FPGA定时器控制器的体系结构,1 ms作为基本定时单位,采用地址映射存储器顺序存储被PLC用户程序使用了的定时器的编号,只对被使用的定时器进行定时操作,提高了PLC的定时计数处理速度。阐述了定时器控制器的各功能模块的工作原理,以及与FPGA中央控制器的通信方式和通信的指令命令。经过仿真与测试,定时误差不大于0.1 ms,减少了PLC定时器执行定时操作的时间,达到精确定时的目的。

可编程控制器;定时器;现场可编程门阵列;地址映射存储器;通信协议

0 引言

PLC(Programmable Logic Controller)可编程控制器是工业控制常用的重要控制器件,它采用了可编程的内部存储器存储程序并执行,输入或输出数字量或模拟量控制各类生产过程[1]。采用ARM-FPGA架构的PLC系统可以很好的融合ARM高速低功耗和FPGA并行工作的优点,该PLC系统的主控制器为ARM,FPGA则作为协处理器与ARM协同完成各种并行运算工作[2-3]。

通过对PLC定时器的运行特点的研究与分析,设计的动态并行执行的定时器控制器可以根据具体工程应用来重构其内部的定时器的总数,实现对FPGA资源的灵活配置。并通过地址映射存储器的使用,能够在执行定时操作时迅速地在所设计的256个定时器中找到需要进行定时操作的定时器的相关数据,跳过了对未使用定时器的数据的读取和判断操作,从而使定时器控制器的定时操作更加高效,提高了可编程控制器定时器的执行效率。

1 定时器控制器设计

定时器控制器的电路结构如图1所示,包含模块有:端口读写控制器,地址映射存储器,定时存储器,1 kHz脉冲生成器,指令执行器,定时控制器。定时结果上传控制器。

图1 定时器控制器结构图

1.1 端口读写控制器

定时器控制器通过端口读写控制器与中央控制器进行数据通信。端口包括32位DATAC数据线,5位ADDRC模块地址线,RDC读信号线,WDC写信号线;RST复位线,BUSY忙信号线,ASK定时器控制器读请求信号线;,ANS中央控制器读应答信号线,CLK系统时钟输入线。其中RST复位线使用低电平复位,低电平的保持时间要大于20 ns。RDC和WDC为低电平使能,ASK与ANS线均为低电平有效。DATAC是使用组合逻辑三态门构成的32位双向I/O口。CE线是用以切换定时控制器、定时结果上传控制器与指令执行器的内部信号线,保证指令执行的优先级高于定时操作和定时结果上传。端口读写控制器可以存储一条指令,当存储有指令即指令执行时,置BUSY线和CE线为低电平,若从指令执行器处接收到指令执行结束信息时,置BUSY线和CE线为高电平。

1.2 地址映射存储器

定时器当前值和设定值在相应存储器中的存储位置是与定时器本身的编号对应,即定时器的编号为定时当前值和定时设置值在存储器中的地址。为了达到动态执行的目的,使用地址映射存储器按初始化的顺序存储被使用的定时器的编号。当进行定时操作或者进行定时结果上传操作时,只需要从地址映射寄存器中的第一个地址开始顺序读取被使用的定时器的编号,以此编号为地址,便可以迅速地在定时存储器中找到使用了的定时器的相关数据进行操作。这样就跳过了未使用的定时器,从而达到了提高系统执行效率的目的。地址映射存储器使用Libero8.3 IDE软件提供的双端口存储器IP核生成,为9位×256的结构,D8位为使用标志位,D7~D0位存储被使用的定时器编号,若D8位为1,则D7~D0位定时器编号有效,否则代表该定时器定时到或此定时器未被使用。存储数据格式如表1所示。

表1 地址映射存储器存储数据格式表

1.3 定时存储器

定时存储器分为定时当前值存储器、定时设置值存储器、定时结果存储器,用以实现定时器状态信息、包括复位、定时器通断电等定时相关信息以及定时结果的存储。

定时器当前值存储器设计为27位×256的结构,用以存储定时器的临时计数数据、当前状态信息、定时当前值和编号信息,定时器的编号即为其相关信息在定时当前值存储器中的地址。因为定时器控制器的定时时钟是以1 ms为单位,设计8位的临时计数区以实现10 ms和100 ms为定时单位的定时器的定时。定时当前值存储器存储数据格式如表2所示。

表2 定时当前值存储器存储数据格式表

定时器设置值存储器设计为18位×256的结构,用以存储定时器的定时设置值,定时器的编号即为其设置值在定时设置值存储器中的地址。

定时结果存储器设计为1位×256的结构,以定时器的编号为地址存储定时器的定时结果信息,如果某一位的数值为1,则代表该位在定时结果存储器中的地址对应的编号的定时器定时已到。

1.4 1 kHz脉冲生成器

由于PLC常用的内部定时器定时单位分别为1 ms、10 ms、100 ms,故采用1 kHz作为定时时钟,以满足常用定时单位中1 ms定时单位的设计要求。

1 kHz脉冲生成器是通过对50 MHz系统时钟的计数生成占空比为90%的1 ms为周期的脉冲。计数器计数值在0~44 999之间输出高电平,在45 000~49 999之间输出低电平,而后计数值将归0,重新开始计数。当该脉冲为高电平时,定时控制器将会对每一个被使用了的且定时未到的定时器进行定时操作,当该脉冲为低电平时,定时器控制器将会判断是否有定时器定时到,如果有则上传定时到的定时器的编号信息,否则跳过此阶段等待该脉冲的高电平进行下一次定时操作。

1.5 指令执行器

当中央控制器对定时器控制器发送指令之后,指令通过端口读写控制器被送至指令执行器。通过对中央控制器发送来的指令里的D31~D29这三位数据的检测,判断指令的类型,启动指令执行器内部各个指令对应的子模块,执行相关的数据操作。指令执行结束后将发送指令结束信息至端口读写控制器,用以告知端口读写控制器指令执行结束,使端口读写控制器置高BUSY线和CE线。流程图如图2所示。

图2 指令执行器流程图

1.6 定时控制器

定时控制器负责对被使用的定时器每1ms进行一次定时操作,告知定时结果上传控制器在此定时时钟周期内是否有定时器定时结束。当定时器控制器内没有指令执行且定时操作结束标志寄存器K1为0时,定时控制器将会执行定时操作。定时操作分为三个步骤,第一步:两个时钟周期,通过从地址映射存储器中读取被使用了的定时器的编号,确定其是否定时结束以及其相关信息在定时存储器中的地址;第二步:两个时钟周期,从定时存储器中读取出的定时器的信息;第三步:三个时钟周期,对定时器的定时数据进行判断,包括是否通电,以及对定时当前值进行“加1”操作并与定时设定值进行比较和判断,是否需要写入定时结束信息等。操作完毕后将相关信息写入定时存储器。如此即完成了对定时存储器中的数据进行“读-改-写”的定时操作。包括流程图如图3所示。

图3 定时控制器流程图

1.7 定时结果上传控制器

定时结果上传控制器负责将一个定时时钟周期内定时结束的定时器的编号信息上传给中央控制器。当定时器控制器内没有指令执行,定时结束标志寄存器sign为0时,定时结果上传控制器将会执行定时结果上传操作。定时结果上传控制器先从地址映射存储器中顺序读取被使用了的定时器的编号信息,并以编号为地址,读取定时结果存储器中该定时器的定时结束信息,判断是否需要上传该定时器的编号。若定时结束标志寄存器sign为1,则跳过上传阶段,等待下一次定时时钟的低电平。流程图如图4所示。

图4 定时结果上传控制器流程图

2 中央控制器与定时器控制器的通信协议

定时器控制器主要实现的功能就是接收中央控制器发来的经过ARM编译后的PLC指令,根据指令自主完成对定时器的相关复位、设定值修改、定时操作、定时结果上传等操作[4-5]。

2.1 通信时序

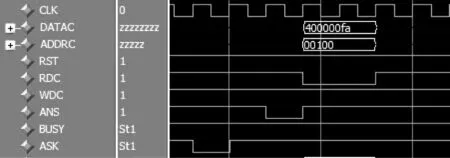

定时器控制器与中央控制器的通信时序如图5所示,BUSY线为忙信号线,当BUSY线为高电平时才可以进行写操作,只有在接收到ASK低电平信号后才可进行读操作。

(a)写时序

(b)读时序图5 定时器控制器数据读写时序图

2.2 通信数据格式

根据PLC的实际使用情况,定时器的数量设计为256个,编号为T0~T255,其中T0~T199为通用型100 ms定时单位定时器、T200~T247为通用型10 ms定时单位定时器、T248~T251为积算型1 ms定时单位定时器、T252~T255为积算型100 ms定时单位定时器,定时设定值为18位,最大设定值为262143。假设使用100 ms为定时单位的定时器,则可定时100~218×100 ms,即最长可以实现7 h 16 min 54.3 s的定时。

为了实现PLC的定时功能,对中央控制器与定时器控制器通信的指令进行了命令字格式的设计。

2.2.1 全局复位指令

该指令由中央控制器发送,将对所有定时器进行复位,对定时器控制内所有存储的数据进行清零。指令数据格式如表3所示。

表3 全局复位指令数据格式表

2.2.2 局部复位指令

该指令由中央控制器发送,将保留每个定时器的设置值的信息,定时器的其他信息将复位至初始化结束未开始进行定时时的状态。该复位指令对积算型定时器和地址映射存储器不进行操作。指令数据格式如表4所示。

表4 局部复位指令数据格式表

2.2.3 定时器初始化指令

该指令由中央控制器发送,是PLC用户应用程序第一次编译或执行全局复位指令后发送给定时器控制器的指令,用以初始化定时器。指令数据指令入表5所示。

表5 定时器初始化指令数据格式表

2.2.4 定时器状态传送指令

该指令由中央控制器发送,是执行PLC用户程序时发送的指令,当PLC应用程序执行到某个定时器的输出指令时,将该定时器的状态信息发送给定时器控制器。指令数据指令如表6所示。

表6 定时器状态传送指令数据格式表

2.2.5 断电保存指令

该指令由中央控制器发送,用于当PLC断电时中央控制器告知定时器控制器进行断电保存,接收到该指令后定时器控制器将发送正在使用的积算型定时器的编号以及该定时器的当前值,用于保存至PLC再次通电时回传。指令数据格式如表7所示。

表7 断电保存指令数据格式表

2.2.6 通电数据回传指令

该指令由中央控制器发送,用于PLC断电后再次通电时的积算型定时器的数据回传,包括断电时正在使用的积算型定时器的定时当前值和该积算型定时器的编号,在此指令发送之前必须完成对积算型定时器的初始化。指令数据格式如表8所示。

表8 通电数据回传指令数据格式表

2.2.7 读取定时器定时当前值指令

该指令由中央控制器发送,定时器控制器接收到该指令后将上传该指令内所带定时器编号的定时器的定时当前值给中央控制器。指令数据格式如表9所示。

表9 读取定时器定时当前值指令数据格式表

2.2.8 定时器定时结束信息

该信息由定时器控制器发送,告知中央控制器该编号定时器定时结束信息。数据格式如表10所示。

表10 定时器定时结束信息数据格式表

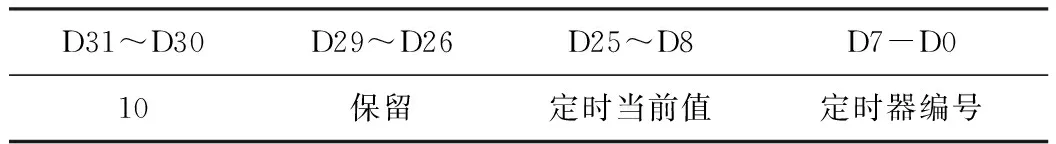

2.2.9 定时器定时当前值信息

该信息由定时器控制器发送,在接收到中央控制器读取定时器定时当前值指令后发送给中央控制器请求的定时当前值信息。数据格式如表11所示。

表11 定时器定时当前值信息数据格式表

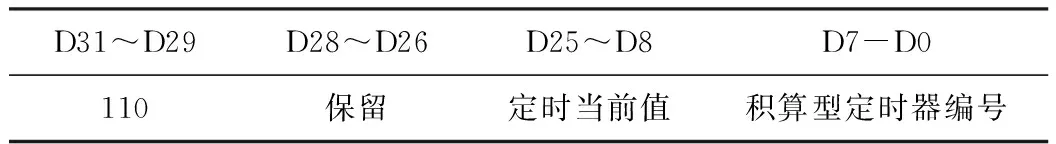

2.2.10 积算型定时器断电保存信息

该信息由定时器控制器发送,在接收到中央控制器断电保存指令后发送此信息给中央控制器,用以保存正在使用的积算型定时器的当前值及其对应的定时器编号。数据格式如表12所示。

表12 积算型定时器断电保存信息数据格式表

3 仿真测试

在使用Verilog HDL语言完成硬件描述方面的设计后,使用ModeSim软件配合编写的testbench.v文件模拟中央控制器对定时器控制器的输入,然后观察定时器控制器的输出情况[6-8]。测试方法:先使用Synplify软件综合后,再进行综合后仿真,对定时控制器和定时结果上传控制器进行测试,测试定时控制器和定时结果上传控制器是否能完成定时功能。

(a)初始化定时器指令

(b)定时器状态传送指令

(c)定时器控制器0.9 ms处输出

(d)定时器控制器1.9 ms处输出图6 定时器控制器仿真结果图

设计的定时器控制器模块地址为00100,先模拟中央控制器写入定时器初始化指令0x700001f9和0x600001fa初始化两个编号为F9H(249)和FAH(250)的积算型1ms定时单位定时器,设定编号为FAH定时器定时设定值为1 ms,寄存器D传送,设定编号为F9H定时器定时设定值为1 ms,非寄存器D传送。然后模拟中央控制器写入定时器状态传送指令0x980002f9修改定时器F9H从断电至通电并将其设定值改为2 ms,模拟中央控制器写入定时器状态传送指令0x880001fa修改定时器FAH从断电至通电。分别在0.9 ms时和1.9 ms时观察定时器控制器的输出情况,仿真结果如图6所示。

经过测试,定时结果上传控制器在0.9 ms处上传编号FAH定时器的编号至中央控制器,在1.9 ms处上传编号为F9H的定时器编号至中央控制器,证明指令执行器、定时控制器和定时结果上传控制器都能正常工作,定时误差控制在0.1 ms以内。

4 结束语

以FPGA为平台设计了一种面向PLC的定时器控制器,设计了定时器控制器与中央控制器的通信协议和指令格式。不仅能够实现定时功能,并且设计使用了地址映射存储器来存储特定编号定时器的相关数据在定时存储器中的地址,使得定时控制器的定时操作更加快速高效,能在设计的256个定时器中迅速找到被使用的定时器进行定时操作,达到了只对被使用的定时器进行定时操作,跳过未使用的定时器,从而提高定时操作效率的设计目的。

[1] 方承远,张振国.工厂电气控制技术.3版.北京:机械工业出版社,2008.

[2] 侯鸿佳,蔡启仲,陈文辉,等.ARM+FPGA组成的PLC结构的通信系统.广西工学院学报,2012,23(1):60-64.

[3] 黎娜,蔡启仲,黄捷峰.基于ARM7与FPGA组成的可编程控制器.微计算机信息,2008,24(4):54-58

[4] 张炜,李克俭,蔡启仲,等.基于FPGA的PLC并行定时器的设计.计算机工程与设计,2013,34(4):1244-1249.

[5] 李静,蔡启仲,张炜,等.基于FPGA的并行操作逻辑运算控制器设计.计算机工程与设计,2013,34(4):1244-1249.

[6] 夏宇闻.Verilog数字系统设计教程.2版.北京:北京航空航天大学出版社,2008.

[7] 孙志雄,谢海霞.基于FPGA的高速串并/并串转换器设计.现代电子技术,2014(8):151-152.

[8] 李克俭,付杰,蔡启仲,等.基于FPGA的串行定时器设计.广西工学院学报,2012,23(3):61-65.

Design of PLC Dynamic Parallel Execution Timer Based on FPGA

HUANG Shi-lin,LI Ke-jian,CAI Qi-zhong

(College of Electronic and Information Engineering,Guangxi University of Science and Technology,Liuzhou 545006,China)

PLC is internally provided with numerous timers,and usually in engineering applications only uses a part of it.Using the PLC system of ARM-FPGA architecture,we designed the FPGA timer controller’s system structure.Taking 1ms as the basic timing unit,by using the memory of address mapping,we sequentially stored the timer number that be used by PLC user program,and only the timer that be used by PLC user program can be performed the timing operation,thus improved the processing speed of PLC timing.The working principle of each function module of the timer controller,and the communication mode and the communication command between the FPGA central controller and the timer controller were described.The simulation and testing shows that the timing error is within 1ms or less,which reduces the time of PLC timer perform the timing operation and achieves the purpose of precise timing.

PLC;timer;FPGA;memory of address mapping;communication protocol

广西科学基金项目(2014GXNSFAA118392);广西教育厅科研项目(2013LX092)

2014-10-09 收修改稿日期:2015-03-28

TP332

A

1002-1841(2015)08-0057-05

黄仕林(1988—),硕士研究生,研究方向为过程控制与自动化装置。E-mail:gm2053462@aliyun.com 李克俭(1962—),教授,高级工程师,研究方向为电力电子技术与自动化装置。E-mail:lijian6262@126.com