USB2.0设备接口芯片从模式设计与实现*

金君潇,王亚军,赵琳娜,虞致国,魏敬和,顾晓峰

(1. 江南大学电子工程系轻工过程先进控制教育部重点实验室,江苏 无锡 214122;2. 中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

通用串行接口(USB)技术在计算机外围设备接口领域占据统治地位,在各种片上系统(SoC)中集成USB接口已成为趋势[1~3]。一套完善的USB设备接口芯片可为SoC提供性能优良、连接简便的接口,成为多数主流SoC平台的必备。目前USB接口的主流版本是USB2.0。USB2.0设备接口芯片负责实现外设和USB主机的通信,内置通用可编程接口和8位/16位数据总线,为外部逻辑提供简易的无胶合接口[4~5]。传统的基于USB设备芯片的数据传输由微控制器控制,而微控制器运行速度不快,限制了数据的传输速率。本文以USB2.0高速设备接口芯片8位/16位外部数据总线为基础,提出一种能够使USB设备接口芯片成为从属模式的工作机制。采用Verilog硬件描述语言设计了包括外部控制器、外部数据存储器的仿真平台,加以验证模型技术(Verification Modeling Technology,VMT)[6~8]例化主机模型作为数据发送、回读端,通过仿真验证设计的正确性。

2 从模式传输原理

一般USB设备接口芯片内置微控制器和特殊结构的缓存机构FIFO(First In First Out)参与数据的传输,外设和芯片内部总线共享FIFO缓存。若以微控制器控制FIFO的数据交互,则传输速率必然受控于微控制器的工作频率,从而限制主机与设备之间的数据传输速率。而在从模式下工作的USB设备芯片,微控制器CPU不参与数据交互,只是配置相关的寄存器。一旦寄存器配置完成,设备芯片工作在从模式下之后,外部控制器即可按照从模式的传输时序与主机进行高速通信;此时,FIFO作为数据端点缓存(EndPoint,EP)。为兼容USB2.0协议[9],设置4个EP分别为EP2、EP4、EP6、EP8,可根据需要设置其大小和缓冲空间倍数,这种配置方式为满足大容量数据传输所需的带宽提供了保证。外部控制器能对EP进行同步写、同步读、异步写、异步读4种工作模式,其中写过程是向方向设置为IN的端点写入数据,读过程是从方向设置为OUT的端点读出数据。

3 从模式模块的设计

3.1 从模式模块结构

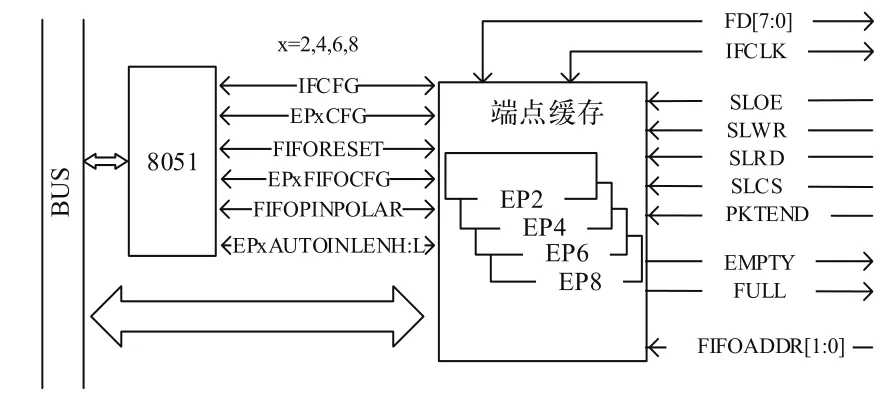

从模式模块主要分为端点缓存、微控制器8051及端点缓存的外部接口[10]。图1给出了从模式下的数据传输结构图。

图1 从模式数据传输结构图

3.2 从模块接口的设计

从模块接口用于连接端点缓存EP与外部控制器Master,接收Master发送过来的读写信号SLRD、SLWR和短包写信号PKTEND;发送端点状态信息FULL、EMPTY;接收或发送IFCLK时钟,时钟信号可选择是外部输入或内部输出;接收端点地址FIFOADDR。图1中和外部接口相关的引脚含义如下。

(1)IFCLK:作为通信的同步时钟,采样数据;(2)FD[7:0]:双向数据总线;(3)SLOE:从模块的输出使能,由Master控制,当SLOE无效时,数据线不输出有效数据;(4)SLWR:从模块写信号,由Master控制,在SLWR有效时,每个IFCLK的有效沿时数据被写入,FIFO指针递增;(5)SLRD:从模块读信号,由Master控制,在SLRD有效时,每个IFCLK的有效沿数据被读出,FIFO指针递增;(6)SLCS:FIFO的片选信号,由Master控制,当SLCS输出高时,不可进行数据传输;(7)PKTEND:包结束信号,由Master控制,在正常情况下,外部逻辑向端点缓存中写数据,当写入端点的字节数等于设定的包大小时,数据将自动被打成一包进行传输;但有时外部逻辑需要传输一个字节数小于设定包大小的包,此时它只需在写入一定数目的字节后,声明此信号,则设备芯片不管外部逻辑写入了多少字节,都自动将之打成一包进行传输;(8)EMPTY、FULL:当前EP的空、满状态;(9)FIFOADDR:选择4个端点的地址线,由Master控制。

3.3 从模式端点工作机制的设计

USB协议定义了用于发送和接收数据的设备端点EP,端点是一个用USB数据字节不断取空和填满的FIFO。根据数据的传输方向,端点可以分为OUT和IN端点,端点缓存只能单方向传输,缓存空间一共为4 K。

端点缓存与USB之间以数据包的形式进行数据交互,外部控制器可以像控制普通FIFO一样对其进行读写。端点的配置十分灵活,根据不同的带宽要求,端点可以配置成双重、三重、四重的缓存。双重缓存的含义是,USB在读取一个数据包的时候,另一个数据包可同时提供外部接口操作;三重缓存提供了另一个数据包,机动地为USB或外部接口读取;四重缓存则提供了第四个数据包存储器。

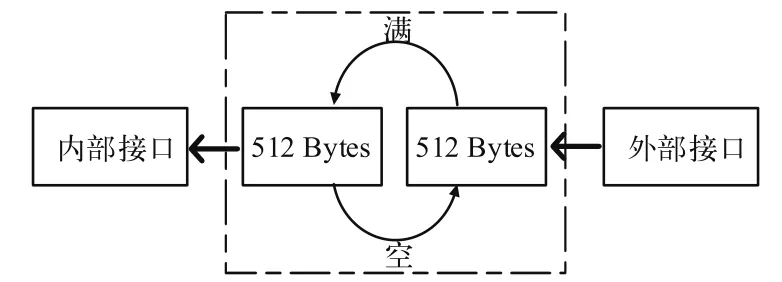

从模式读操作中只要有一个FIFO为“半满”,外部接口就可继续读取数据。当前操作的FIFO读“空”时就自动转换到USB设备芯片内部总线接口,排队等候USB接口写入数据,并将外部接口队列中为“满”的FIFO转接到外部接口上,供其继续读取。类似地,对于从模式写操作,只要有一个FIFO为“半满”,外部接口就可继续发送数据。当前操作的FIFO写“满”时就自动转换到USB设备芯片内部总线接口,排队等候USB接口读取数据,并将外部接口队列中为“空”的FIFO转接到外部接口,供其继续写入。图2以从模式写操作为例,给出了对应的双重缓存FIFO的工作机制。

图2 从模式写操作双重缓存FIFO工作机制

3.4 相关寄存器的设计

将I/O口设为从模式接口、外部逻辑经数据总线FD连接端点缓存,FD为双向接口,由SLOE引脚控制输出,设置端点大小和缓存倍数并复位端点,并且设置数据传输长度大小。从模式8位数据同步读写配置如下。

(1)IFCLK:配置接口为同步从模式接口,时钟IFCLK为输入;(2)EPxCFG:配置EP2、EP4为双缓冲的512 B的OUT端点,配置EP6、EP8为双缓冲的512 B的IN端点;(3)FIFORESET:将EP复位到初始状态;(4)EPxFIFOCFG:配置EP2、EP4为8 bit传输自动读出的FIFO;配置EP6、EP8为8 bit传输自动写入的FIFO;(5)FIFOPINPOLAR:配置使能信号SLOE、SLWR、SLRD、PKTEND、SLCS和状态标志EMPTY、FULL为低有效。(6)EPxAUTOINLENH:L:设置IN端点的传输长度为512 B。

以8051作为微控制器参与寄存器的配置。配置文件Hex文件,经过External ROM读入8051微控制器,为端点传输相关的一些寄存器赋值。

4 仿真平台设计

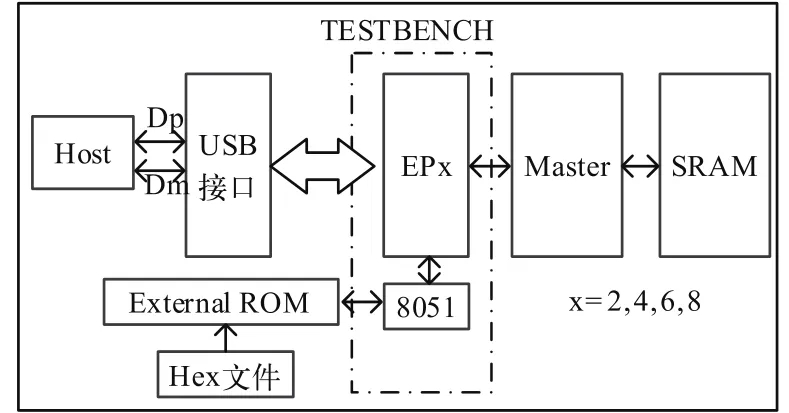

为了验证设计的外部控制器对USB数据读写的功能,在LINUX系统上,以Verilog硬件描述语言为开发语言,以Synopsys的VCS软件为仿真工具,搭建了如图3所示的仿真环境。仿真环境包括外部控制器Master、外部数据存储器SRAM、端点缓存EPx、8051微控制器、外部程序存储器External ROM、串行接口引擎(Serial Interface Engine,SIE)、USB物理层(Physical Layer,PHY)、USB主机Host。

图3 外部控制器的仿真环境

4.1 数据传输机制

(1)Host利用DesignWare库中的usb_host_vmt[6]模型例化而来,该模型能以USB传输包的形式传输数据,并能打印回读数据,方便数据的一致性检测;Host作为数据发送端和接收端。(2)USB接口作为EPx和Host之间的数据接口,能够对主机发送的数据进行解码、位剔除、串并转换等操作,将数据输入OUT端点中;或者对IN端点中的数据进行并串转换、位填充、编码等操作,将数据发送到Host端。(3)外部读写控制器Master产生读写状态机,用于将数据从OUT端点中读出并写入到SRAM中,再从SRAM中将数据读回写入IN端点中。(4)SRAM只作为数据的中转站用于存储数据,与外部读写控制器相连。SRAM接口有地址线A8~A0、数据线D15~D0、控制线包括芯片使能、输出使能、写使能,高字节使能信号UB、低字节使能信号LB。

4.2 Master工作机制

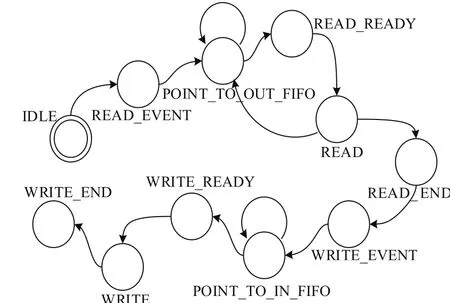

外部控制器Master的核心是一个状态机,完成对EPx空满的判断、读写使能、EPx地址选择、数据传输方向设置等功能。图4所示为数据总线宽度为8 bit的同步读写状态机,共11种状态,描述如下。

I D L E:当有读事件发生时,转到状态READ_EVENT;READ_EVENT:设置OUT端点地址,初始化SRAM地址,转到状态POINT_TO_OUT_FIFO;POINT_TO_OUT_FIFO:使能SLOE(低电平有效),如果EMPTY(低电平有效)信号为高,则转到状态D A T A_R E A D Y,否则停在状态使能SLRD,使能,SRAM地址加1,并将数据读入SRAM,转到状态READ;READ:不使能SLRD,不使能信号,判断EMPTY信号,若还有数据要读,则返回状态POINT_TO_OUT_FIFO,若没有则转到状态READ_END;READ_END:初始化端点地址,初始化SRAM地址,不使能信号SLWR(低电平有效)、SLRD、SLOE,转到状态WRITE_EVENT;WRITE_EVENT:写事件发生,设置IN端点,转到状态POINT_TO_IN_FIFO;POINT_TO_IN_FIFO:判断FULL信号(低电平有效),如果为高,转到状态W R I T E_R E A D Y,否则停留在状态POINT_TO_IN_FIFO;WRITE_READY:使能SLWR,不使能信号,SRAM地址加1,转到状态WRITE;WRITE:不使能SLWR,判断EMPTY信号,若还有数据要读,则返回状态POINT_TO_IN_FIFO,若没有则转到状态WRITE_END;WRITE_END:初始化SRAM地址,转到状态IDLE;DEFAULT:默认状态为IDLE。

图4 外部控制器工作状态机

整个状态机能够实现将主机发送到OUT端点的数据读出到外部数据存储器,再从外部数据存储器写入到IN端点,供主机回读数据。主机可根据回读数据和原始发送数据的对比,验证状态机是否正常工作。

5 仿真结果及分析

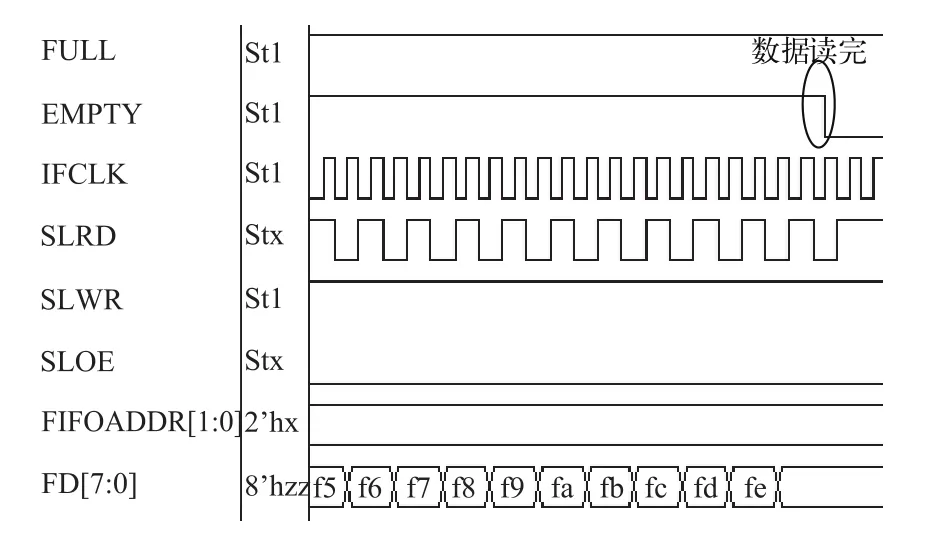

从模式同步读的仿真结果如图5所示。FIFOADDR[1:0]为01,表示参与传输的FIFO为EP4,IFCLK为48 MHz的外部时钟输入,下降沿有效,SLOE置低,表示FD[7:0]数据输出到外部控制器中。SLRD置低时读一个字节数据,读完一个字节则SLRD置高,以此类推读完512 byte数据。在读完所有数据之后,EMPTY置低,表示EP2内已无数据可读。

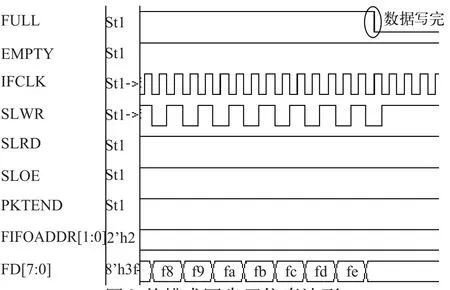

从模式同步写的仿真结果如图6所示。FIFOADDR[1:0]为10,表示参与传输的FIFO为EP6,IFCLK为48 MHz的外部时钟输入,下降沿有效,SLOE置高,表示FD[7:0]数据从外部控制器输出。SLWR置低时读一个字节数据,写完一个字节则SLWR置高,以此类推写完512 bytes数据,并在写入最后一个数据后,FULL置低。

图5 从模式同步读仿真波形

图6 从模式同步写仿真波形

由仿真波形可算出,IFCLK的频率为48 MHz,每两个IFCLK时钟周期写1 byte(即8 bit)数据,因此可得出数据传输速率为96 Mb/s,和其他总线如400 kb/s~3.4 Mb/s的IIC、1.5 Mb/s的UART等相比,传输速率有显著的提高。

6 结束语

设计实现了基于USB2.0设备芯片的从模式数据传输方式,并以Host为主机模型、外部SRAM为设备模型仿真验证了该模式的可行性。在从模式下,USB设备芯片能为ATA、UTOPIA、EPP等主流接口和大多数DSP提供简易的无胶合接口,并且数据传输过程不经过微控制器控制,显著提高了数据传输速率。

[1] 杨晓光. 基于通用串行总线和有限状态机的数据发送系统设计[J]. 微电子学与计算机,2010,27(4): 162-164.

[2] 胡锦,胡立琴,陈训亮. 一种嵌入式USB2.0主机控制器IP核的研究与设计[J]. 微电子学与计算机,2009,26,(1): 133-136.

[3] 冯祎,吴超,王景中. 基于Slave FIFO 模式的CMOS摄像头接口设计[J]. 电子测试,2013,(6): 8-9,14.

[4] 王荣博,侯朝焕,陈栋,等. 基于EZ-USB FX2LP的高速数据传输接口设计[J]. 电子测量技术,2009,32(4):167-170.

[5] 刘春雅,程旭,赵辉昌. 基于FPGA的数据采集系统的设计与实现[J]. 电子设计工程,2011,19(1): 50-54,61.

[6] Synopsys. USB on-the-go verification IP VMT user manual[EB/OL]. [2013-07-10]. http://solvnet.synopsys.com/portal/dt.

[7] 刘蕊. 基于VMM验证方法学的USB控制器IP验证方案[J].信息通信,2012,3: 286-288.

[8] 高夫,杜学亮,金西. 基于VMT的DDR-SDRAM控制器功能验证[J]. 计算机工程,2008,34(4): 263-265,274.

[9] Compaq. Universal serial bus specification revision 2.0[S].USA: Compaq Computer Corp : 2000.

[10] Cypress. EZ-USB technical reference manual[EB/OL].[2013-06-07]. http://www.cypress.com/?docID=48811.