电力系统无线通信中的低复杂度Rake接收机

许知博,黄少伟,杨云涛

(1. 陕西省地方电力(集团)有限公司, 陕西 西安 710061;2. 清华大学 电机系电力系统国家重点实验室, 北京 100084)

电力系统无线通信中的低复杂度Rake接收机

许知博1,黄少伟2,杨云涛1

(1. 陕西省地方电力(集团)有限公司, 陕西 西安 710061;2. 清华大学 电机系电力系统国家重点实验室, 北京 100084)

针对电力系统中高速无线通信,提出了一种分级式Rake接收机架构,有效节约了硬件资源,避免了布线拥塞。基于该推荐架构,实现了一种8路并行8指Rake接收机。在SMIC.18 CMOS工艺下,该Rake接收机相对于传统方案获得了13.1%芯片面积和37.2%布线网络的节约。

Rake接收机;电力系统;无线通信;布线拥塞

因铺设简单、运行成本低等特点,监测数据传输无线化已成为电力系统发展的必然趋势[1]。作为第二代移动通信核心技术,通用分组无线服务技术(GPRS)首先被应用到了电力系统通信[2]。但是,由于受到数据吞吐率的限制,已不能满足电力系统测量、监管等大数据的传输需求。目前,全球微波互联接入技术(WiMAX)[3]、无线传感网络[4]、超宽带无线通信[5]等新型高速通信技术正被推广到电力系统通信中来。然而,上述的研究主要集中在技术体制的评估,并没有基于电力系统通信的具体特点对已有技术进行优化。事实上,由于电力系统通信网络需要长时间运行,降低接收机复杂度可有效延长电池供电检测结点的运行时间。因此,本文旨在研究电力系统无线通信中低复杂度Rake接收机的设计。

由于可以捕获更多能量并且不敏感于定时误差,高速无线通信系统采用高分辨率的Rake接收机来获得优异的接收性能。然而,高分辨率的Rake接收机需要花费大量的移位寄存器、多路选择器资源来实现多径选择。在长扩展延迟信道[6-7]中,高分辨率的Rake接收机需要数百个移位寄存器组来确保所有的多径元素被收集。但是,在高吞吐率无线通信系统中,移位寄存器和多路选择器之间复杂的布线网络会导致严重的布线拥塞,甚至导致布线不收敛[8-9]。因此,降低Rake接收机的布线复杂度,对于避免布线拥塞、节约硬件资源和降低功耗有着显著意义。

1 Rake接收原理

Rake接收机是一种多径分集合并接收技术,可以在时间上分辨出细微的多径信号,并对这些分辨出来的多径信号分别进行延时和相位校正,在某一时刻对齐、加权调整,进而消除码间串扰,获得信道分集增益[10]。Rake接收时,输入信号与主径和选定的次径分别进行相关运算,并对相关值按照最大比合并,根据合并结果进行数据恢复[8]。

假定A表示信号幅度,扩频调制的发送信号可以表示为

(1)

式中:s(t)表示用户信息符号序列xi扩频后的发射信号;Tf是脉冲重复周期;w(t)是由Ns个脉冲构成长度为Ts=NsTf的扩频波形,可表示为

(2)

式中:αk为扩频序列;δ(t)表示单位脉冲响应。在接收端,受到多径响应和噪声的影响,接收信号表示为

(3)

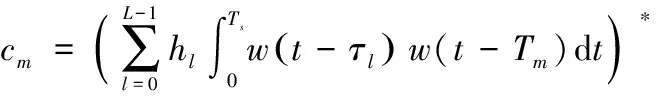

式中:L是信道中多径分量的数目;hl和τl表示第l条径的增益系数和各径到达时延;n(t)是单边功率谱密度为N0的加性白高斯噪声。Rake接收机的每一条支路由一个相关器组成,实现与不同延迟下的扩频波形w(t)的相关。在路径延迟为Tm下,第m指相关后的结果表示为

(4)

在jTs时刻,对相关器的输出采样,扩频序列移位正交下有

(5)

(6)

对于高速无线通信系统而言,采样速率往往达到吉赫兹量级时,硬件电路单路处理模式往往无法满足如此高的系统工作时钟。M路并行处理模式的Rake接收机,可以有效地并行处理各径上的数据,在不提高系统工作时钟的前提下,获得M倍于单路处理模式的数据吞吐量[9]。

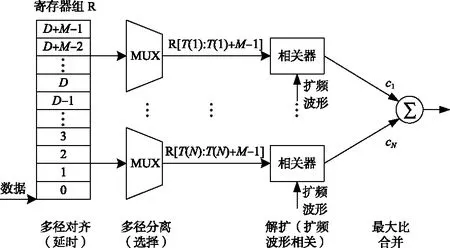

假定Rake接收机指数为N,扩频因子为J,最大路径延迟为D个采样时钟,过采样倍数为K,并行输入采样点路数为M,且M是K的整数倍,第m指的离散路径延迟为T(m)。传统Rake接收机首先将采样数据输入至移位寄存器组中进行多径延时对齐,因此移位寄存器的深度为D+M;接着,采用多路选择器进行多径选择,以分离出各个Rake指上的接收波形,由于一个时钟处理M个采样点,所以每个支需要M个D选1多路选择器,以选出M个波形;然后,在每个Rake指上进行扩频相关,由于每时钟处理M个采样点,因此J×K/M个时钟周期完成一次解扩;最后,将各个Rake指上解扩所得信号进行最大比合并,得到最终Rake输出。以N指传统Rake接收机为例,其结构如图1所示。

图1 传统N指Rake接收机结构

传统Rake接收机的设计思路简单,但其需要的寄存器资源、多路选择器资源以及连线资源过大。由于数据都来自相同的寄存器缓存,这将导致布线拥塞、路径延迟激增,进而降低系统工作时钟[8-9]。

2 分级式Rake接收机

本文提出了一种分级式Rake接收机结构,将多径对齐、多径分离及解扩均拆分成两级进行。一方面,由于整个系统是线性系统,因此扩频波形w(t)相关处理可以拆分成与δ(t)的波形匹配和与αk的序列相关两级;另一方面,多径对齐与多径分离根据每个时钟处理并行输入的采样点数分成了分数倍和整数倍两级,详细结构图如图2所示。

图2 分级式N指Rake接收机结构

首先,对采样数据进行基于FIR模式的波形匹配,这样可以有效节约各个相关器都做波形匹配消耗的逻辑资源。

第一级多径对齐分离,进行小数倍离散路径延迟(相对于Rake接收机系统时钟)的对齐与分离。由于每时钟有并行M路输入,因此小数倍延迟有M个不同的离散延迟,由离散路径延迟T(m)的低L位(L=「lbM⎤)表示。波形匹配之后,每个Rake指每个时钟周期只需要抽取出M/K个数据进行解扩,因此,所需最大寄存器深度仅为2M-K个,多路选择器也仅需M/K个M选1。

第二级多径对齐分离,进行整数倍离散路径延迟(相对于Rake接收机系统时钟)的对齐与分离,由于整数倍离散路径延迟由T(m)的高G位(即减去L的剩余位数,G=「lb(D/M)⎤)表示,与上一步类似处理最终选取出各指对应的扩频序列,所需的最大寄存器深度为M/K×2G,每指仅需M/K个2G选1的多路选择器。

最后,将各个Rake指序列相关所得的信号进行最大比合并,各指信号与相应的扩频序列完成乘加运算。各径得到的数值,与信道估计获得的各径信道冲激响应幅值相乘,最终通过累加器完成N径数据的累积运算,最终得到Rake接收机输出。

不同于传统Rake接收机设计方案,分级式Rake接收机将多径分离和多径对齐分成了整数倍多径分离、多径对齐和小数倍多径分离、多径对齐两部分来实现;同时,扩频波形相关处理拆分成波形匹配与序列相关两级。因此,该推荐结构与传统Rake接收机相比,可以大幅度地减少寄存器和多路选择器资源的使用,较好地减小系统综合时出现的布线拥塞、路径延迟激增的问题,提高系统的工作时钟。

3 实现与分析

针对高吞吐率无线通信系统,本文设计了一种8指分级式Rake接收机,过采样倍数为4、扩频因子为8、并行输入路数为8路以及最大路径延迟为127个采样时钟。Rake的输入数据采样率为1 Gsample/s(采样值/s),以125 MHz系统时钟频率、8路并行的方式输入,输出符号速率为31.25 Msample/s。

基于Verilog HDL语言,本文完成分级式Rake接收机的实现,其原理框图如图3所示。首先,对输入的采样数据进行基于FIR模式的波形匹配,需要8路并行4阶匹配滤波器。之后,多径对齐与多径分离根据每个时钟处理的采样点数(8个点)分成了两级。第一级进行小数倍离散路径延迟(相对于125 MHz系统时钟)的对齐与分离。由于每时钟有并行8路输入,因此小数倍延迟有8个不同的离散延迟,由离散路径延迟T(m)低3位表示。每个时钟周期Rake每指需要抽取2个数据进行解扩,因此,所需的寄存器深度仅为12,多路选择器也仅需2个8选1。第二级进行整数倍离散路径延迟(相对于125 MHz系统时钟)的对齐与分离,由离散路径延迟T(m)高4位表示。然后,解扩系列相关阶数为2,每4个时钟周期完成一次序列相关。最后将各个Rake指上相关所得的信号进行最大比合并,得到最终输出。

图3 推荐分级式8指Rake接收机结构

传统结构和推荐分级式Rake接收机的误码率性能进行ModelSim RTL级仿真验证。信道选用超宽带CM2信道[5,7],并且一个突发包中信道响应保持不变。在BPSK、QPSK调制下,误码率仿真结果如图4所示。仿真曲线表明,推荐的分级式Rake接收机可以获得和传统结构基本相同的误码率性能,验证了推荐结构的有效性。

传统结构与分级式Rake接收的复杂度评估,如表1所示。考虑到有I、Q两路信号,传统Rake结构需要寄存器(135+32×8)×2=782个,而分级式Rake结构需要寄存器(11+12+32×8+8×8)×2=686个;传统Rake结构需要128选1多路选择器8×8×2=128个,对应128×(128-1)=16 256个2选1多路选择器,而分级式Rake结构需要8选1多路选择器2×8×2=32个和16选1多路选择器为2×8×2=32个,对应32×(8-1+16-1)=704个2选1多路选择器;最后传统Rake结构需要乘法器2×8×8+16=144个,而分级式Rake结构需要乘法器为2×8×4+16=80个。分析结果表明,推荐分级式Rake的寄存器略低于传统Rake,但是多路选择器、乘法器资源则大大降低。

图4 误码率性能比较

表1 资源复杂度对比

最后,基于SMIC 180 nm CMOS工艺,供电电压为1.2 V,系统时钟约束125 MHz,本文完成了该分级式Rake接收机ASIC实现。DC compiler门级综合工具给出了芯片的芯片面积及布线网络综合报告。与传统Rake接收机进行比较,结果如表2所示。该推荐的分级式Rake接收机可以节约13.1%的芯片面积。更为重要的是,该推荐结构的布线网络数下降了37.2%。在布线阶段,对于传统Rake接收机面临的严重的布线拥塞问题被有效解决。

表2 芯片面积和布线网络的比较

4 小结

针对电力系统中的高速无线通信,本文提出了一种高速低复杂度分级式Rake接收机架构,将多径分离和多径对齐分成了整数倍多径分离、多径对齐和小数倍多径分离、多径对齐两部分来实现,并将扩频波形相关处理拆分成波形匹配与序列相关两级。与传统Rake接收机相比,该推荐结构大幅度地减少了寄存器和多路选择器的使用,避免布线拥塞和路径延迟激增。其在SMIC.18 CMOS工艺下的实现结果表明,该Rake接收机相对于传统方案获得了13.1%芯片面积和37.2%布线网络的节约。因此,该推荐的分级式Rake接收机架构在高吞吐率扩频接收机领域有着广阔的应用前景。

[1]谢波,王世文,刘永辉. 基于IP over SDH河南电力调度数据网规划及互联[J]. 电视技术, 2012, 36(6): 36-39.

[2]王伟杰, 闫永巍, 王飞. 太阳能无线电力线覆冰监测系统研究[J]. 传感器与微系统, 2009, 28(11): 22-24.

[3]陈蕾. WiMAX技术及其在电力系统通信中的应用[J]. 电力系统通信, 2007, 28(7): 46-48.

[4]孙晓雅,李永倩,李天. 无线传感器网络在电力系统中的应用[J]. 传感器与微系统, 2012, 31(6): 5-7.

[5] ECMA-368,High rate ultra wideband PHY and MAC standard[S]. 2005.

[6]任景英,郝双洋,赵红梅. 超宽带室内信道测量及数据处理技术研究[J]. 电视技术, 2013, 37(13): 131-134.

[7]MOLISCH A F. Ultra wideband propagation channels-theory, measurement, and modeling[J]. IEEE Trans. Vehicular Technology, 2005, 54(5): 1528-1545.

[8]HARJU L, KUULUSA M, NURMI J. Flexible implementation of a WCDMA Rake receiver[C]//Proc. IEEE Workshop on Signal Processing Systems.[S. l.]: IEEE Press,2002: 177-182.

[9]KOUSO M. Enhancement of RAKE receivers for ultra-wideband reception[J]. IET Communications, 2008, 2(3): 421-431.

[10]姚尚绩, 郑飞. 超宽带Rake接收机结构的研究[J]. 电子技术应用, 2012, 34(8): 122-125.

许知博(1986— ),硕士,助理工程师,从事电力通信与信息系统技术研究工作;

黄少伟(1985— ),博士,助理研究员,主研电力系统并行仿真与分布式计算、微电网、智能配电网;

杨云涛(1983— ),博士,工程师,主要从事配电网通信与信息系统技术研究与应用工作。

责任编辑:薛 京

Low-complexity Rake Receiver for Wireless Communications in Electronic Power Systems

XU Zhibo1, HUANG Shaowei2, YANG Yuntao1

(1.ShaanxiRegionalElectricPowerGroupCo.,Ltd.,Xi’an710061,China; 2.StateKeyLabofPowerSystems,DepartmentofElectricalEngineering,TsinghuaUniversity,Beijing100084,China)

In this paper, a novel multi-layer Rake receiver architecture is proposed for high data rate wireless communications in the electronic power system, which efficiently saves hardware resource and avoids routing congestion. According to the proposed architecture, a parallel-8 figure-8 multi-layer Rake receiver is designed. In SMIC.18 CMOS technology, the Rake receiver achieves a reduction of 13.1% cell area and 37.2% routed nets, compared with the traditional scheme.

Rake receiver; electronic power systems; wireless communications; routing congestion

国家自然科学基金项目(51277104)

TN914.4

A

10.16280/j.videoe.2015.01.018

2014-06-10

【本文献信息】许知博,黄少伟,杨云涛.电力系统无线通信中的低复杂度Rake接收机[J].电视技术,2015,39(1).