基于商业零中频芯片的BPSK/QPSK解调器设计

邓元策,陈巧艳,马 路,石立国,王竹刚

(1. 中国科学院大学,北京 100190;2.中国科学院 空间科学与应用研究中心,北京 100190)

基于商业零中频芯片的BPSK/QPSK解调器设计

邓元策1,2,陈巧艳2,马 路1,2,石立国1,2,王竹刚2

(1. 中国科学院大学,北京 100190;2.中国科学院 空间科学与应用研究中心,北京 100190)

提出基于商业零中频芯片MAX2837的BPSK/QPSK解调器设计,详细分析了零中频芯片MAX2837的特性、AGC环路、载波同步及位同步环路的设计。工程实测结果表明:该系统在误比特率为10-5时,解调损耗约2.5 dB,完成系统设计要求;该系统集成度高、体积小、重量轻、成本低。

零中频;MAX2837;BPSK/QPSK解调器

零中频接收机直接将射频信号下变频到基带信号进行处理,不需要中频放大、高Q值镜像频率滤波器等结构,使其接收系统的数字集成度提高,既简化了设计,又减小了接收设备的体积和成本,越来越受到军用和民用通信的青睐。但是零中频结构接收机由于直接将信号搬移到基带也有它固有的缺陷,如I/Q 不平衡、直流偏移、偶次谐波、闪烁噪声等问题。文献[1-3]分别从时域补偿的角度、正交相移混频拓扑和基于查找表的数字域补偿的角度对I/Q不平衡问题进行了改善。关于零中频接收机中由“本振泄漏自混频”和“干扰自混频”引起的直流偏移问题的解决办法在文献[4-5]有相应的讨论和对比。文献[6]讨论了零中频结构在数字电视接收机系统中应用。实践表明利用商业零中频芯片的高集成度、可靠性强、可在线灵活配置的优点,使得研发设备体积小、重量轻、功耗低的同时简化了设计,缩短了研发周期,实际研制系统已应用于探空火箭高速数据传输链路的地面接收设备中。

1 系统构架及设计指标

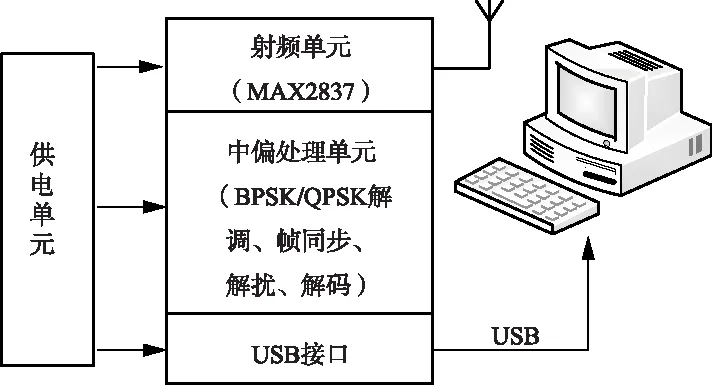

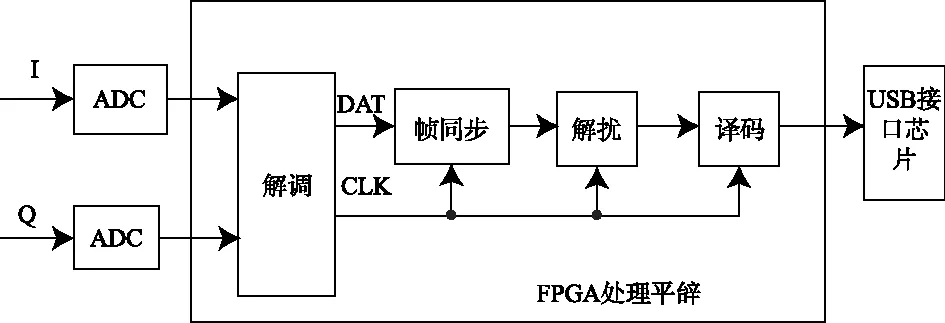

文中设计的BPSK/QPSK解调器主要需要完成对BPSK/QPSK信号的解调、帧同步、解扰、RS解码以及和后续终端之间的接口。其系统框图如图1所示,系统包括了射频单元、中频单元、USB接口和电源4个部分。其中射频单元接收来自天线的射频信号,完成下变频到零中频,并且完成I/Q不平衡补偿、中频AD输出。中频处理单元除了完成常规的解调任务之外,还需完成帧同步、解扰和解码的功能,其功能框图如图2所示。解调器需完成2.048 Mbit/s的BPSK信号、10 Mbit/s的QPSK信号和4.096 Mbit/s的QPSK信号的解调,且要求在10-5误码率的情况下,解调损耗小于3 dB。

图1 系统框图

图2 中频处理单元功能框图

2 MAX2837简介

MAX2837零中频射频收发器设计用于2.3 ~2.7 GHz无线宽带系统中。在芯片内部集成实现RF发送器功能所需的全部电路,提供射频至基带接收通道、基带至射频发送通道、压控振荡器(VCO)、频率合成器、晶体振荡器和基带/控制接口。器件包含具有快速建立时间的∑-Δ射频合成器,具有小于20 Hz的频率步长的振荡器,允许使用低成本的晶体代替高成本的温度补偿晶振(TCXO)。该收发器IC还集成了片上DC偏移消除和I/Q不平衡误差检测电路以及载波泄漏检测电路。其丰富的内部结构使得只需要几个简单的外围元件即可以组成一个完整的无线宽带射频收发器。MAX2837为接收器和发送器集成了完整的片上滤波器,完全无需外部SAW滤波器。Rx和Tx信号通道上的基带滤波器已经按严格的噪声系数和线性度指标进行了优化。该器件支持高达2048 FFT的OFDM,并且可为1.75~28 MHz射频带宽提供可配置的信道滤波器。其收发器在发送和接收之间的切换时间仅需2 μs,并且已经包括频率瞬态建立时间[7]。

如图3所示,MAX2837内部集成了DC偏移消除、I/Q误差检测以、载波泄漏检测、幅度检测、抗混叠滤波、温度补偿接口等电路,所以使用MAX2837作为零中频射频单元不需要在外部设计额外直流偏移、I/Q支路不平衡专用处理电路,并且该芯片对外提供了标准的串行配置接口(SPI),可以大大简化了后续处理单元的结构和成本,是非常经济而且可靠的射频解决方案。

3 BPSK/QPSK解调器设计

模拟的零中频信号经过ADC采样,由FPGA进行数字信号处理。BPSK/QPSK的解调器主要包含了AGC、载波跟踪环路以及位同步环路。整个解调器的功能框图如图4所示。图中的AGC输出的增益控制字由SPI配置接口写入到MAX2837的增益控制寄存器中,以此来控制信号输入的幅度。判决输出模块输出的比特流接入到后续的帧同步模块完成帧同步。位同步模块输出了I/Q数据信号和两个同步后输出的参考时钟。其中载波恢复和位同步分别采用了零中频特有的交叉鉴相器和数据转换跟踪环结构。

图3 MAX2837内部框图(截图)

图4 BPSK/QPSK解调器功能框图

3.1 数字AGC设计

数字AGC是数字中频接收机的重要辅助电路[8],数字中频接收机设置自动增益控制的目的在于使接收机的增益随着信号的强弱进行调整,或者保持接收机的输出恒定在一定的范围[9]。本文讨论的AGC属于前一种在接收机输入端的数字AGC设计,它的作用是保证输入信号幅度在一定范围之内,即在信号幅度较弱的时候提高接收机的增益,使得信噪比提高,在接收到强信号时使接收机工作在正常范围之内(保证A/D转换器不会溢出)。本方案中,数字AGC采用了非相干反馈形式,其框图如图5所示。图中的Z-1模块为单位延迟模块,Σ模块为累加模块。可以看出AGC首先对输入的I/Q信号进行平方运算,经过累积之后,和基准信号比较输出差值进行累加,最后将差值累加的结果转换成MAX2837中增益寄存器的控制字。

图5 数字AGC功能结构框图

(1)

由文献[9]中可得到其概率密度函数的详细表达式,其期望、方差和偏度的表达式为

E[Y]=2N+2Nγ

(2)

Var[Y]=4N+8Nγ

(3)

(4)

而如果图5中①点处的信号表示为随机过程X,则③点处的信号表达式Y′和上文中的随机变量Y的关系为

Y′=σ2Y

(5)

得出相应的期望和方差的表达式为

E[Y′]=2N(σ2+μ2)

(6)

Var[Y′]=4Nσ4+8Nσ2μ2

(7)

当自由度2N和λ较大时(信噪比较大),非中心带参数λ的卡方亦趋近于正态分布N(E[Y′],Var[Y′]),使用3Sigma原则有

(8)

所以相对于AGC环路的理想信号的波动幅度可以表示为

(9)

由式(5)~式(9)可知,当信噪比较大时AGC调节的能量累积部分的输出范围和累积次数的关系如式(9)所示。当信号AGC的调节范围在如式(9)所示的比例范围内时,环路才是稳定的。当信噪比较低时,应按文献[9]中给出的累积分布函数,利用式(1)~式(4)求得在均值附近所需的动态范围内的取值,然后由式(5)反解出累积门限,最后求得累积次数。

3.2 载波跟踪设计

因为接收机的晶振频偏和发射信号的多普勒频移以及多普勒频移的变化,所以MAX2837中的下变频器后ADC采样的输出的零中频信号,实际上还是有一定频偏的。需要用载波跟踪环来将剩余的频偏纠正过来。载波同步算法采用常规的Costas形式的锁相结构。但因为输入信号为零中频信号,与本地载波相乘之后的倍频项无法采用低通滤波器滤除,因此需采用交叉结构的零中频复数鉴相器来完成复数鉴相,其结构如图6所示。

图 6 QPSK/BPSK零中频复数鉴相器结构

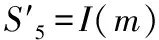

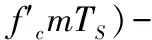

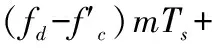

图6中的⑧点处的切换开关是对QPSK和BPSK的区分,当切换开关闭合的时候,图6构成的是QPSK的零中频复数鉴相器;当其断开时,构成了BPSK的鉴相结构。当作为BPSK鉴相器的时候,设信号I,Q输入信号为

I(m)=A·D·cos(2πfdmTs+φ0)+n1(mTs)

(10)

Q(m)=A·D·sin(2πfdmTs+φ0)+nQ(mTs)

(11)

式中:D表示调制符号,取值为{1,-1};A,fd,φ0和Ts分别表示信号的幅度、发送载波频偏、载波初始相位和采样间隔。所以⑥点和⑤点处的信号表达式分别为

(12)

(13)

(14)

由上式可以得到BPSK的鉴相增益。当图6所示鉴相结构作为QPSK的鉴相器时,令I,Q路输入信号分别为

XI(m)=I(m)sin(φ(m))+Q(m)cos(φ(m))

(15)

XQ(m)=I(m)cos(φ(m))-Q(m)sin(φ(m))

(16)

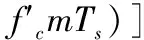

为了讨论方便,使用φ代替φ(m)且I,Q路信号用简略表达式表示,由图中所示结构得此时⑤,⑥处的信号表达式分别为

Phq(m)=I(m)cos(θ)+Q(m)sin(θ)

(17)

Phi(m)=-I(m)sin(θ)+Q(m)cos(θ)

(18)

式中:θ表示本地载波和接收信号载波的相位差。又当进入跟踪状态,θ很小的时候,有sgn(Phq(m))≈I(m)且sgn(Phi(m))≈Q(m),所以⑦,⑧点的信号为

sgn(Phi(m))·phq(m)≈I(m)Q(m)cosθ+sinθ

(19)

sgn(Phq(m))·phi(m)≈I(m)Q(m)cosθ-sinθ

(20)

因此,⑨点的相差输出为

Δθ≈2sinθ

(21)

综上对BPSK和QPSK鉴相器的讨论,可以得到相应的鉴相增益。本方案中的环路滤波器的设计,采用一阶环路滤波器,二阶锁相环的形式,其数字实现结构如图7所示。

图 7 载波跟踪环路滤波器实现结构

从图7可以看出环路滤波器的主要设计工作就是确定两个环路滤波器的增益参数。在g2支路的累加中加入了限幅器是因为当没有信号进入环路的时候,高斯白噪声进入环路滤波器,高斯白噪声经过积分之后成为了维纳过程也就是布朗运动,所以有可能使得初始的频差游离到捕获带以外去,致使信号进入的时候不能入锁。环路滤波器的两个系数可表示为

(22)

(23)

式中:T为采样率;ωn为二阶环路的自由振荡频率;K为环路增益,其中包含了鉴相增益和NCO的增益。

3.3 位同步设计

位同步环路采用了数据转换跟踪环路(DTTL)结构,其设计结构亦可以等效为一个锁相环的结构。两者的差别唯有鉴相器输入输出的物理量不同,前者输入输出的物理量是相位,而后者是时间。但是另一方面,通过式(24)这种简单的比例关系即可将时间误差亦可以等效为相位的误差,所以两者的设计思路基本是一致的。

(24)

式中:εθ,ετ和Tc分别表示相位误差、时间误差和基带数据周期。位同步环的设计应在满足环路的稳定性条件,尽可能提高环路进入锁定的时间,同时兼顾一些位同步的精确度要求。环路的稳定性条件一般认为是环路的最大抖动(4σ~6σ环路定时误差ετ)小于半个码元周期。在本项目中,采用的环路带宽的主要设计目标是让任务书规定的最大频差在位同步环路的快捕带内,该环路带宽远小于稳定性要求所规定的环路带宽。

4 Simulink仿真实现及验证

利用Simulink搭建了BPSK/QPSK的仿真模型,其中主要的载波同步环路如图8所示,位同步环路如图9所示。载波环路采用了Costas环结构,其中的鉴相器结构在第3.2节已有说明,位同步环路采用DTTL环路。

样本数量为107级,载波频偏为3.2 kHz的情况下,各种调制制式的误码情况如表1所示,符号“—”表示在样本量中没有出现误码。

图 8 载波跟踪环路Simulink模型

图 9 位同步环路Simulink模型

5 实测性能

本文所述BPSK/QPSK解调器已用于探空火箭高速数据传输链路的地面接收设备中,其工程实物图如图10所示,MAX2837输出的正交零中频信号,经过双路ADC采样,由Xilinx Spartan6 XC6SLX16 FPGA进行后续处理。FPGA完成所有解调、帧同步、解扰、解交织和RS译码以及通过USB接口芯片输出的工作,占用了78%的Slice资源。在项目中的实测误码结果和理论误码曲线的对比如图11所示。从图中可以看出在10-5误码率附近,该解调器的解调损耗为约2.5 dB,满足设计指标的要求。

6 结论

本文总结了基于商业零中频芯片MAX2837和FPGA的BPSK/QPSK解调算法的设计,详细分析了AGC环路、载波恢复以及定时环路的设计,给出了仿真和工程实测结果,该解调器具有成本低、结构简单的特点同时大大降低了设备的体积、重量、功耗。该调制器已经被应用到探空火箭高速数传链路的地面接收设备的研制中。文中所采用的零中频载波跟踪算法经过适当改造,可以推广到任意正交调制体制信号的解调。这种基于零中频结构的接收机,集成度高、体积小、重量轻、功耗低,在军用和民用领域都具有很高的推广价值。

图10 BPSK/QPSK解调器实物图

[1]唐世刚,龚克,潘长勇,等. 数字接收机I/Q支路不平衡的时域补偿[J]. 清华大学学报:自然科学版,2007(1): 49-52.

图11 测试误码曲线和理论误码曲线比较

[2]徐建,吴建辉,时龙兴,等. 双正交零中频接收机拓扑结构设计[J]. 电路与系统学报, 2000(2): 78-81.

[3]邹世源,刘久文,阳辉. 数字域校正零中频发射机IQ不平衡的研究[J].电视技术,2013,37(23): 163-166.

[4]唐琴,吴建辉. 零中频直流偏移消除技术比较与分析[J]. 微电子学,2008(6): 811-81.

[5]胡雪惠,白献林,雷梁. 零中频接收机中的直流偏移抑制技术[J]. 空间电子技术, 2008(3): 48-50.

[6]杨霏,杨刚. 基于零中频结构的数字电视调制系统研究[J].电视技术,2011,35(12): 25-27.

[7]Inc.MAXIM. 2.3GHz to 2.7GHz wireless broadband RF transceiver[EB/OL].[2014-04-11].http://wenku.baidu.com/link?url=YliTfcOzgxCjmwhb6_KpdDk845oNnmI9vXJzotCGo_cjShuyIYpnbcET1Z76kEy4mL71OnOh RokssIUlrbd1OfF-QPCXb4s5L3-VoJzNq3.

[8]王彦,曹鹏,费元春. 数字中频接收机的设计与实现[J]. 电讯技术,2004,44(5): 41-44.

[9]周顺,徐志军,杨田. 数字中频接收机中的数字AGC的设计与实现[J]. 军事通信技术,2008(1): 9.

[10]武爱文,冯卫国,卫淑芝,等.概率论与数理统计[M]. 上海:上海交通大学出版社,2011.

[11]ABRAMOWITZ M,STEGUN I A. Handbook of mathematical Functions[M]. Washington:National Bureau of Standards,1972.

[12]URKOWITZ H,PHILADELPHIA P. Energy detection of unknown deterministic signals[J]. Proceeding of the IEEE,1967,55(4): 523-531.

责任编辑:李 薇

Design of BPSK/QPSK Demodulator Based on Direct-conversion Zero-IF RF Integrated Chip

DENG Yuance1,2,CHEN Qiaoyan2,MA Lu1,2,SHI Liguo1,2,WANG Zhugang2

(1.UniversityofChineseAcademyofSciences,Beijing100190,China;2.NationalSpaceScienceCenter,ChineseAcademyofSciences,Beijing100190,China)

The design of BPSK/QPSK demodulator is investigated in this paper based on direct conversion zero intermediate frequency (zero-IF) RF integrated chip MAX2837. The characteristics of zero-IF RF integrated chip MAX2837 are introduced in subsection II. The design of automatic gain control loop, carrier recovery loop and timing recovery loop is analyzed in detail. The measurement result shows: the gap between the measured bit error probability and theoretical value is about 2.5 dB when the measured bit error probability is 10-5; the designed demodulator has many advantages, such as high integration level, small size and high quality with low price.

zero-IF; MAX2837; BPSK/QPSK demodulator

TN712.2

A

10.16280/j.videoe.2015.01.014

2014-05-11

【本文献信息】邓元策,陈巧艳,马路,等.基于商业零中频芯片的BPSK/QPSK解调器设计[J].电视技术,2015,39(1).