0.6 V CMOS低噪声放大器的设计与优化

周洪敏,张 瑛,丁可柯,于 映

(南京邮电大学 电子科学与工程学院,江苏 南京 210023)

0.6 V CMOS低噪声放大器的设计与优化

周洪敏,张 瑛,丁可柯,于 映

(南京邮电大学 电子科学与工程学院,江苏 南京 210023)

采用SMIC 0.18 μm CMOS工艺设计了一个低电压低功耗的低噪声放大器(Locked Nucleic Acid,LNA)。分析了在低电压条件下LNA的线性度提高及噪声优化技术。使用Cadence SpectreRF仿真表明,在2.4 GHz的工作频率下,功率增益为19.65 dB,输入回波损耗S11为-12.18 dB,噪声系数NF为1.2 dB,1 dB压缩点为-17.99 dBm,在0.6 V的供电电压下,电路的静态功耗为2.7 mW,表明所设计的LNA在低电压低功耗的条件下具有良好的综合性能。

低噪声放大器;噪声系数;输入匹配;低功耗

近年来,蓬勃发展的无线通信对无线射频通信系统提出了诸如高集成度、低电压、低功耗等更高的要求。低噪声放大器(Locked Nucleic Acid,LNA)被广泛应用于无线通信系统中,是无线通信系统中一个非常重要的部分,位于接收系统的前端,在放大微弱信号的同时抑制噪声干扰,提高系统的灵敏度。噪声、增益、功耗以及线性度是衡量LNA性能优劣的重要指标。LNA作为射频前端的关键模块,国内外学者对它作了深入的研究。针对深亚微米下的LNA的噪声性能,Derek K.Shaeffer和Thomas H.Lee做了详细研究,他们提出的功耗约束下的噪声优化方法被广泛采用;P.Aadreani等人提出的功耗约束下噪声和功率同时匹配方法,对LNA的噪声优化技术进行了完善;为了提高LNA的增益,H.Hsieh等人采用电流复用技术。

虽然随着CMOS工艺的迅速发展,使得高增益、低噪声和低功耗成为可能,但是线性度并没有随着工艺的提高而提高。在接收机中LNA的功耗占有相当大比例,降低其功耗对降低整个系统功耗有着重要意义。对于MOS管,其功耗和供电电压成平方关系,所以通常通过降低MOS管的工作电压降低功耗。同时,在电路设计过程中,为了克服高电场带来的高噪声要尽量避免使用太高的偏置电压。但是在通常情况下,低噪声放大器的噪声系数和MOS管的特征频率成正比[1-2],而特征频率和MOS管的偏置电压成正比关系,对于MOS器件来说,其线性度和增益也近似与其偏置电压成正比[3],所以当偏置电压降低时会造成LNA噪声系数增大、增益减小以及线性度变差。LNA位于无线射频接收机的前端,其性能好坏对整个接收机起着决定性作用。LNA必须具有低的噪声系数、足够的增益、低的功耗以及良好的线性度。但是实际上,噪声系数、增益、功耗和线性度是相互制约的。因此如何在低电压下设计高性能的LNA是当前研究的热点。

1 低噪声放大器的设计

共源共栅(cascode)结构被广泛应用于窄带LNA的设计中,电路如图1所示。由于cascode结构的共栅级可以有效地阻止共源级米勒效应的影响,故cascode结构有非常好的隔离度,这样在进行输入和输出端的匹配设计中,二者不会相互影响,可以进行单独的匹配设计,这样就大大提高了电路的设计效率。但是,对于此结构的LNA,从图1可以看出,MOS管M1和M2是堆积结构,该结构限制了电路工作在低电压下。

图1 cascode电路结构

对于传统的共源共栅结构,为了保证电路正常工作,需要将MOS管M1和M2偏置在饱和区,即应该满足

Vdsi≥Vodi=Vgsi-Vthi

(1)

式中:Vdsi,Vgsi,Vodi,Vthi分别为第i个NMOS管的漏源电压、栅源电压、过驱动电压以及阈值电压,i为1或2。

要保证电路正常工作,所需电源电压的最小值为

VCC_min≥(Vgs1-Vth)+(Vgs2-Vth)+Vth

(2)

在SMIC RFCMOS 0.18 μm工艺中,NMOS管的阈值电压为0.48 V,假设其过驱动电压为0.12 V,根据上式可以得到所需要的最小电源电压为0.72 V。本文采用折叠cascode结构,既可以工作在低电压下,又具备cascode结构的一些优点,电路如图2所示。NMOS管M1组成折叠cascode结构的共源级,共栅级由PMOS管M2构成,该结构既保持了cascode结构原有的许多特性,又能大大地降低对工作电压的要求。

1.1 线性度分析

当输入为小信号时,放大器的传输特性可以用泰勒级数[4]展开为

y(t)=a1x(t)+a2x2(t)+a3x3(t)

(3)

三阶交调点处的输入信号幅度为

(4)

对于共源放大器其漏极电流可以用泰勒级数展开为

图2 本文提出的折叠cascode电路结构

(5)

(6)

从式(6)可以看出,AIP3的值不仅与gm1,gm3有关还和gd3以及gd1有关系。为了获得高的线性度在设计LNA的过程中,首先希望gm1越大越好,在设计过程中可以通过增大MOS管的栅宽或者电流增大gm1的值。但是,对于一个cascode结构,其线性度[5]可以表示为

(7)

1.2 输入匹配及噪声分析

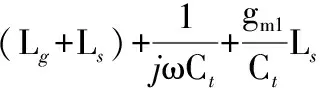

由图2可知,该电路的输入阻抗[6]为

(8)

式中:Ct=Cgs1+Cex。

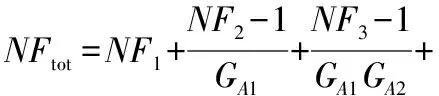

对于任何一个多级级联系统其噪声系数[7]可以表示为

(9)

式中:NFk为第k级的噪声系数;GA(k-1)为第(k-1)级的增益。由式(9)可知,第1级放大器的噪声和增益是关键,如果第1级的增益足够大,第2级及后面的各级放大器的噪声对系统的噪声影响可以忽略,因此电路噪声性能主要决定于第1级放大器[8]。所以主要分析第1级放大器即共源级的噪声。

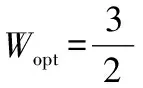

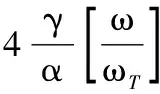

由经典的二端口噪声理论[9]可以推导在考虑功耗的限制下,噪声系数最小时的最优的MOS管宽度为

(10)

对于器件宽度为Wopt的器件,在功耗约束范围内得到的噪声系数为

(11)

2 电路仿真结果及分析

采用SMIC0.18μmCMOS射频工艺,在Cadence软件环境下完成电路各项性能指标的仿真。在0.6V工作电压下,电路的静态功耗为2.7mW,中心工作频率为2.4GHz。

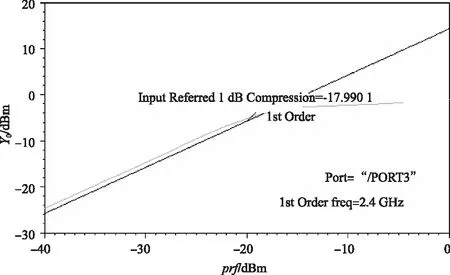

S参数随频率的变化过程如图3所示。在2.4GHz工作频率处,正向功率增益S21=19.25dB,输入反射系数S11=-12.46dB,说明此电路具有足够的增益并实现了比较好的输入阻抗匹配。噪声系数随频率的变化过程如图4所示,在工作频率2.4GHz处,噪声系数NF=1.923dB,具有较小的噪声系数。1dB压缩点如图5所示,说明此电路具有较好的线性度。

表1为本文设计的低噪声放大器与参考文献给出的低噪声放大器的性能比较结果,可以看出,采用折叠cascode结构,低噪声放大器不仅满足低电压、低功耗的要求,而且在相同的工艺条件,相同的工作频率下,本文设计的低噪声放大器在阻抗匹配、噪声和增益等方面都获得了较好的性能指标。

图3 LNA的S参数特性

图4 LNA的噪声系数特性

图5 LNA的1 dB压缩点线性结构

表1 LNA性能比较

3 小结

本文采用SMIC0.18μmCMOS工艺设计实现了一个折叠cascode低噪声放大器。主要研究了在低电压低功耗条件下的线性度提高和噪声优化技术。仿真结果表明,本文所设计的低噪声放大器在0.6 V的电压条件下取得了较高的增益、较好的输入匹配、较低的噪声系数以及较好的线性度,具有较好的综合性能指标。

[1]KUNHIN T, YOUNGBOG P, RAINER T, et al. High frequencynoise characteristics of RF MOSFETs in subthreshold region[C]//Proc. Radio Frequency Integrated Circuits (RFIC) Symposium. [S.l.]: IEEE,2003:163-166.

[2]NGUYEN T, KIM C, IHM G, et al. CMOS low-noise amplifier design optimization techniques[J]. IEEE Trans. Microwave Theory and Techniques, 2004, 52(5):1433-1442.

[3]LIU B, ZHOU J, MAO J. Design of0.5 V CMOS cascode low noise amplifier for multi-gigahertz applications[J]. Journal of Semiconductors,2012,33(1):1506.

[4]李志群,王志功. 射频集成电路与系统[M]. 北京:科学出版社,2008.

[5]RAZAVI B. RF Microelectronics[M]. NJ, USA: Prentice Hall PTR, 1998.

[6]FAN X H, ZHANG H, EDGAR S. A noise reduction and linearity improvement technique for a differential cascode LNA [J]. IEEE Journal of Solid-state Circuits ,2008, 43(3):588-599.

[7]GRAY P R,MEYER R G.Analysis and design of analog integrated circuit[M].4th ed.New York:John Wiley & Sons,2001.

[8]王振朝,种少飞,韦子辉,等. 射频低噪声放大器设计与仿真[J].电视技术,2014,38(5):81-84.

[9]THOMAS H L. CMOS射频集成电路设计[M]. 余志平,译. 北京:电子工业出版社,2006.[10]景一欧,李勇,赖宗声,等. 基于0.18 μm CMOS工艺的2.4 GHz/5.2 GHz双频段LNA的设计[J]. 电子器件,2007,30(4):144-147.

[11]丁冲,戴宗杰,张小兴,等. 基于ZigBee接收机的2.4 GHz CMOS LNA的设计[J].南开大学学报:自然科学版,2008,41(3):105-110.

[12]王宁章,周长川. 2.4 GHz射频低噪声放大器分析与设计[J].微计算机信息,2007,23(10):242-243.

Design and Optimization of 0.6 V CMOS LNA

ZHOU Hongmin, ZHANG Ying, DING Keke, YU Ying

(CollegeofElectronicsScienceandEngineering,NanjingUniversityofPostsandTelecommunications,Nanjing210023,China)

A low-voltage low-power low-noise amplifier(LNA) using SMIC 0.18 μm CMOS technology is presented in this paper. The linearity improvement and noise figure optimization techniques of a low-noise amplifier under low-voltage condition are discussed. Cadence SpectreRF simulation results show the LNA achieves a forward gain of 19.65 dB, input reflection(S11) of -12.18 dB, noise figure of 1.2 dB and 1 dB compression point of -17.99 dBm at 2.4 GHz while consuming 2.7 mW from 0.6 V power supply. The results indicate that this LNA has perfect performance under low-voltage low-power condition.

low noise amplifier; noise figure; input matching; low power

国家自然科学基金青年科学基金项目(61106021);江苏省高校研究生科研创新计划项目(KYLX_0802);南京邮电大学青蓝工程基金项目(NY210037)

TN722.3

A

10.16280/j.videoe.2015.01.013

2014-07-07

【本文献信息】周洪敏,张瑛,丁可柯,等.0.6 V CMOS低噪声放大器的设计与优化[J].电视技术,2015,39(1).

周洪敏(1978— ),女,讲师,主要研究方向为射频集成电路设计。

责任编辑:李 薇