无损数字视频存储回放设备设计

唐湘成,黄自力,刘 怡,曾 晶,肖 柯

(西南技术物理研究所,四川 成都 610041)

无损数字视频存储回放设备设计

唐湘成,黄自力,刘 怡,曾 晶,肖 柯

(西南技术物理研究所,四川 成都 610041)

采用Altera公司的EP2C8 FPGA作为主控芯片,设计的无损数字视频存储回放设备实现了ATA-6规范的IDE硬盘接口协议和千兆网络图像传输,为图像处理算法研究提供了一个效率高、成本低、验证准确的仿真调试方法。该设备已在算法研发团队中普及使用,具有较大的市场推广价值。

IDE;千兆网;无损数字视频存储回放

随着近年来视频监控领域的智能化需求不断提升,针对该领域的图像处理算法研究也在持续升温,无损(或称作无压缩)的数字视频存储回放设备成为了算法研究必不可少的调试验证工具。目前智能视频监控领域尤其是在高清摄像机普及应用的情况下,虽然配备有DVR(即数字视频录像机)设备能对监控过程中的数据进行存储回放,但均采用了诸如MPEG-2、MPEG-4、H.264、M-JPEG等图像压缩技术,压缩过后的视频图像不能真实反应出原始“问题”视频,并不适合图像处理算法仿真研究。

算法研究目前大多采用基于PCI/PCIE的无压缩图像采集卡的方案进行仿真调试,但存在以下问题:1)由于基于PC平台,使用时需配置计算机,不便于携带;2)此类图像采集卡只具备PC机端采集及回放功能,无法输出数字视频时序,只能对单帧图像数据逐帧进行仿真调试,工作繁琐,测试周期长;3)造价较高,不便于普及使用。

基于上述,本文设计的无损数字视频存储回放设备,采用Altera公司的EP2C8 FPGA作为主控芯片,实现了ATA-6规范的IDE硬盘接口协议和千兆网络图像传输,为图像处理算法研究提供了一个效率高、成本低、验证准确的仿真调试方法。

1 总体方案设计

无损数字视频存储回放设备是先将摄像机输入的数字视频无压缩的实时采集,并通过IDE接口协议存储于外挂硬盘中。算法仿真调试时,按照原接收摄像机时的输入时序将存入硬盘中的数据读出,因此设备可完全模拟摄像机存储数据时的状态,将设备的数字视频输出接口直接替换原摄像机的输出接口,接入待测试设备即可进行算法的仿真调试。为了便于在存储/回放过程中操控及观测实时图像,设计中增设了千兆网传输图像数据至PC端功能,实现对存储/回放图像的同步显示以及指令控制。

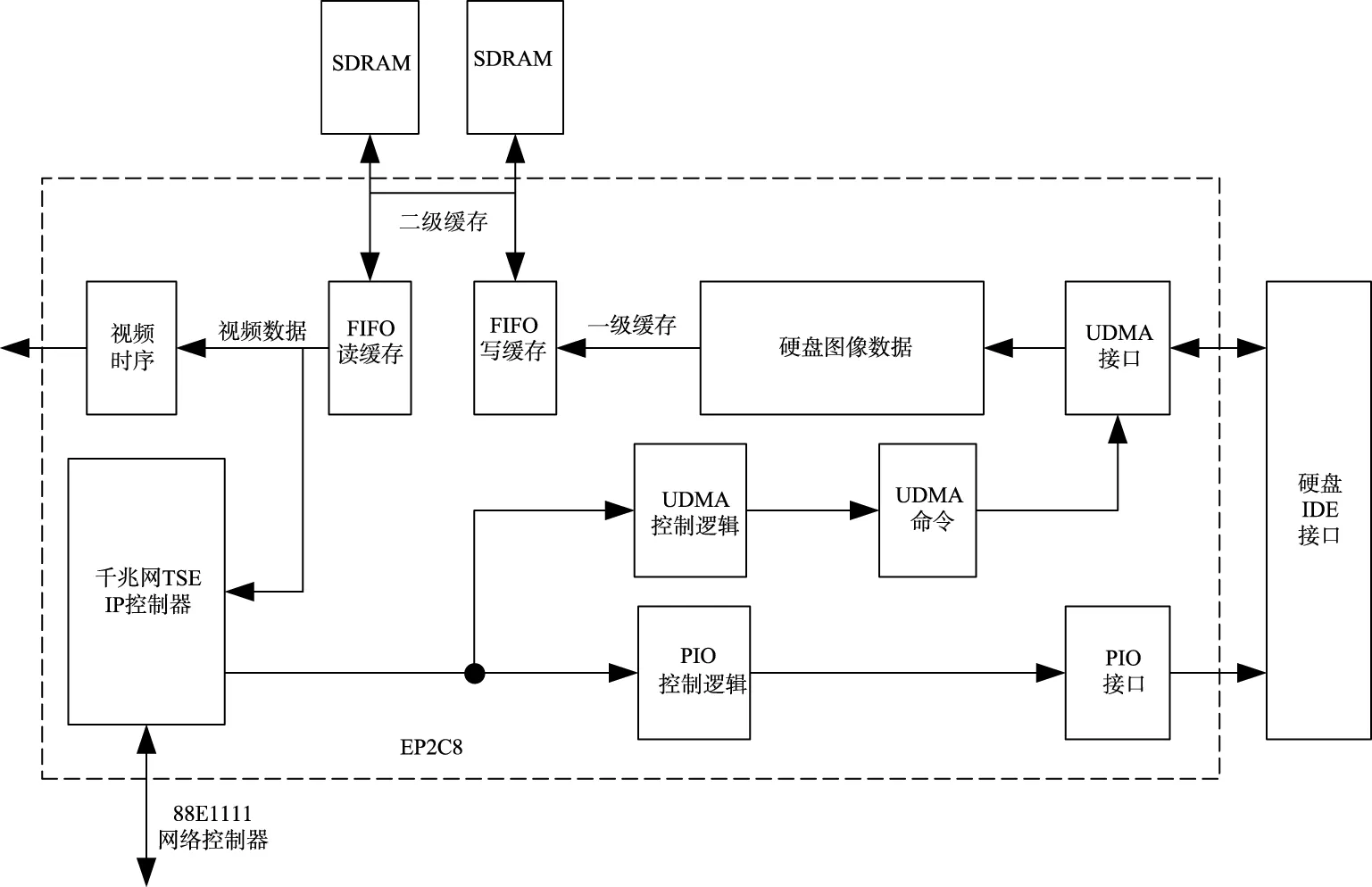

系统整体结构组成如图1所示,以Altera的Cyclone II EP2C8 FPGA芯片为主控制器,控制88E1111芯片实现千兆网与PC机的数据通信,通过FPGA外接的IDE接口与硬盘互联,并行LVTTL接口则包含了数字视频的输入及输出接口。

设计中使用的摄像机成像芯片为MT9M001,其输出的数字图像分辨率为1 280×1 024,图像位宽10 bit,帧率30 f/s(帧/秒),要满足实时存储/读取要求,IDE硬盘的读写速度应≥20 Mbit/s。IDE(Integrated Drive Electronics)即“电子集成驱动器”,又称为ATA(AT-Attachment)接口。ATA经历了从ATA-1到ATA-6的发展过程,ATA-6兼容之前所有的ATA协议标准[1],同时将DMA传输的最高传输速度提升至100 Mbit/s。设计中采用FPGA实现ATA-6规范的IDE硬盘接口协议能够满足无损数字视频硬盘存储及回放的速率要求,FPGA控制实现的千兆网图像传输,也能保证图像的实时显示需求。

图1 系统整体结构组成

2 各功能模块设计与实现

设备主要有无损数字视频存储以及无损数字视频回放两大功能。无损数字视频的存储功能具体可划分为如图2所示的5个功能模块。接收视频缓存模块将接收到的摄像机图像数据一路送硬盘写入模块,在指令网络接收模块控制下,将图像数据存入硬盘;另一路则送入视频网络发送模块,并在指令网络接收模块控制下送PC显控模块进行显示。

图2 视频存储功能模块划分

无损数字视频回放为无损数字视频存储的逆过程,具体可划分为如图3所示的6个功能模块。硬盘读出模块在指令网络接收模块控制下将需回放的视频数据从硬盘中读出送入发送视频缓存模块,经该模块处理后的图像数据一路送入视频网络发送模块,并在指令网络接收模块控制下送PC显控模块进行显示;另一路送入视频发送模块后,经数字视频输出接口按照原摄像机输入时序实时输出数字图像数据。

图3 视频回放功能模块划分

2.1 硬盘写入/读出模块

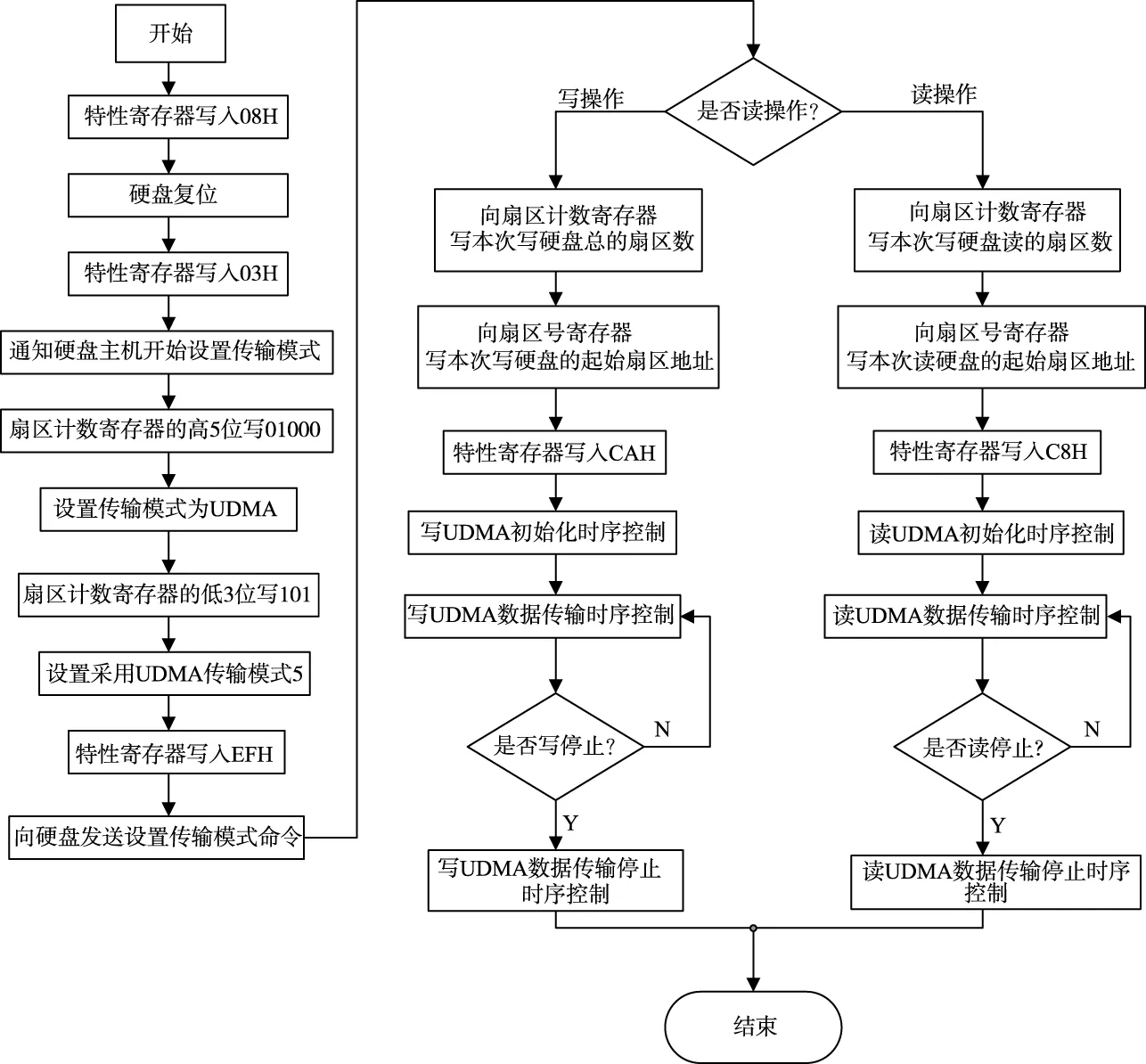

对于主机与硬盘之间的数据传输,IDE接口有两种传输方式:一种是程序控制IO (PIO),另一种是DMA方式。DMA方式又分为单字DMA、多字DMA、Ultra DMA(简称UDMA)模式0到模式5。UDMA采用了与DMA不同的技术,时钟的双沿用做数据读写的选通信号,即每半个时钟周期就可以传输一次数据,使得硬盘的数据传输率成倍增加[2]。本设计中采用PIO传输模式先对UDMA命令参数设置,如复位、DMA写、DMA读、特性参数设置等,然后启动UDMA传输,具体操作流程如图4所示。

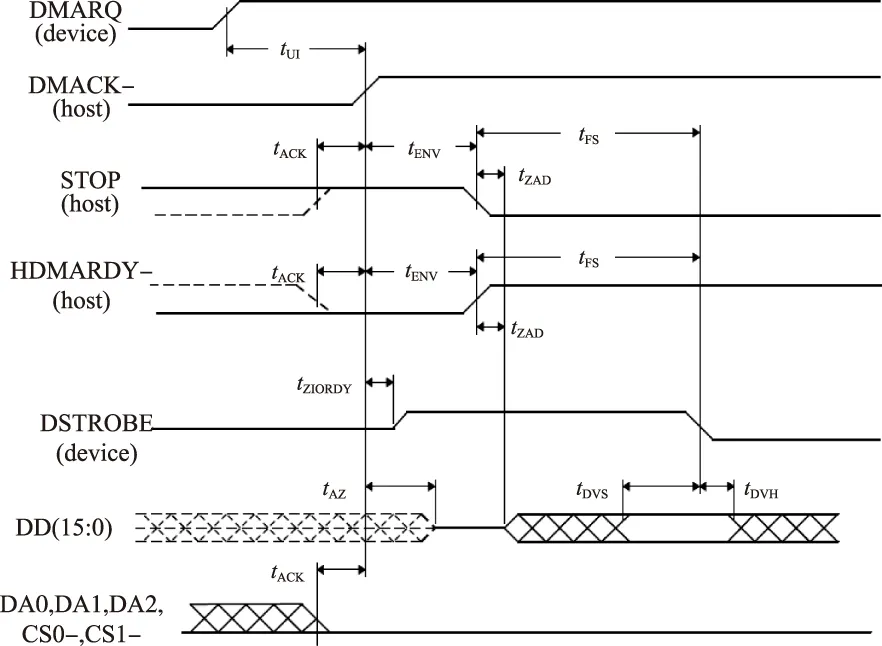

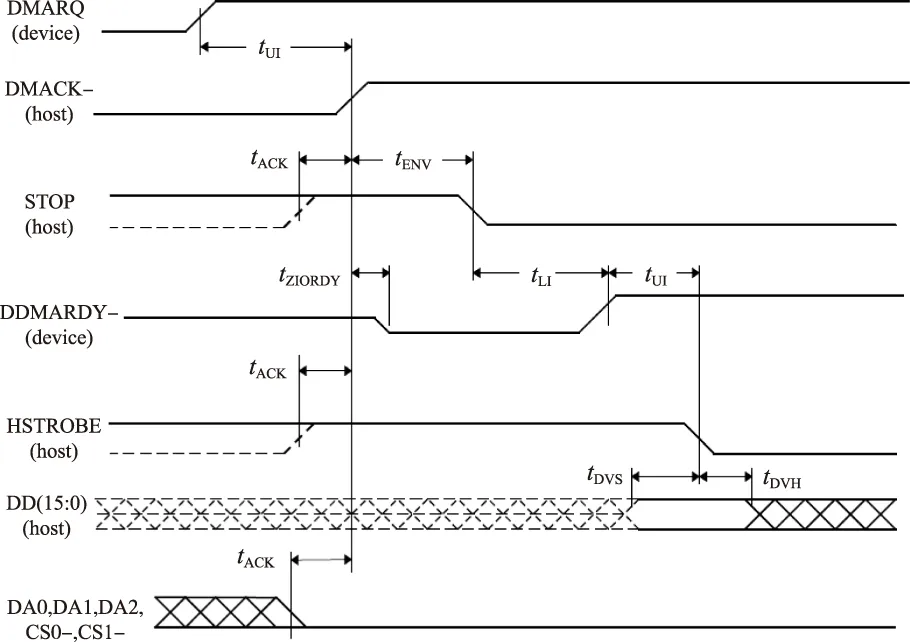

图5~图7列出了硬盘操作几个关键的时序图,图5为PIO模式读写时序[3],图6为UDMA写入时序[3],图7为UDMA读出时序[3]。设计时各信号间不仅需保证正确相位关系,还需满足UDMA模式5规定的建立和保持时间。

2.2 视频缓存模块

硬盘的读取速度为100 Mbit/s,FPGA控制的千兆网络三速以太网(Tri Speed Ethernet,TSE)控制器运行时钟频率125 MHz,模拟前端摄像机MT9M001输出图像的时钟频率48 MHz,因此在图像数据传输过程中需经两级缓存处理:一级缓存为FIFO写入/读出操作,其保证硬盘读取速率与SDRAM写入速率以及SDRAM写入同图像输出速率的匹配;二级缓存则保证SDRAM乒乓存入整帧图像数据的正确读写操作。FPGA控制IDE硬盘回放实时视频数据流程如图8所示。

1)PIO控制逻辑模块根据网络控制命令产生PIO控制命令,对IDE硬盘的工作状态、起始地址等进行设置,并控制IDE硬盘进入UDMA工作模式。

2)UDMA控制逻辑模块根据网络控制命令产生UDMA控制命令,通过UDMA接口控制硬盘进入UDMA读出状态。

图4 操作硬盘控制命令流程

图5 PIO模式时序波形图

图6 UDMA写入时序波形图

图7 UDMA读出时序波形图

3)图像数据从硬盘读出写入FIFO写缓存[4],为图像数据切换存入异步时钟域的SDRAM作准备。

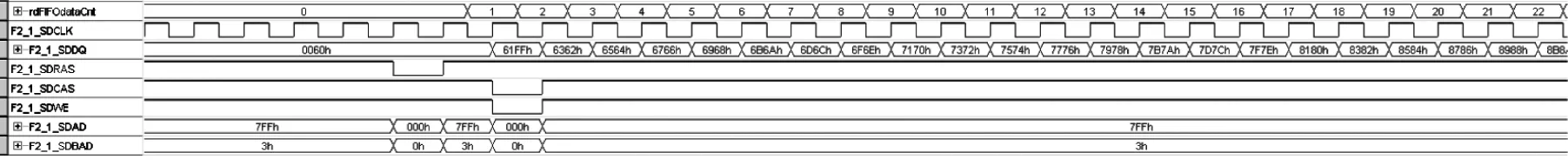

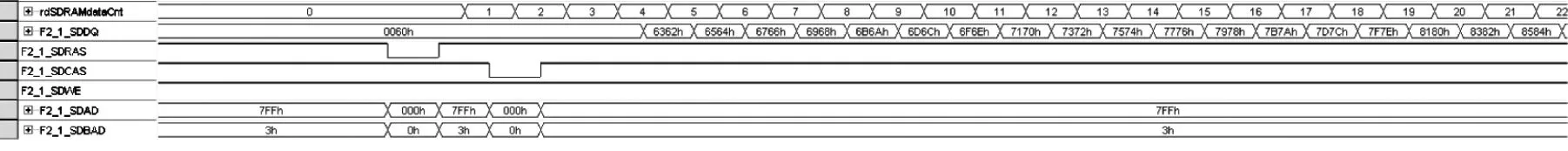

4)将FIFO写缓存中的图像数据存入SDRAM,图9为采用Quartus II 的Signal Tap软件对写入SDRAM操作的采样波形图。

5)读出SDRAM中的图像数据写入FIFO读缓存[4],此刻应保证写入FIFO读缓存中的数据在产生模拟原摄像机时序的每行正程到来前数据准备就绪,图10为采用Quartus II 的Signal Tap软件对读出SDRAM操作的采样波形图。

6)最后将FIFO读缓存的数据一路由视频时序模块生成模拟原摄像机时序将数据读出;另一路读出后送入FPGA控制的千兆网TSE控制器封包后发送至PC端显示。

图8 FPGA控制IDE硬盘回放流程

图9 SDRAM写入操作(截图)

图10 SDRAM读出操作(截图)

FPGA控制IDE硬盘存储实时视频数据流程与回放流程互为逆过程,因此接收视频缓存模块同发送视频缓存模块也互为逆过程,功能相仿。

2.3 视频发送模块

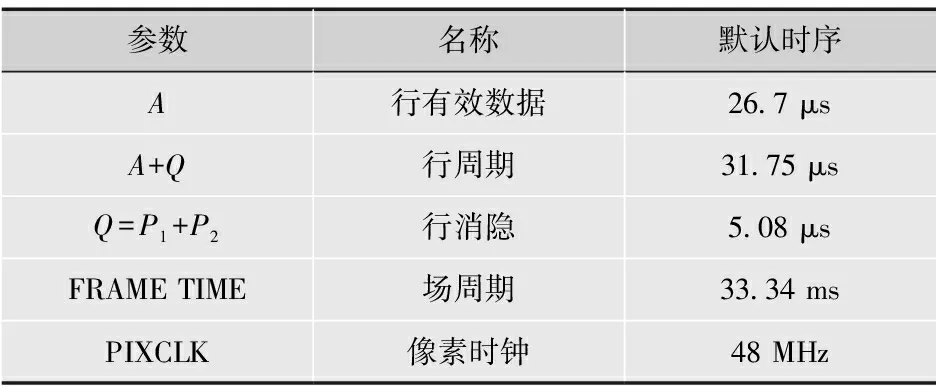

模块发送的视频应满足MT9M001芯片的输出时序要求[5],如图11及表1所示。

图11 MT9M001输出时序图

表1 MT9M001时序主要参数

参数名称默认时序A行有效数据26 7μsA+Q行周期31 75μsQ=P1+P2行消隐5 08μsFRAMETIME场周期33 34msPIXCLK像素时钟48MHz

2.4 网络传输模块

网络传输模块由视频网络发送模块以及指令网络接收模块组成。二者均采用UDP的通信协议,视频网络发送模块主要负责板端图像数据向PC端的网络发送;指令网络接收模块主要完成板端接收PC端通过网络发送的控制指令,如硬盘参数设置、硬盘存储的开始停止命令、回放的开始停止命令等。

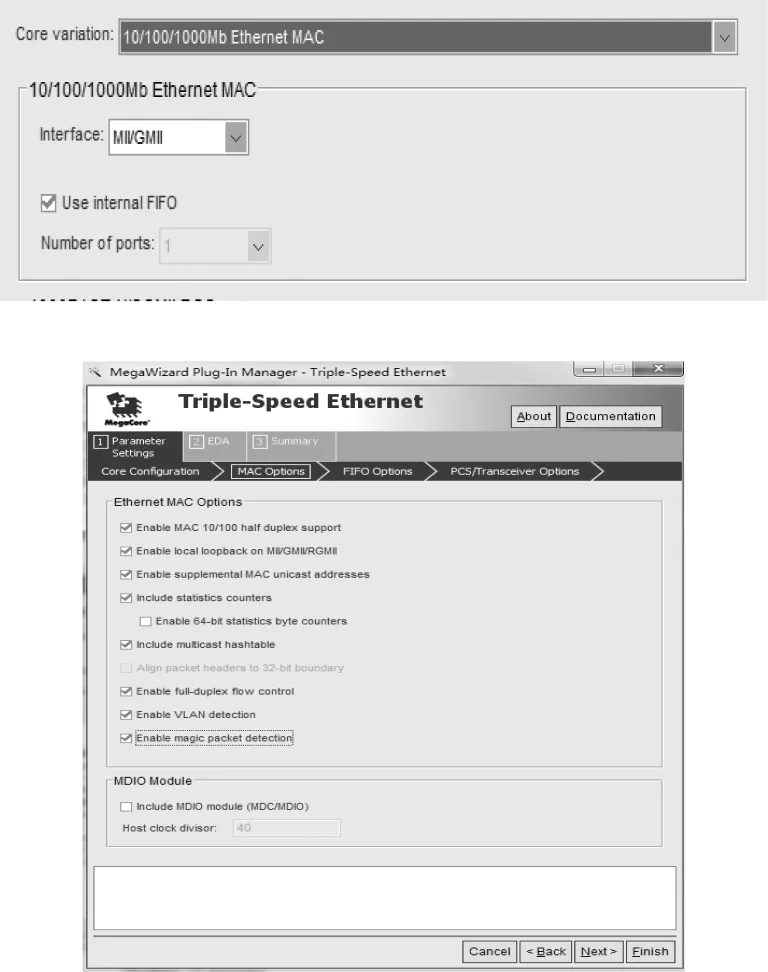

Altera提供了可参数化的千兆以太网Megacore解决方案[6],该方案可在Altera 的Arria GX、CycloneII、CycloneIII系列FPGA上工作,采用千兆网TSE控制器 IP核可实现单条或多条吉比特以太网链路,通过交换机或路由器可与任意以太网端口相连,整个配置界面如图12所示可将 IP 核配置为所需模式[7]。

FPGA控制千兆以太网发送图像数据时UDP包的封包协议设定为UDP包头+图像数据包的形式。

1)UDP包头:由4 byte MAC报头+20 byte IPv4报头+8 byte UDP报头组成;

2)图像数据包:由1 byte帧序号+3 byte包序号+512 byte从FIFO中读出Len(512 byte)长度的图像数据+

图12 IP 核参数配置界面(截图)

3 byte包尾组成。

FPGA控制千兆以太网发送图像数据的大致流程如下:

1)每个UDP包的长度设定为Len(512 byte);

2)将图像数据按行在FIFO中缓存,当存满一个设定的Len长度数据后产生一个UDP包生成信号;

3)FPGA接收信号后生成上述封包形式的UDP包发送给TSE控制器,完成一次UDP包的图像数据网络传输;

4)以此往复,完成一帧图像数据的发送。

图13为利用winpcap软件对送达PC端网口数据抓取UDP包的结果,经测试满足上述协议要求。

图13 winpcap抓包结果图(截图)

2.5 PC显控模块

PC端使用VS2008开发软件,内嵌winpcap网络抓包函数将收到的图像数据包依次保存至图像缓存区,当一幅图像存储完成后,采用位图显示方式进行图像的显示。除此之外,PC端显控模块还完成了诸如硬盘参数设置、存储的启动/停止、回放的启动/停止等操作,其界面如图14所示。

图14 PC端显控界面(截图)

3 分析及总结

本设计采用Altera公司的EP2C8 FPGA作为主控芯片,实现了ATA-6规范的IDE硬盘接口协议及千兆网络图像传输。经测试,可满足摄像头分辨率为1 280×1 024,帧频30 f/s(帧/秒)的无损数字图像采集存储,实时回放过程可完全模拟原摄像头采集时状态,将此设备作为图像处理算法研究的调试工具具有仿真验证准确、效率高的特点。由于设计采用FPGA为核心架构,今后可根据用户需求更改以适应各种标准的摄像头应用,并且硬盘的操作不依赖于操作系统,可实现脱机工作,便于携带。此外整个设备的硬件成本低廉,不足500元,采用如图15所示的IDE转SATA2.0转接卡后,还可挂接大容量的SATA2.0硬盘,以满足长时间存储数据需求,方案具有较高的性价比。现该设备已在算法研发团队中普及使用,具有较大的市场推广价值。

图15 硬件连接图(照片)

[1]王毅,管会生,刘斌彬,等.基于FPGA的IDE硬盘接口卡的实现[J].微计算机信息,2006,22(11):201-203.

[2]程海波.基于FPGA的机载高速数据记录系统的研究[D].西安:中国科学院西安光学机械研究所,2005.

[3]Technical Committee.Information technology-AT Attachment with Packet Interface-6(ATA/ATAPI-6)[S].2001.

[4]刘妍妍.遥感图像采集中的SDRAM图像缓存技术[J].电视技术,2012,36(17):52-55.

[5]Micron Technology Inc.MT9M001-1/2-Inch Megapixel Digital Image Sensor Features[EB/OL].[2014-08-18].http://www.

micron.com.

[6]王雪萍,唐林波,赵保军.基于DSP+FPGA的远程屏幕传输系统[J].电视技术,2013,37(9):75-79.

[7]Altera Corportion.Triple speed Ethernet megacore function user guide[EB/OL].[2014-08-18].http://www.altera.com.cn.

唐湘成(1980— ),博士生,主研电路系统设计、数字图像处理;

黄自力(1965— ),研究员,博士生导师,主研数字图像处理;

刘 怡(1981— ),高级工程师,主研嵌入式数字图像处理;

曾 晶(1984— ),硕士生,主研数字图像处理;

肖 柯(1978— ),高级工程师,主研嵌入式数字图像处理。

责任编辑:闫雯雯

Design of Non-compressed Digital Video Storage Playback Equipment

TANG Xiangcheng,HUANG Zili,LIU Yi,ZENG Jing,XIAO Ke

(SouthwestInstituteofTechnicalPhysics,Chengdu610041,China)

The non-compressed digital video storage playback equipment is designed with EP2C8 FPGA of the Altera Corporation as the main control chip, the IDE hard disk interface protocols standardized by ATA-6 and image transmission of gigabit network are implemented.Thus an accurate stimulated debugging method with higher-efficiency and lower-cost for image processing is eventually achieved.

IDE;gigabit network;non-compressed digital video storage playback

TN946.7

A

10.16280/j.videoe.2015.07.029

2014-09-18

【本文献信息】唐湘成,黄自力,刘怡,等.无损数字视频存储回放设备设计[J].电视技术,2015,39(7).