超宽带穿墙雷达数据采集系统的设计与实现①

胡 恺,欧阳缮,徐五生

(桂林电子科技大学 信息与通信学院,广西 桂林 541004)

随着时代的发展,穿墙雷达的应用不再仅仅局限于军事上,在安全防范、医学成像等方面都有了显著的应用[1]。穿墙雷达系统主要分为2类:一类是使用频域信号的雷达系统,像连续波雷达系统;另一类是使用时域信号的雷达系统,如脉冲超宽带雷达系统[2-4]。其中超宽带穿墙雷达系统又因为其结构简单、更高的成像分辨率以及通过按时间选通的方式,能够方便地分辨信号耦合波与多径传播反射波的优势,更受人们青睐[5]。

现阶段的穿墙雷达接收机主要基于顺序等效采样算法实现,其结构框架一般分为2种:1)先用FPGA板实现顺序等效采样,然后后端通过DSP进行数据处理后送至ARM显示[6];2)用FPGA板实现顺序等效采样后将数据保存,拷贝到PC上用Matlab处理、画图[7]。现阶段的接收机都存在明显的不足,首先是顺序等效采样方法的不足[8]。顺序等效采样方法的基本实现过程是在每一个回波周期采集一个数据,当下一个回波周期到来时,通过延时器延时一段纳秒级的时间后采集第二个数据,以此类推,直至所有延时时间总和大于或等于信号的回波周期为止,最后将这段时间内采集的数据按顺序排列即可恢复回波信号。这种采样方法通过小而精确的步进时间获得较高的等效采样率,但也暴露了它的缺点,它还原一个周期所需要的n个数据要经过n个回波周期的采集才能得到,这无疑造成了回波信号利用率过低、数据采样时间过长。其次是接收机整体系统性的不足,主要表现在接收机实现难度较大及操作繁琐。具体来说,第一种结构的接收机用DSP作为数据处理端,ARM作为显控设备,这样不仅因为要在DSP上实现算法而加大了接收机实现难度,而且作为显控设备的ARM也很难做到人性化的显示与操作;第二种结构的接收机将数据传输给PC后,需要操作人员将数据导入Matlab中,再调用成像算法处理数据,这就造成了数据处理过程操作繁琐,缺少一个系统化的控制[9-10]。

鉴于现有接收机存在着许多不足,提出一种更加合理的用于超宽带穿墙雷达的数据采集系统。它在数据采集采用伪随机等效采样算法,通过等步长的采样过程确保对回波信号的充分利用与还原,克服了顺序等效采样算法存在的缺点。而且接收机后端数据传输部分采用网口传输的方式,保证了数据传输速率的高效与完整。上位机用VC编写界面,在后台调用Matlab提供复杂数据处理能力,解决了一般接收机不够人性化、算法实现难度大的问题。系统整体性能优越,且方便移植。

1 数据采集系统的整体框架

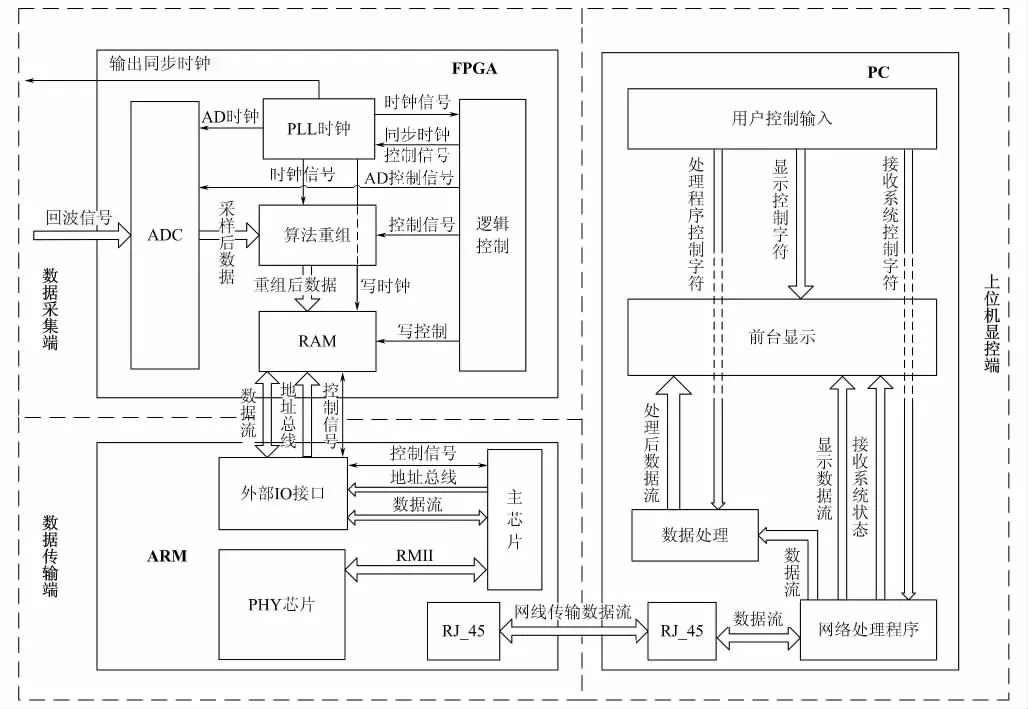

数据采集系统主要完成以下功能:数据采集与重组、信息的交互、上位机用户控制与信息显示。为此,把数据采集系统划分为3个部分来设计与实现:以FPGA为核心的数据采集端,以ARM为核心的数据传输端,以及上位机显控端。数据采集系统整体框架如图1所示。

图1 数据采集系统整体框架Fig.1 The overall framework of data acquisition system

2 数据采集系统的设计与实现

2.1 数据采集端的设计与实现

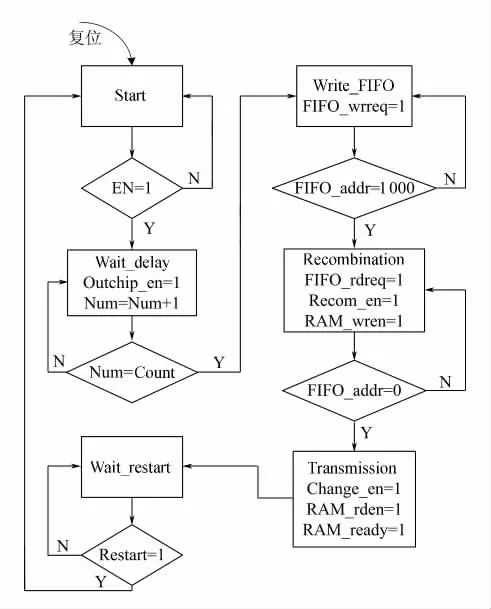

数据采集端的主要功能是利用较低的采样率对超宽带回波信号进行采样,然后通过伪随机等效采样算法[9-10]对采样数据重新排放,实现对回波信号的还原。这部分的功能在FPGA上编程实现,具体工作流程如下,其算法状态机描述的状态转移如图2所示。

图2 数据采集端状态转移图Fig.2 State transition diagram of data collection part

1)Start:开发板上电或者异步复位后进入,检测到EN高电平后进入下一个状态,表示检测到一个数据采集周期的开始。

2)Wait_delay(先使能外部芯片模块),包括AD芯片LTC2240同步时钟产生芯片NB6N14S,由于AD芯片从睡眠模式转换到工作模式需要一段唤醒时间[11],程序会进入原地等待状态,然后使能计数器,当延时到一定长的时间,检测到计数器与设定数值Number相等时,进入下一个状态,表示LTC2240与NB6N14S已经处于正常工作状态。

3)Write_FIFO(拉高FIFO写使能信号FIFO_wrreq),对FIFO进行写操作,完成AD采集输出数据的暂存,当检测到FIFO已写入足够的数据时,即检测到FIFO的使用地址输出为1000后,停止对FIFO的写入,进入下一个状态。

4)Recombination(重组过程),完成对FIFO暂存数据的重新排列。当进入这个状态后,拉高FIFO读使能信号FIFO_rdreq,对FIFO进行读操作,使FIFO输出的数据送到双口RAM数据线处;拉高Recom_en,使能重组模块,使其根据伪随机等效采样算法算出重新排列数据所需的顺序,送到双口RAM地址线处;拉高RAM_wren,使能双口RAM的写操作,把FIFO输出的数据在重组模块对应排列顺序,完成对双口RAM的写过程。当检测到FIFO中的数据已经读完后,即FIFO中的使用地址输出为0,就进入下一个状态。

5)Transmission(传输过程),将双口RAM的数据通过数据线传输到后端的数据传输端。当双口RAM的数据写入完毕后,拉高数据就绪信号RAM_ready,使后端的ARM板知道数据已准备好,这时ARM会触发中断,给双口RAM送来读时钟与读地址,数据经过双口RAM的读写传输到ARM。

6)Wait_restart(等待过程),当后端的ARM读取双口RAM中的数据时,其内部的计数器会使能,计数器满以后,即对双口RAM中的所有数据读取完毕,ARM返回一个Restart信号,通知FPGA可进行下一轮的数据采集。

2.2 数据传输端的设计与实现

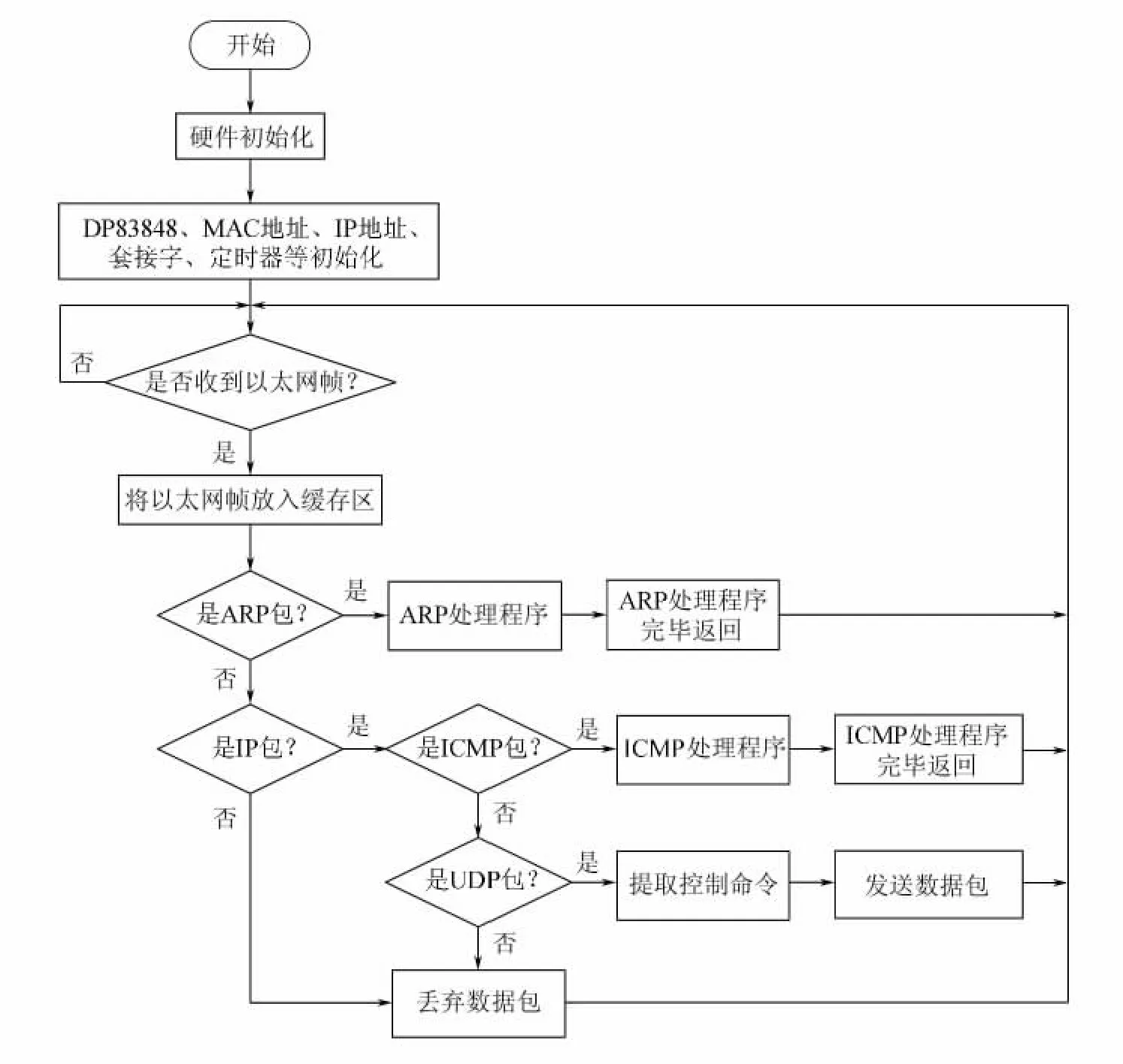

数据传输端负责从数据采集端接收准备好的数据发送给上位机显控端进行处理,也负责从上位机显控端接收控制字符完成对数据采集端与数据传输端的控制。该部分功能通过在LPC1766上编写UDP通信协议实现,LPC1766是基于ARM Cortex-M3核的微控制器,其操作频率可达100 MHz,含有64kB的数据存储器、以太网MAC等[12],因 此,在LPC1766上实现UDP通信只需编写实现ARP、IP、ICMP、UDP等通信协议即可。

具体到数据传输端与上位机显控端之间的网络通信模式,采用客户/服务器的模式,其中,数据采集端对应服务器端,上位机对应客户端。当服务器端启动后会在指定端口等待客户端的控制字符,然后,客户端通过网络向服务器端发送事先约定有效控制字符,接着,客户端进入等待服务器数据流的状态,最后,在服务器端接收到有效的控制字符后,按约定的格式向网络进行数据流的传输。数据传输端的UDP通信程序流程如图3所示。当传输端收到上位机传来的网络帧后,程序会先根据数据包的类型对网络帧进行判断,然后跳转到对应数据包的处理程序部分进行处理,这时如果收到的帧携带的是UDP数据包,则程序会对数据包内的数据进行分析,如果与控制字符相符,传输端就向网络发送携带采集数据的数据包,等待上位机的接收,直到本次采集数据发送完毕,传输端又进入等待状态,等待下一次的数据接收与发送。

图3 数据传输端软件流程图Fig.3 Flow chart of data transmission part

2.3 上位机显控端的设计与实现

上位机显控端是PC实现的人机交互界面,主要实现控制、显示、数据处理、数据存储与读取的功能。考虑到VC编程提供的丰富的接口与Matlab强大的数据处理能力,将这部分的功能利用Matlab与VC混合编程的形式实现。即前台运行VC界面程序,用户通过界面上的按钮实现对系统的控制,当数据采集完成传输到上位机后,用户可以按下“成像”按钮,在后台通过COM接口将数据导入Matlab进行处理,结果最终返回到前台界面显示。

3 实验结果

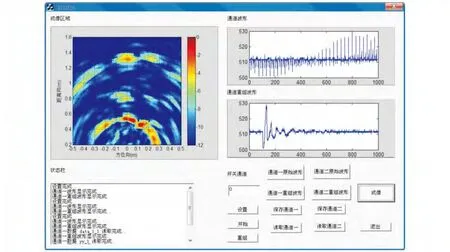

测试系统由信号源、收发天线和设计的数据采集系统组成。信号源为500~1300 MHz的一阶高斯脉冲,信号周期为10 MHz。收发天线采用适合发射信号频段的极化天线,信号源发射的脉冲穿过5cm的木板,到达木板后面的30cm×30cm的铁板后反射,数据采集系统在数据采集端通过2路采集通道,对接收天线接收到的回波信号进行采集重组,并将重组数据通过数据传输端传至PC,PC通过后台调用Matlab对数据进行处理,得到结果在前台VC界面显示。最终实现效果如图4所示。

4 结束语

现有的利用顺序等效采样方法实现的穿墙雷达接收机都存在算法和系统性方面的不足,根据伪随机等效采样算法设计的数据采集系统,通过将FPGA与ARM有效地结合,解决了现有的等效采样方法存在的问题,实现等效采样率10GHz的采样效果,在上位机实现友好的人机交互。系统结构紧凑,易于更新且成本较低,通过实验验证成像效果良好,且整体性能可靠。

图4 上位机实验结果Fig.4 Experimental results in PC

[1]BaranoskiE J.Through-wall imaging:historical perspective and future directions[J].Journal of the Franklin Institute,2008,345(6):556-569.

[2]Qiu Zhaokun,Li Dongze,Jiang Weidong.Study of continuous wave radar for human motion characteristics measurement[C]//10th IEEE International Conference on Signal Processing,2010:1078-1081.

[3]Yang Yunqiang,Fathy A E.Development and implementation of a real-time see-through-wall radar system based on FPGA[J].IEEE Transactions on Geoscience and Remote Sensing,2009,47(5):1270-1280.

[4]Wang Yazhou,Fathy A E.Advanced system level simulation platform for three-dimensional UWB through-wall imaging SAR using time-domain approach[J].IEEE Transactions on Geoscience and Remote Sensing,2012,50(5):1986-2000.

[5]Lazaro A,Girbau D,Villarino R.Analysis of vital signs monitoring using an IR-UWB radar[J].Progress in E-lectromagnetics Research,2010,100:265-284.

[6]Xu Yantao,Kong Lingjiang,Yang Jianyu,et al.Research and application of display and control system based on embedded Linux[C]//Computer and Electrical Engineering,ICCEE 2008.International Conference on.IEEE,2008:802-806.

[7]叶盛波,周斌,方广有.新型超宽带探地雷达数字采样接收机设计[J].电波科学学报,2011,26(4):783-788.

[8]Guo Shize,Sun Shenghe,Zhang Zhongting.A novel equivalent sampling method using in the digital storage oscilloscopes[C]//Instrumentation and Measurement Technology Conference,IEEE,1994:530-532.

[9]黄守麟.超宽带穿墙探测雷达信号采集和处理系统设计与实现[D].桂林:桂林电子科技大学,2009:10-19.

[10]谢跃雷,晋良念,欧阳缮,等.一种基于FPGA的超宽带雷达数字接收机[J].现代雷达,2014(1):62-65.