基于以太网的加速度传感器数据采集传输系统设计*

邹 坤,石云波,焦佳伟,赵 赟,贺 婷

(1.中北大学,山西 太原030051;2.苏州中盛纳米科技有限公司,江苏 苏州215123;3.电子测试技术国防重点实验室,山西 太原030051)

0 引 言

对于大量的数据进行采集、传输、处理和存储,采用串口方式已经不能满足系统的需求,通过串口传输步进速度比较慢,而且传输模式单一,误码率比较高,不能适应越开越快的工业和军事的发展。而以太网不仅兼容性好,通信速度快,传输距离远而且利于上位机交互,在上位机软件中也有成熟的以太网接口函数[1]。

本文提出了一种基于以太网的加速度传感器数据采集传输系统设计方案,采用FPGA 为主控芯片,完成了数据的接收转换成数据帧进行传输[2]。采用AD7667 做为高速A/D 转换芯片。AD7667 作为一个16 位的高速A/D 转换芯片,由一个单一的5 V 供电,内部包含一个高速16 位采样A/D 转换器,并且具有低功耗应用的电源减少模式(impulse 模式)。

W5300 是一种0.18 μm CMOS 工艺的单芯片器件,内部集成10/100 M 以太网控制器,MAC 和TCP/IP 协议栈。W5300 使用方便、稳定可靠,广泛应用于高性能、低成本的Internet 嵌入式领域。通过一个集成有TCP/IP 协议和10/100M 的以太网MAC 和PHY 的单芯片可以非常简单和快捷地实现Internet 连接。

1 系统硬件设计

1.1 硬件总体结构

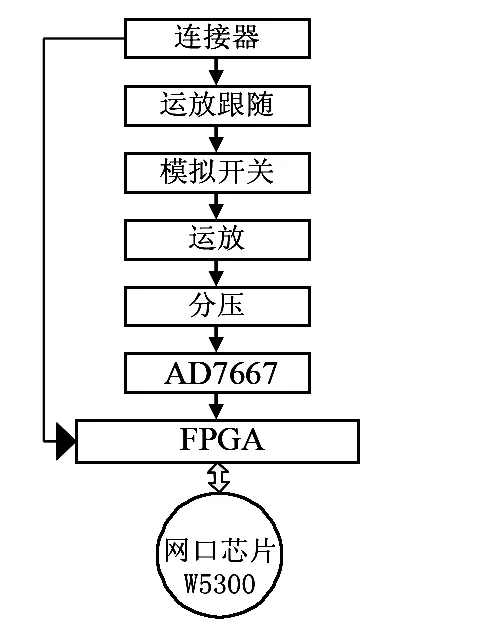

加速度传感器数据采集传输系统的硬件总体框图如图1所示。主要采用了连接器、运放跟随、模拟开关,AD 控制模块AD7667,FPGA 主控芯片和以太网数据传输模块W5300。

FPGA 芯片在该系统中主要完成对采集到的信号进行预处理控制、数据接收,控制A/D 转换芯片把模拟信号转换成数字信号,并且按照自定义的帧格式通过网线传输到计算机。

W5300 网口芯片是处理主机访问网络媒体的操作,把来自FPGA 的数据包封装成帧,在编码成信号,发送到网络上。W5300 内部集成了TCP/IP 内核和微控制器,使其能满足高速通信的需求。

图1 硬件总体框图Fig 1 Overall block diagram of hardware

1.2 A/D 转换电路设计

A/D 转换器是采集传输系统电路部分的核心,在整个系统中有不可或缺的地位。高精度、低功耗的ADC 是数据高效采集的保证。AD7667 具有非常高的采样率模式,用于异步应用的快速模式和为了低功耗应用的电源减少模式(Impulse 模式)。

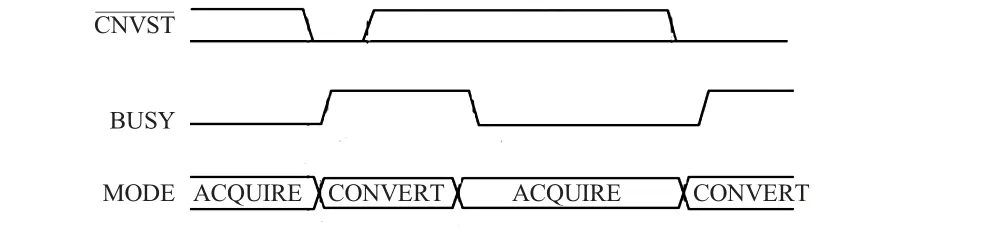

在Impulse 模式下,可以自动进行初始化转换。根据时序图2 所示,在BUSY 低的时候也保持低电平,这时AD7667 为控制采集阶段,并自动启动一个新的转换。通过保持为低电平,AD7667 通过自身使转换进程运行。需要指出的是,当BUSY 变低的时候模拟输入必须保持不变。另外,在上电时,一旦要启动转换过程就要变低。在这种模式下,AD7667 可以超过Impulse 模式下的666kSPS 的运行速度的限制而稍微更快一些。

图2 AD7667 基本转换时序Fig 2 Basic conversion timing of AD7667

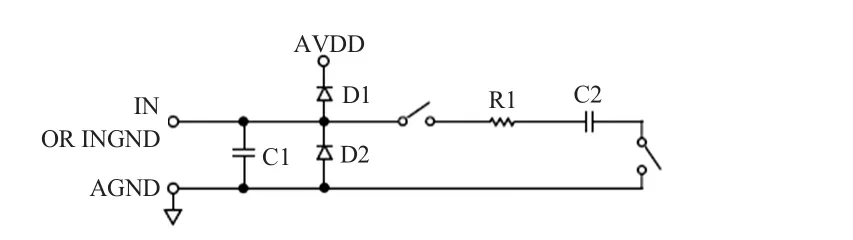

AD7667 的等效模拟输入电路图如图3 所示,两个二极管D1,D2 为模拟输入端IN 和INGND 提供ESD 保护。在采样阶段,模拟输入IN 的阻抗可以建模为由电容器C1 和由电阻器R1 串联形成的网络和C2 组成的并行连接。C1是主要引脚电容器,R1 的阻值为168Ω,是一个由一些串行电阻器组成的集总元件。C2 的电容值为60 pF,主要是A/D 转换芯片的采样电容器。在转换过程中,开关被打开,输入阻抗被限制到C1。R1 和C2 组成了单极的低通滤波器,从而降低不良叠效应,限制了噪音[3]。

图3 等效模拟输入电路Fig 3 Equivalent analog input circuit

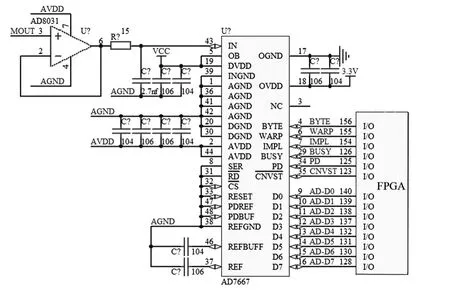

其与FPGA 的电路连接图如图4 所示。

图4 A/D 转换连接图设计Fig 4 Design of A/D converting connection circuit

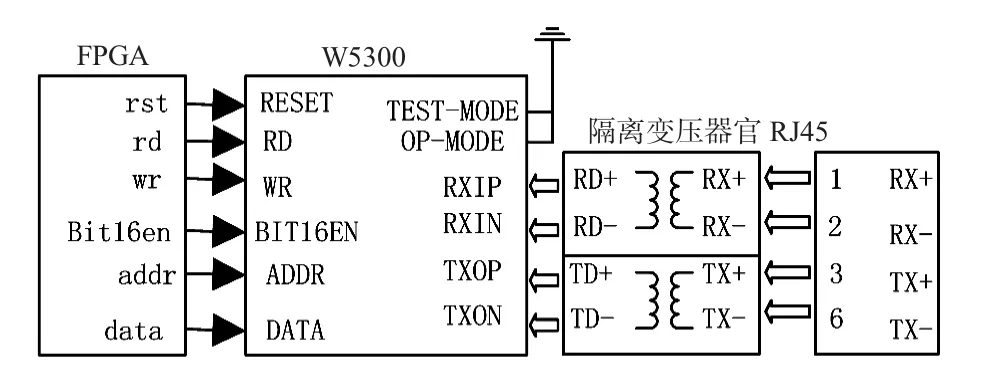

1.3 以太网传输接口设计

以太网的设计主要是通过FPGA 设置BIT16EN 信号为高电平,实现W5300 的16 位数据总线工作模式,采用直接寻址方式。为了提高数据传输的抗噪声能力和数据的稳定性、传输距离等问题,W5300 和RJ45 之间采用网络隔离变压器进行连接,提高了以太网高频的要求,同时有效地保护了接口电路[4]。W5300 网络接口的主要硬件连接原理图如图5。

图5 以太网接口设计原理图Fig 5 Principle diagram of ethernet interface diagram

2 系统软件设计

VC++是一种集成开发环境,提供了MFC 类库。MFC是微软公司对大部分标准的Win32 API 函数的封装,提供了图形环境应用程序的框架和创建应用程序的组件。MFC操作系统界面简洁,占用资源少,操作方便,软件本身提供基于传输层TCP 和UDP 协议的网络通信接口。所以,采用MFC 进行上位机软件设计。

2.1 数据通信

在数据采集传输系统的软件设计中,采用以太网进行通信,为了减少通信的误码率提高通信的成功率与准确率,采用TCP/IP 通信协议进行以太网数据通信,由于传输速度较快,因为采用UDP 的传输方式,为了保证数据传输的可靠性[5],制定了相应的数据帧格式,保证了数据的有效性。

数据帧格式主要由数据包的帧头、数据包大小、数据内容、校验和、帧尾五个部分构成。

W5300 即为发送端,其IP 地址是172.0.0.100,PC 作为接收端的IP 地址是172.0.0.200,网络连接成功以后就可以进行数据的收发。上位机对网络进行设置,包括目标IP 地址、端口号、接收和发送缓冲区大小、分配各Socket 的工作模式[6]。

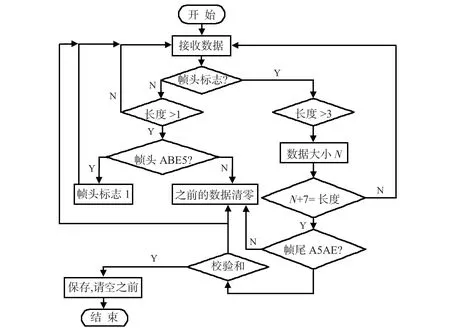

2.2 数据协议分析

根据接收到的数据,上位机进行实时的协议分析。通过读取接收缓冲区中的数据,对接收到的字符串进行处理。协议分析流程图如图6 所示。

图6 通信协议分析流程图Fig 6 Flow chart of communication protocol analysis

3 试验与结果

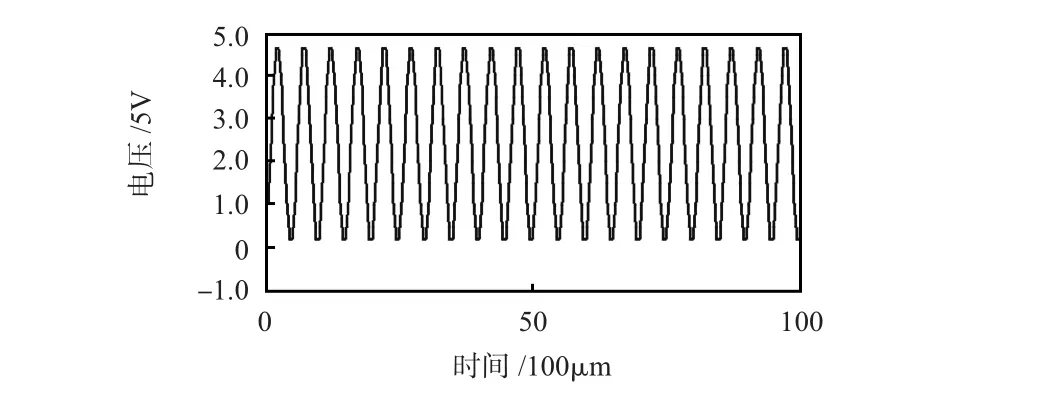

试验在温度、湿度、振动三综合试验平台上,对标准传感器进行数据采集。在温度为20 ℃,湿度为10%RH,加速度为5 gn,振动频率为2 kHz 的条件下进行正弦扫频试验,波形图如图7 所示。

在正弦扫频试验时,输出电压是0~5 V 的正弦波,采用标准传感器采集数据传输给上位机,虽然有外界影响因素,但是通过采样值利用最小二乘法拟合显示效果比较良好,与振动台显示出的波形几乎一致。经过分析,本系统的数据采集系统对MEMS 加速度传感器的数据能精确地显示、采集,能满足军事、工业等远程数据通信系统的需求。

图7 数据采集波形图Fig 7 Data acquisition waveforms

4 结束语

本试验利用FPGA 作为主控芯片获取存储数据,通过选用AD7667 进行A/D 转换,利用W5300 使FPGA 与网口进行数据传输,基于网口与电脑的连接利用上位机软件对数据进行处理。使用以太网的传输方式,提高通信的效率。FPGA 芯片的选择和AD7667 与W5300 的搭配,提高了数据传输存储的效率,减小了电路板体积,上位机进行数据处理提高了运算速度,对于传感器的标定有较高的参考价值。

[1] 侯俊杰.深入浅出MFC[M].2 版.武汉:华中科技大学出版社,2001.

[2] 孙 文.多通道数据采集系统的设计与实现[D].长沙:湖南大学,2013.

[3] 孟祥娇,张会新,崔永俊,等.基于FPGA 和AD7667 的16 路采编传输系统设计[J].自动化与仪表,2012,27(11):5-7.

[4] 张 勇,甄国涌,王丽莉,等.基于W5300 的以太网数据传输硬件设计及优化[J].化工自动化及仪表,2011,38(8):1-3.

[5] 方 宁.基于以太网的远程数据采集与数据传输[D].成都:电子科技大学,2005.

[6] 陈 峰.实时信号数据采集系统的研究与设计[D].上海:上海交通大学,2010.