通用鱼雷合作声信标信号发生器设计与实现*

尚 凡 李 帅

(91388部队94分队 湛江 524022)

通用鱼雷合作声信标信号发生器设计与实现*

尚 凡 李 帅

(91388部队94分队 湛江 524022)

针对原有鱼雷合作声信标信号产生电路使用分立元件设计实现,长期服役可靠性下降、功能单一、体积庞大等缺点,提出借助大规模集成电路,采用“单MCU方案”设计实现了新型数字化信号发生器。该信号发生器性能与原系统完全兼容,在大幅提高可靠性与可维修性的同时,提供了信号体制设定功能,增强产品使用的灵活性;采用多种电气隔离手段,确保其能够在强电磁干扰环境中可靠工作。

鱼雷合作声信标; 通用信号源; AVR单片机; 电气隔离

Class Number TJ630.6

1 引言

声自导鱼雷是潜艇平台不可或缺的水下重要杀手锏武器。为保障各型鱼雷顺利开展海上试验,需建设配套的雷上合作声信标。该信标装备安装于被测鱼雷雷体上,在鱼雷航行时,按照特定信号体制发射合作声信号,配合靶场其他测量系统完成鱼雷水下航行弹道、末弹道的测量任务。现有雷上信标为20世纪80年代英国同类装备的仿制产品,其内部电路均采用分立元件组成,不但体积庞大、功能单一,使用灵活性差,而且长期使用后其可靠性程度显著下降。因此,本文提出借助现代电子技术,设计实现新型合作信标通用数字化信号产生器。

2 信号发生器功能及技术指标

在兼容原有合作信标装备前提下,为满足不同试验任务需求,研制模块需要实现的各项功能与技术参数有:

1) 能够不改变原有时统设备接口功能的前提下,实现强电磁环境下的时间同步功能,同步精度小于5μs;同步后,3小时内同步精度优于200μs。

2) 能够按照信号体制设置参数与鱼雷航深信息,连续输出低频段与高频段同步窄脉冲信号。

3) 能够通过硬件开关或检查台软件两种方式,更改高低频段信号体制。低频通道周期可选,频率可选,单双脉冲可设置;高频通道可设置是否关闭,并选择单双脉冲。

4) 能够实时记录鱼雷航行深度信息,并事后可通过串口总线将数据上传至检查计算机。

3 模块方案设计

根据模块功能与参数指标,给出三种实现设计方案:

3.1 单FPGA方案

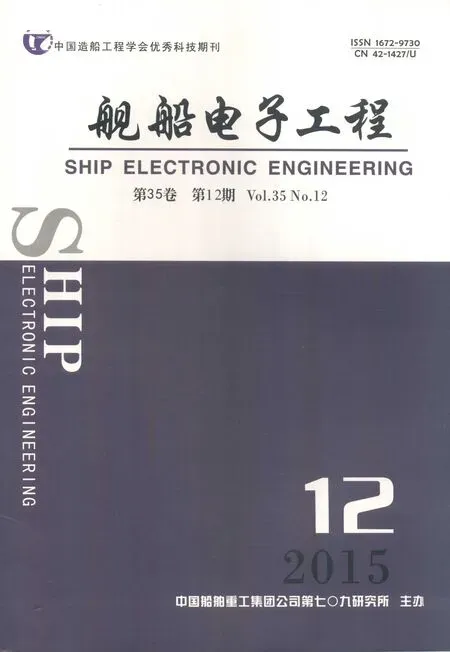

图1 单FPGA方案框图

如图1,使用一片现场可编程门阵列(FPGA)芯片作为主控芯片,使用Verilog硬件语言在芯片内部实现信号生成模块、异步串口通讯模块、ADC接口逻辑模块以及Flash芯片接口模块等。根据FPGA芯片内部工作原理,可认为其是由大量数字逻辑门及触发器组成,因此,特别适合用于数字脉冲分频、计数及双脉冲信号生成等应用。但由于其内部没有集成模拟数字转换器、FLASH储存空间,必须引入ADC与FLASH芯片完成模块功能。

该方案优点:

1) 只使用一枚FPGA作为主控芯片,硬件结构较为简单,可靠性较强。

2) FPGA芯片工作原理特别适合信号源模块中的时钟守时、数字脉冲信号分频计数、双脉冲信号生成及信号调制等任务。

缺点:

1) FPGA内部没有集成模拟数字转换器及Flash储存器,必须引入ADC与FLASH芯片完成模块部分功能。

2) ADC、UART及Flash接口逻辑模块内部逻辑关系复杂,设计及调试难度较大。

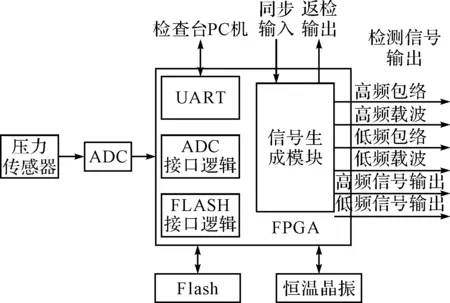

3.2 FPGA+MCU方案

为充分发挥FPGA芯片在数字脉冲信号生成方面的优势,简化其他模块接口逻辑设计难度,如图方案2,引入一枚微控制器MCU模块负责深度信号采集、处理、保存和与计算机通讯等任务。其基本工作原理是:上电后,MCU首先按照原有的设置参数配置FPGA芯片;FPGA内部信号生成模块完成时钟同步与守时功能;MCU根据深度信息是否过深度门限,打开或关闭SAT及MDT信号输出;MCU将采集到的深度信息经滤波后,通过通用IO口送给FPGA芯片,以控制双脉冲时间间隔;MCU在主循环中接收处理检查台串口信息,并记录深度信息至内部Flash中。

图2 FPGA+MCU方案框图

方案优点:

1) 由于MCU的引入,在充分利用FPGA芯片完成信号生成任务的同时,保证其内部时序逻辑简单可靠,将逻辑较复杂的功能交由MCU完成。

2) 利用MCU丰富的外部模块资源(如ADC、Flash、UART等),使用软件方式完成深度的采集、处理及保存功能,并实现与检查台PC机通讯功能。

3) 在实验室状态下,可使用MCU内部定时器资源对FPGA输出信号包络、载波进行信号检测,完成系统检测功能。

缺点:

1) 同时使用MCU与FPGA两枚主控芯片,系统软硬件复杂度提高、可靠性下降,当MCU出现死机等情况时,FPGA也不能按照设置状态正常工作。

2) 当使用MCU完成信号包络、载波检测功能时,MCU软件复杂度较高。

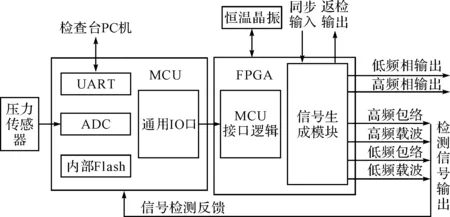

3.3 单MCU方案

另一种方案是除去FPGA芯片,只采用一枚MCU作为主控芯片来完成时统同步、守时、深度采集处理、高低频通道信号生成、串口通讯等所有模块功能。如图3所示,该方案工作原理为:上电后,MCU按照原有信号参数,配置内部计数器模块,输出高低频通道载波信号,打开同步中断允许;MCU根据深度信息是否过深度门限,打开或关闭脉冲包络产生中断允许;根据鱼雷航深信息设置信号双脉冲间隔。

方案优点:

1) 只是用MCU模块所有功能,硬件结构最为简单,不需要外部扩展ADC及Flash芯片,相同条件下硬件可靠性只受MCU元器件影响。

图3 单MCU方案框图

2) 舍去了复杂的接口电路与软件设计工作,充分使用MCU软件控制灵活的特点,系统实现工作量较小,最适合实验室原理样机研制。

缺点:

1) 由于MCU内部定时器作为通用资源已经固化在芯片内部,其完成两路双脉冲信号生成任务时灵活性较FPGA弱。在MCU选型时,应选择内含计数器功能强大、配置灵活且能够直接生成PWM信号的元器件。

2) 使用MCU完成双脉冲信号生成功能,不可避免地需要实时根据航行深度使用软件修改定时器配置寄存器,更改脉冲边沿位置。可能存在因中断或软件编写不当导致的信号输出错误,因此,软件的编写需要融入一定技巧确保任何情况下信号输出稳定可靠。

4 系统硬件框图

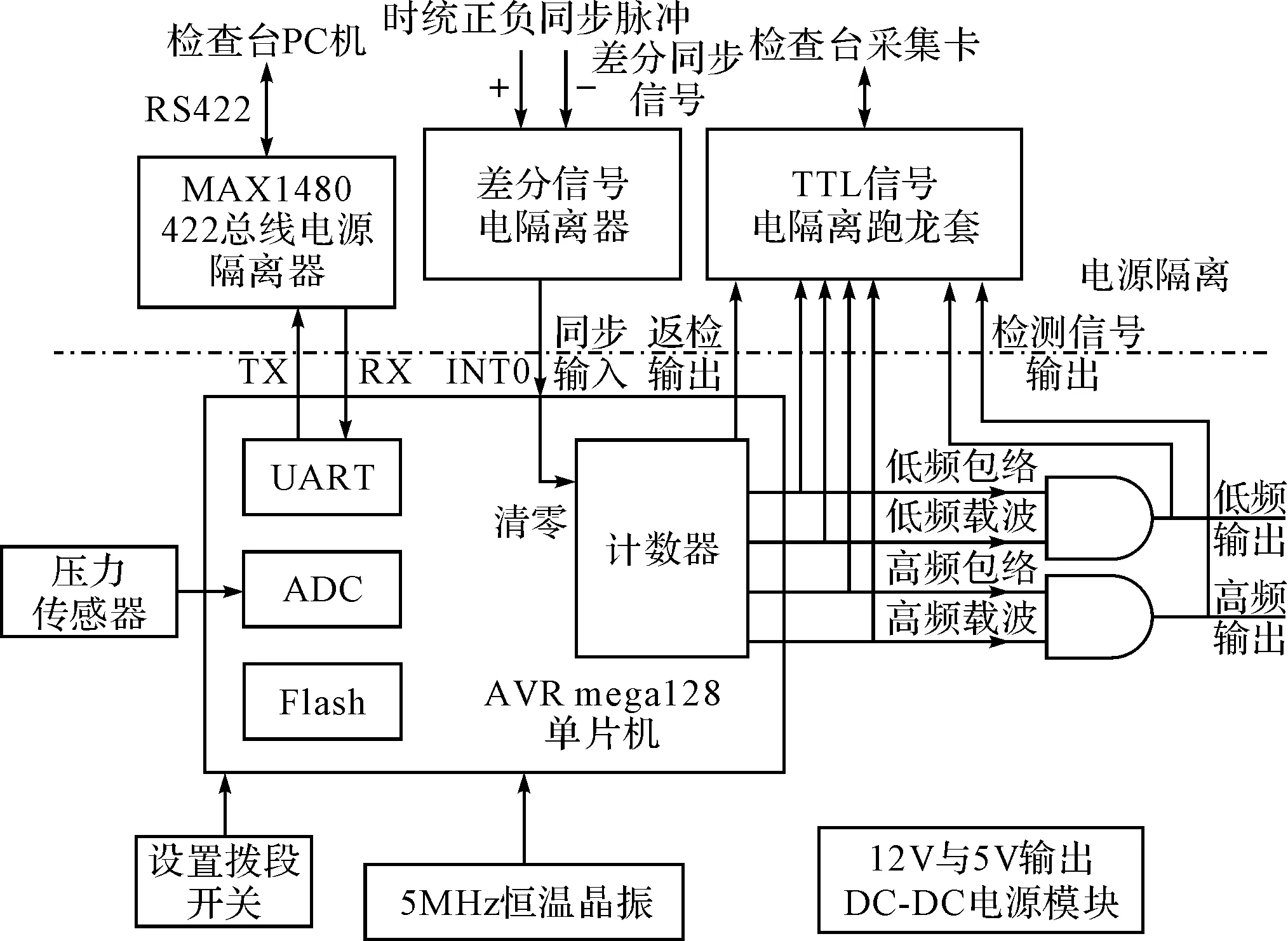

综合考虑设计三种方案优缺点,设计采用“单MCU方案”完成合作信标通用数字信号产生模块原理样机工作。模块硬件框图如图4所示。

MCU采用ATMEL公司生产的AVRmega128单片机,该芯片内部集成有128kB Flash储存空间,四个独立的计数器单元(每个计数器包含三个PWM信号生成单元),AD转换器,UART模块等丰富的内部资源较适合本项目应用。设计中选择不稳定度小于1×10-9的5MHz恒温晶振作为单片机芯片时钟,确保了系统同步守时精度与信号产生精度。其内部资源分配为:使用“外部中断0(INT0)”完成时钟同步功能;使用内部“计数器1(TCNT1)”完成守时、返检、高低频通道包络生成功能;使用“异步通信单元0(UART0)”完成与PC机通讯功能;使用“模拟数字转换器通道0(ADC0)”完成航行深度采集功能;使用内部Flash数据空间保存深度信息。

在不更改时统设备原有接口情况下,同时使用其±5V同步脉冲作为差分信号输入合作信标系统,完成信号同步动作。能够大幅提高时钟同步可靠性,确保系统在强电磁环境下亦不会发生误同步现象。

图4 通用合作信标信号产生模块框图

采用全双工的RS422总线实现与PC机通讯功能,与RS232总线相比,在不需要更改PC机检测软件的前提下,大幅提高总线通讯可靠性与传输速率。

“差分同步信号”转“TTL同步信号”,TTL电平返检信号与检测信号输出及RS422电平转换等硬件单元,均使用具有电源隔离功能的成品模块或芯片,彻底将合作信标系统、雷体、检查台系统地线进行隔离,确保鱼雷航行中或实验室检测时,系统与外部系统相互电气干扰。

使用硬件开关与检测软件相结合的方法,完成信号体制的选择功能。硬件开关设置通道拥有最高权限,若使用硬件开关设置,软件设置参数将自动失效。确保在鱼雷技术准备时,若检查台计算机出现问题,也能对合作信标完成信号体制配置功能。采用5V与12V DC-DC模块为系统供电。12V电源为恒温晶振、压力传感器供电,5V电源为信号源其他芯片供电。在单片机外部,使用74LS00与非门完成信号调制。

5 设计难点

由于原理样机采用“单MCU方案”方案,而没有采用更加灵活的FPGA芯片完成低频、高频两通道双脉冲信号生成功能,因此,设计难点在于如何充分发挥单片机内部资源特别是定时器资源,可靠完成信号源模块要求的信号产生、时间同步及守时等功能,并确保软件操作不会破坏信号连续产生的稳定性。

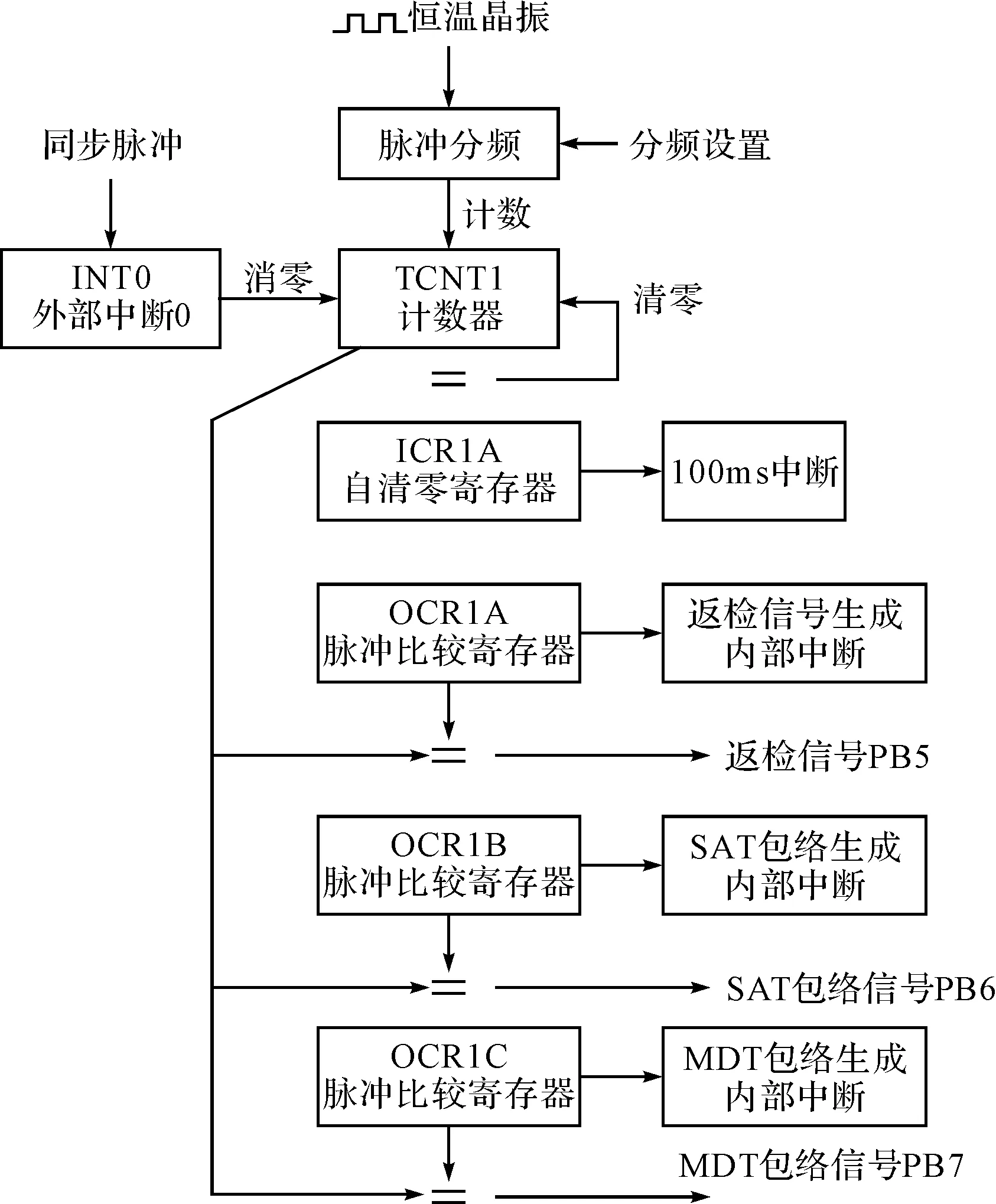

AVRmega128单片机每部含有两个16位计数器与两个8位计数器单元,每个计数器又包含一个自清零寄存器ICR和三个脉冲比较计数器OCR可完成PWM信号生成功能。本文使用一个16位计数器(TCNT3)产生f1的低频载波信号,一个8位计数器(TCNT0)产生f2的低频载波信号,一个16位计数器(TCNT1)完成同步、守时、返检输出、高频通道与低频通道的包络产生功能。图5为定时器1(TCNT1)工作原理框图。

图5 定时器1(TCNT1)工作原理框图

其工作原理描述如下:

1) 恒温晶振输出的5MHz基准脉冲作为单片机系统主频引入MCU后,通过预分频器(÷8)送入计数器1。

2) 计数器1对分频后的信号连续计数,并根据设置在与自清零寄存器ICR1A相等(ICR1A=62500)时自动清零,并给出中断信息(100ms中断)。以100ms时间间隔完成系统守时功能。

3) 在外部中断接收到同步信号时,对计数器1异步清零,完成系统同步功能。

4) 脉冲比较计数器OCR1A、OCR1B、OCR1B与计数寄存器TCNT1比较,相等时,硬件自动产生返检或包络信号脉冲上下边沿,并输出到芯片IO口,完成系统低频段、高频段通道包络及返检信号输出功能。

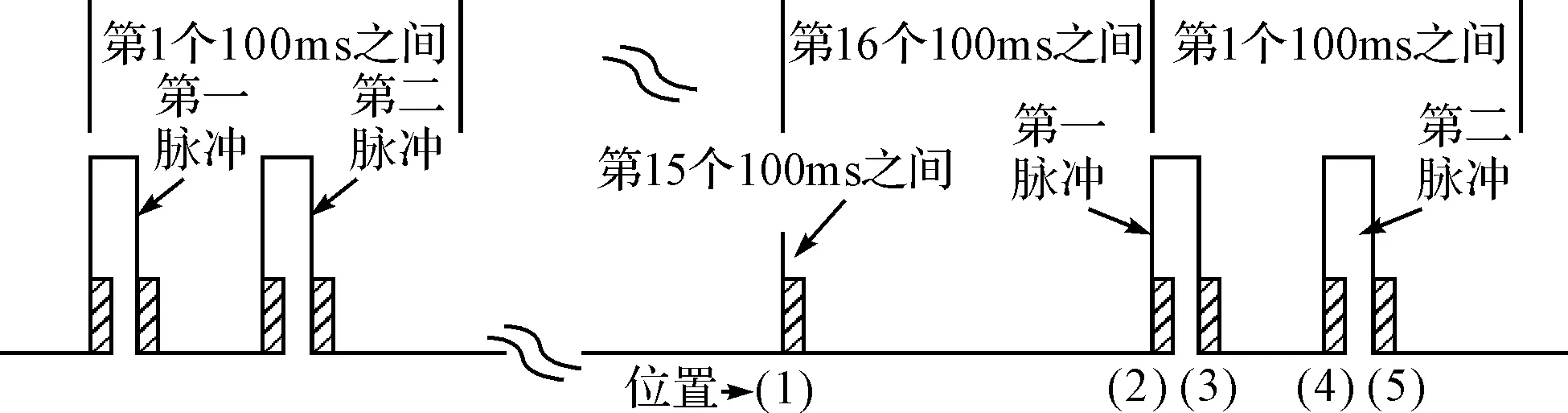

假设低频段周期设置为1.6s,以低频段脉冲包络为例介绍双脉冲包络信号产生的软件设置原理。

图6 脉冲包络产生原理示意图

图6中,低频段脉冲周期为1.6s,包含16次100ms中断信息。

1) 每个低频段周期内,当第15个100ms发生时(即位置(1)),打开脉冲比较计数器OCR1B中断,设置当计数器为0时,生成上升沿;

2) 当OCR1B第一次发生(即位置(2)),重新设置OCR1B,于1.24ms(脉宽)时刻生成下降沿;

3) 当OCR1B第二次发生(即位置(3)),第一个包络脉冲已经生成,读取程序主循环中ADC测量结果(即深度信息),计算并设置第二脉冲上升沿位置;

4) 当OCR1B第三次发生(即位置(4)),重新设置OCR1B,于“位置(3)时刻”+1.24ms(脉宽)处生成下降沿;

5) 当OCR1B第四次发生(即位置(5)),该低频段周期双脉冲包络生成完毕,关闭OCR1B中断允许,关断脉冲生成功能,等待至第15个100ms发生时进入步骤1)。

返检信号、高频段包络生成方法基本一致,不再赘述。该方法巧妙地使用了定时器1内部集成的丰富中断资源与PWM生成功能,在每个脉冲边沿发生之前在中断服务程序中设置边沿位置及方向,能够确保信号生成不会因为软件操作存在不确定的时延。另外,由于留有充分的时间余量,因此即便有突发中断产生也不会影响脉冲边沿的生成,确保包络生成稳定连续可靠。

6 结语

新型鱼雷声信号源原理样机能够实现同步、守时、低频段与高频段通道双脉冲信号生成等功能。3小时守时精度优于100μs,双通道双脉冲调制后信号输出正常可靠。双通道脉冲信号经死区控制电路二次调制后送入功率放大电路,功放输出稳定可靠。由于采用差分信号同步,差分总线信息功能,并进行了完全电气隔离,该产品抗干扰能力显著提高,在强电磁环境下也能可靠工作。增设的信号体制设定功能工作可靠,配置灵活方便,能够满足双雷齐射试验需求,有较好的实用价值。

[1] 翼大雄,刘健,陈孝桢,等.基于LBL声信标的AUV快速精确定位[J].声学技术,2009,28(4):476-479.

[2] 于海春,余华兵,孙长瑜.基于虚拟仪器技术的通用水声信号发射系统设计[J].应用声学,2009,28(2):116-120.

[3] 曲加圣,杨松.便携式水下声信标探测定位设备技术设计与实现[J].舰船科学技术,2012,34(4):75-78.

[4] Kuon I, Rose J. Measuring the gap between FPGAs and ASICs[J]. IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems,2007.

[5] SST. SST26VF016 datasheet[EB/OL]. http://ww1.microchip.com/downloads/en/DeviceDoc/25017A.pdf,2011.

[6] Chen, H, Liu, Z, Su, L, et al. Design of the SPI interface of 10-gigabit ethernet with FPGA[C]//Conference on Network Architectures, Management and Applications Ⅱ,2005.

[7] Atmel Corportation. AVR MCU ATmega128 Data Sheet[EB/OL]. http://www.atmel.com/dyn/resources/prod_documents/doc2467.pdf,2009.

[8] R.L. Clark, A. Scalpi. Design considerations of vacuum-sealed OCXO’s for high reliability applications[C]//Proceedings of Tricomm,1996.

[9] MAX1480A-1490BDatasheet[EB/OL]. http://datasheets.maxim-ic.com/cn/ds/MAX1480A-MAX1490B_cn.pdf,2005.

[10] 王红亮,杨晓.AVR单片机与串行A/D的SPI接口设计[J].电测与仪表,2008,45(513):45-48.

Design and Realization of Universal Signal Generation Circuit of Torpedo Synchronous Acoustic Beacons

SHANG Fan LI Shuai

(Unit 94, No. 91388 Troops of PLA, Zhanjiang 524022)

A digital signal generation circuit with VLSI and Single MCU scheme is designed to overcome the disadvantages of existing signal generation circuit designed with discrete component in torpedo synchronous acoustic beacons, such as reducing reliability with long-term service, single function, huge volume and so on. The digital signal generation circuit with the function of set signal parameters is not only completely compatible with original system, but also has the advantages of used flexibly, high reliability and maintainability. Meanwhile, manifold electrical isolation methods are used to insure the digital signal generation Circuit working reliably in strong electromagnetic interference environment.

torpedo synchronous acoustic beacons, universal signal generation circuit, AVR MCU, electrical isolation

2015年6月7日,

2015年7月19日

尚凡,男,助理工程师,研究方向:水声信号处理。

TJ630.6

10.3969/j.issn.1672-9730.2015.12.038