基于硬件支持的可调加密实现方案

赵福祥

(西安外事学院工学院,西安 710077)

基于硬件支持的可调加密实现方案

赵福祥

(西安外事学院工学院,西安 710077)

针对可调加密模式在实际应用中较难生成动态因子和管理密钥的问题,采用复合MPSoC平台硬件支持的方法,应用混沌密码、动态组密钥与硬件密钥防护等技术,提出一种改进的可调加密方案。通过增加小规模硬件部件以换取可调因子与加密的并行计算,支持受资源限制嵌入式设备应用,实现动态密钥管理。实验结果表明,该方法通过并行计算可缩短系统的整体运行时间,提高系统整体效率。

可调加密模式;嵌入式安全;混沌映射;硬件支持;混沌密码

1 概述

数据的安全存储是信息机密性应用的重要保证。可调加密模式除了对存储数据加密外,还提供对设备元数据的加密,从而提高了抗结构分析的安全强度[1-2]。但是存储设备的管理部件都是嵌入式处理器,同样也应用在电子播放器、家用电器、手机电话、掌上电脑、智能卡、微型传感器、网络路由器、汽车与飞机的控制等设备中,由于智能微控制器的应用,大幅度提升了人与机器的交互作用,让应用的技术流程变得顺畅。但嵌入式设备被大量用到个人、商业及国防设施中后,跟随而来的安全问题就跃升为关注的焦点[3]。嵌入式设备与物理环境相关,攻击会从单纯的数据转伸到了实物,风险远高于单纯信息系统。而其本身也要存储、接入或传输敏感性的数据,也需要同等安全保障。加之网络化是嵌入式微控制性能发挥的最佳选择,开放性所带来效益与攻击都不可回避。可以说嵌入式技术是继通信和计算机之后又一项基于成熟信息技术的先进控制与处理平台,也形成专业的设计特性[4]。目前嵌入式安全巨大需求已经使其成为密码与安全学科中最活跃的分支,所研究的方向也都更清晰集中到固定方向[5],包括轻重量密码学、物理性安全、AD-Hoc网络安全、安全操作系统、射频识别标签等。尽管如此,嵌入式安全不可能移植常规的加密方法,难点是掌握特定应用的技术特性。而加密算法都以大量的数据计算为基础,若没有恰当的实现平台,仍然会颠覆算法理论的优势。合理的系统防御策略与精巧优化性能正是解决难题的突破口。综合实现算法的难度、效率与兼容性,选择复合SoC是实时嵌入式加密

算法的最佳平台[6],也是用于实现可调加密方案最优的基础[7-8]。混沌密码满足实时性,且有良好的随机性,但其密文均匀性和操纵稳定性都有不佳,其实现也并非针对数据存储[9]。为嵌入安全取得合理的配置与更高安全强度,本文提出基于硬件支持的可调加密的实现方案。

2 方案的模型结构

本文方案的目标是实现嵌入式自身安全与数据实时加密的需求,涉及嵌入式防护与密文抗结构分析等,各项实用关键性技术及组合都应围绕目标设置。方案的模型结构采用下面的3种方法。

2.1 可调加密的扩展

通过对已有可调加密方案的分析可知,可调模式算法本质是在原加密函数中增加了可调因子,目标是使组合密钥在加密过程中增加确定的随机增量,由加密过程的伪随机作用,使附加增量在密文中产生扰动,以取得抗结构分析性攻击性能。厘清新模式算法概念与形式描述对方案十分有益,既能透视其不足,还能感知其计算难点。可调加密模式的形式化表示为E:K×T×P→C,即使明文空间DP数据映射到对应的密文空间若任给K∈K和T∈T,则是长度保持的确定性置换,其中,K是密钥空间;T是可调因子集合。加密算法E的逆是解密算法D:T×K×S→S,即使密文空间DC数据将映射到明文空间,其中,当且仅当定义Perm(S)为所有置换φ:S→S的集合,再定义PermK(S)为所有置换φ:K×S→S的集合,使得φ(k)∈PermK(S)对所有k∈K成立。在应用层面可调因子集合可以取自连续密文分组区块的位置索引集,因此对于组合密钥,定义PermT(K)是所有函数φ:T×K→K的集合,使得φ(k)∈Perm(M),而PermT×K(S)为所有函数π:T×K×S→S的集合,且有对任意K∈K,存在PermT×K≌PermK(S)。若密钥固定,而相应可调参数也保持不变,则组合密钥不会产生任何变化。因此,需要把密码扩展成为两维度的算法。

2.2 两维度的加密

兼顾效率与成本,大容量存储器读取应为分组结构,既有利于数据管理,又有利于安全设计效率的提高。在管理方面,分组存储单位可缩短元数据长度,实现存储单位为结构性重复处理的需要。在安全方面,恰当选取存储单位则有利于加密效率真的提高。设存储单位为块,块既做数据操作单位,也兼做加密单位,同时还作为密钥更换单位。可调因子的差异源取自块编号,如此设置只是保证各块间的可调性区分,但根据2.1节的结论,它却不能保证同一块内的区分。因而必须添补时间轴的差异源,形成两维度的加密。

从差异源获取可调因子采用了再密钥的更新方法。为保持加密的前向安全性,主密钥K不直接用于数据加密,而用作再密钥函数Ki=F(K,i)的种子,使主密钥泄露不造成加密数据失效,主密钥寿命得以延长。Ki隐含了密钥与时间相关变化序列,若存在位置变量保持不变,可推导出函数 ΔKi= F(Δs(t)+k)缺少时间成份,即Δs(t)=0,则导出ΔK=F(k)=c,即可得出如下关系:

2.3 动态可调结构

动态可调结构是由块号与独立时间变量构成的函数,以保证密文在相同地址存储时的可调因子取值不同。实际上密文的保存逻辑限制了独立时间成分变量只在新数据写入存储器时才产生变化,而当从存储器读出老的数据值时则不应有任何变化。动态可调结构的计算公式如下:

其中,IDsec是块号;contsec是一个块地址写请求计数器;w/r是一位数字对应于w/r读写信号;c是2次读写过程的间隔,如果它超过了生成密钥的时间,就设为1,否则设为0。

3 硬件支持方案

嵌入式的安全方案需要采用专用软件与硬件的配置,单纯软件在通用处理器上执行,可提供不同实现和连续更新等更优的灵活性,硬件支持却是提高处理性能的根本。密码硬件加速器选择L氏(Logistic)映射实现,具备混沌加密系统的特性[10-11]。

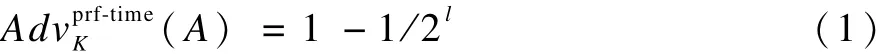

3.1 系统结构与处理监控

本文方案所采用的系统结构如图1所示。系统由3个独立部件构成,包括安全参数存储子系统、复合MPSoC系统和监控子系统。

图1 嵌入式加密系统的数据双向结构

主密钥来自密钥服务器并导出加密密钥,加密数据的安全性依赖这些密钥。为强化安全性,加密算法安全参数都不应该从设备中被泄露,存储在设备中这些密钥和秘密数值需要保护,统称为秘密钥。还有一些根证书的数据不怕泄露但要防止未授权的修改,称为认证数据。

为取得嵌入式安全处理,监控系统用于验证实际处理与原设计代码的差异。采用安全启动机制就可以使嵌入式的系统装载就可达到安全标准。任何不在范围内指令的执行或执行顺序的改变都有可能被认为是攻击。但提高效率的关键是增设可分时的独立部件以加大并行性,下面将叙述硬件加密电路的构造。

3.2 L氏映射改进及量化

L氏映射是度数为2的多项式映射,采用数学形式L氏映射可写为:

χn+1=λ×χn(1-χn) (3)其中,λ为正数。L氏映射依赖于λ的取值。对于λ取值范围在[3.57,4]之间时,输入值的轻微改变就会引起输出值产生巨大的不同。当λ=4时分布更平坦和对称,为了避免L氏映射产生短路径循环而削弱数字混沌密码统计特性,改进 L氏映射将以λ=4时为基础,改变其为有相同的定义域和值域的方程,区间取为[α,(1-α)],得以下方程组:

改进L氏映射输出量(χn)量化为8位的量值yn过程表示如下:

其中,χn(0<χn<1)χn(0<χn<1);aj是每位的值。设定改进L氏映射的实现在以N位硬件结构器件上,限制yn取值仅在最低8位有效位的值,因此 yn可写为:

量化步骤中所截断的更多有效数位实际上都是非线性的,从而增加了任何攻击的复杂性。

图2显示了原 L氏原映射与改进映射的分布对比。

图2 L氏原映射与改进映射的分布对比

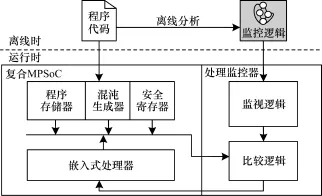

4 硬件密码加速电路

硬件密码加速电路即借助改进 L氏映射为基础,构建实时密码表生成电路,以削减加密算法中软件生成加密密钥所占用的时间。

电路包含了密钥表生成部分和α参数设置两部分,如图3所示。电路的输入为一随机数,可选择8位或16位,随存储块的地址长度而定。

输出则为连续16 Byte~20 Byte随机数表,随后再由计算单元做多个字节纵向的按位旋转,就可获得所需的密码表。

电路的选择控制由 α参数秘密设定,密钥表的取值会随α的改变而不同。

图3 硬件密码加速电路

5 电路仿真验证

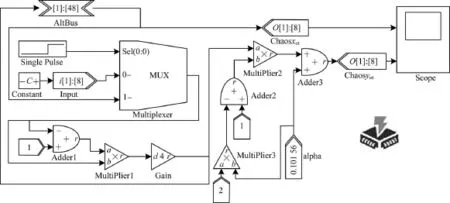

为了验证图3电路模块的正确性,对图L氏原电路的输出χOt和改进输出yOt进行仿真,其时间序列如图4所示。

图4 混沌与改进混沌时间序列

比较图4中2个分图发现,利用DSP Builder设计的电路有效地实现了改进L氏电路的功能。把图形化模块直接转化为Cyclone II系列的EP2C35F 484C8芯片对应的硬件描述语言,再利用QuartusII进行编译,得仿真时序如图5所示。

图5 改进混沌Quartus II仿真波形

其中,yOt为改进L氏电路输出字节。即方案中可调加密,若对存储块号BC=3 125的数据块加密时,则得可调参数值为:

TK=0χC9FC43846B9347856E82844C8725D233

(7)

最后,通过相应的引脚分配后下载完成芯片的编制。

6 方案评估

完成L氏模块构建,即达到了硬件到并行计算实现可调加密的既定目标。密钥更新软件算法中主要依赖安全哈希函数,假设安全哈希函数执行时间为Δt,忽略并行算法切换时间,那么硬件支持算法相对软件密钥更新每个存储块就会节省2Δt的开销。若整个存储器有 n个数据块,整个存储器加密节省的时间就为2nΔt,n取海量则会节省大量的时间。以下将对安全哈希函数的运行时间进行测试,以确定Δt的参考数值。测试平台P4/1.5 GHz/XP,分别对sha256算法的摘要DV=0χ248D 6A61D 20638 B8E5C026930C3E6039A33CE45964FF2167F6ECED D419DB06C1和quart算法的摘要DV=126B75BC AB23144750d08BA313BBD800A4进行计算测试,测试结果如表1所示。

表1 算法各次循环累计时间 m s

表1中sha256算法运行时间约为0.016 m s,quark算法约为3.2 m s,但quark算法为轻重量算法,故取Δt参考值为3.2 m s。

7 结束语

本文提出一个基于硬件支持的可调加密实现方案,主要设计思路是通过增加硬件支持电路实现可调加密中密钥生成算法与数据加密算法的并行计算。实验结果表明,该方法通过并行计算缩短了系统整体运行时间。由于嵌入式安全是一项综合技术,需要通过软硬件的有效结合才能消除流程中的瓶颈难题,这将是本文下一步需要研究的问题。

[1] Liskov M,Rivest R,Wagner D.Tweakable Block Ciphers[C]//Proceedings of CRYPTO’02.Berlin,Germany:Springer-Verlag,2002:31-46.

[2] Abdalla M,Bellare M.Increasing the Lifetime of a Key:A Comparitiveanalysis of the Security of Rekeying Techniques[C]//Proceedings of Asiacrypt’00.Berlin,Germany:Springer-Verlag,2000:546-559.

[3] Hwang D D,Schaumont P,Tiri K,et al.Securing Em bedded System s[J].IEEE Security&Privacy,2006,4(2):40-49.

[4] Ravi S,Raghunnathan A,Kocher R,et al.Security in Em bedded System s:Desingn Challenges[J].ACM Transactions on Em bedded Computing System,2004,3(3):461-491.

[5] Ravi S,Raghunnathan A,Chakradhar S.Tamper Resistance Mechanisms for Secure Embedded Systems[C]//Proceedings of VLSID’04.Mumba,India:[s.n.],2004: 605-611.

[6] Justin M J,Manimurugan S.A Survey on Various Encryption Techniques[J].International Journal of Soft Computing and Engineering,2012,2(1):429-432.

[7] Wolf F.The Future of Multiprocessor Systems-onchips[C]//Proceedings of DAC’04.[S.1.]:IEEE Computer Society,2004:681-685.

[8] Guneysu T,Heyes S,Paar C.The Future of High-speed Cryptography:New Computing Platform s and New Ciphers[C]//Proceedings of GLSVLSI’11.New York,USA:ACM Press,2011:461-466.

[9] Pande A,Zambreno J.Chaotic Encryption Scheme for Real-time Digital Video[J].Journal of Telecommunication System s,2013,52(2):551-561.

[10] 徐正光,田 清,田 立.一类可以产生独立同分布密钥流的混沌系统[J].物理学报,2013,62(12).

[11] 张 波,王光义,韩春艳.基于Logistic映射PN序列的FPGA实现[J].现代电子技术,2009,(7):11-14.

编辑 索书志

Tweakable Enciphering Implementation Scheme Based on Hardware Support

ZHAO Fuxiang

(Engineering School,Xi’an International University,Xi’an 710077,China)

To solve the problem of hard to generate dynamic factor and manage key in practical applications of the enciphering mode,a tweakable enciphering scheme is presented based on hardware support by using hybrid MPSoC implementation and chaotic code and dynamic key and hardware key protect technologies.Parallel computations between acquiring the tweakable factor and executing data encryption are introduced by adding small scale hardware and the overall efficiency of the system is improved.Techniques of resource-constrained application and dynamic key management are applied in the scheme.Experimental results show that the scheme can reduce the run time of system and improve the overall efficiency.

tweakable enciphering mode;embedded security;chaotic mapping;hardware support;chaotic code

赵福祥.基于硬件支持的可调加密实现方案[J].计算机工程,2015,41(10):144-147,154.

英文引用格式:Zhao Fuxiang.Tweakable Enciphering Implementation Scheme Based on Hardware Support[J]. Computer Engineering,2015,41(10):144-147,154.

1000-3428(2015)10-0144-04

A

TP309

10.3969/j.issn.1000-3428.2015.10.027

陕西省教育厅专项基金资助项目(2013JK1146);陕西省自然科学基金资助项目(2014JM 8323)。

赵福祥(1964-),男,副教授、博士,主研方向:密码学,网络与信息安全。

2014-09-15

2014-11-20E-m ail:zhaofuxiang@aliyun.com