基于Verilog HDL的14层电梯控制系统

周细凤,曾荣周,刘美华,孙 静

(1.湖南工程学院 电气信息学院,湘潭 411101;2.电子科技大学 电子薄膜与集成器件国家重点实验室,成都 610054)

基于Verilog HDL的14层电梯控制系统

周细凤1,曾荣周2,刘美华1,孙 静1

(1.湖南工程学院 电气信息学院,湘潭 411101;2.电子科技大学 电子薄膜与集成器件国家重点实验室,成都 610054)

采用Verilog HDL语言,实现了14层电梯控制功能.设计中有2个进程,分别是状态机进程和信号灯控制进程.其中状态机进程是主要进程,信号灯控制进程是辅助进程,两者相互配合完成整个控制过程.整个控制系统采用Quartus II软件仿真设计,采用 DE1的FPGA开发板对所设计的程序进行了硬件调试,由硬件调试结果可看出,所设计的控制系统能实现14层电梯楼层调换功能,且具有很强的实用性和适应性.

Verilog HDL;电梯控制;Quartus II;FPGA

0 引 言

随着城市建设的迅速发展,高层建筑越来越多,电梯的使用变得越来越普遍,已经是宾馆、商业大厦、居民楼、学校等场所必不可少的设施之一.一个完整的电梯系统有八个主要组成部分,分别是导向系统、曳引系统、轿厢、电气控制系统和安全保护系统、门系统、电力拖动系统、重量平衡系统,其中控制系统是电梯的核心部分.

现阶段的电梯控制系统主要采用两种方式,一种是使用微机作为信号控制单元,完成电梯信号的采样、运行状态和功能的设定,实现电梯的自动调度和集选运行功能,拖动控制则由变频器来完成;第二种控制方式是基于FPGA的控制系统.其中微机控制系统虽在智能控制方面有较强的功能,但存在抗扰性差,系统设计复杂,一般维修人员难以掌握其维修技术等缺陷.而FPGA控制系统由于运行可靠性高,使用维修方便,抗干扰性强,设计和调试周期较短等优点,倍受人们重视等优点,已经成为目前在电梯控制系统中使用最多的控制方式.

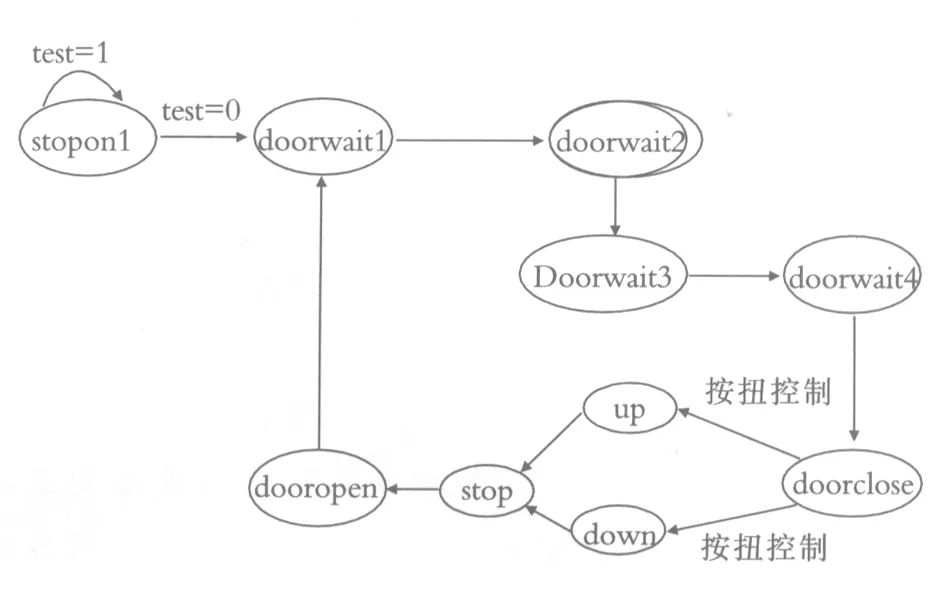

本文采用Verilog HDL语言,实现了14层电梯控制功能.设计中用到了状态机,使控制系统更为简单.设计中有2个进程,分别是状态机进程和信号灯控制进程.其中状态机进程是主要进程,信号灯控制进程是辅助进程,两者相互配合完成整个控制过程.在主进程中定义了10个状态,分别是“stopon1”,“dooropen”,“doorclose”,“doorwait1”,“doorwait2” ,“doorwait3”,“doorwait4”,“up”,“down”和“stop”,在电梯时钟的触发下,通过信号灯信号和当前状态判定下一状态.在信号灯控制进程中,信号灯能反映按键请求情况,它的亮灭是由状态机进程中输出信号来控制的.本文使用Altera公司的Quartus II软件仿真程序,采用DE1的FPGA开发板对所设计的程序进行了硬件调试和测试,由硬件调试结果和软件仿真结果均可看出,所设计的控制系统能实现14层电梯楼层调换功能,实时显示楼层信息,维护更为方便.

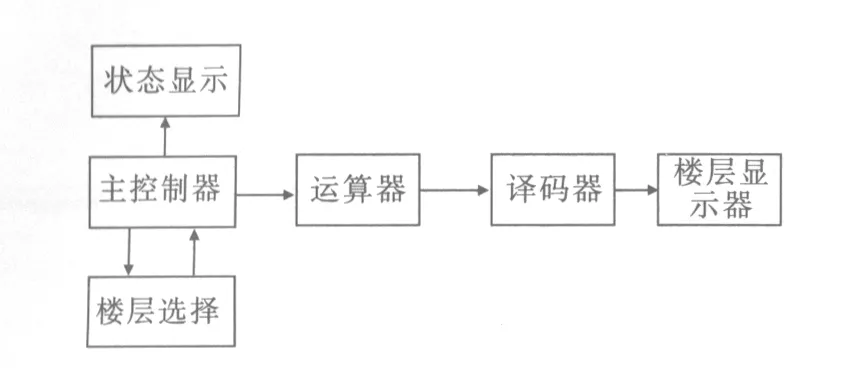

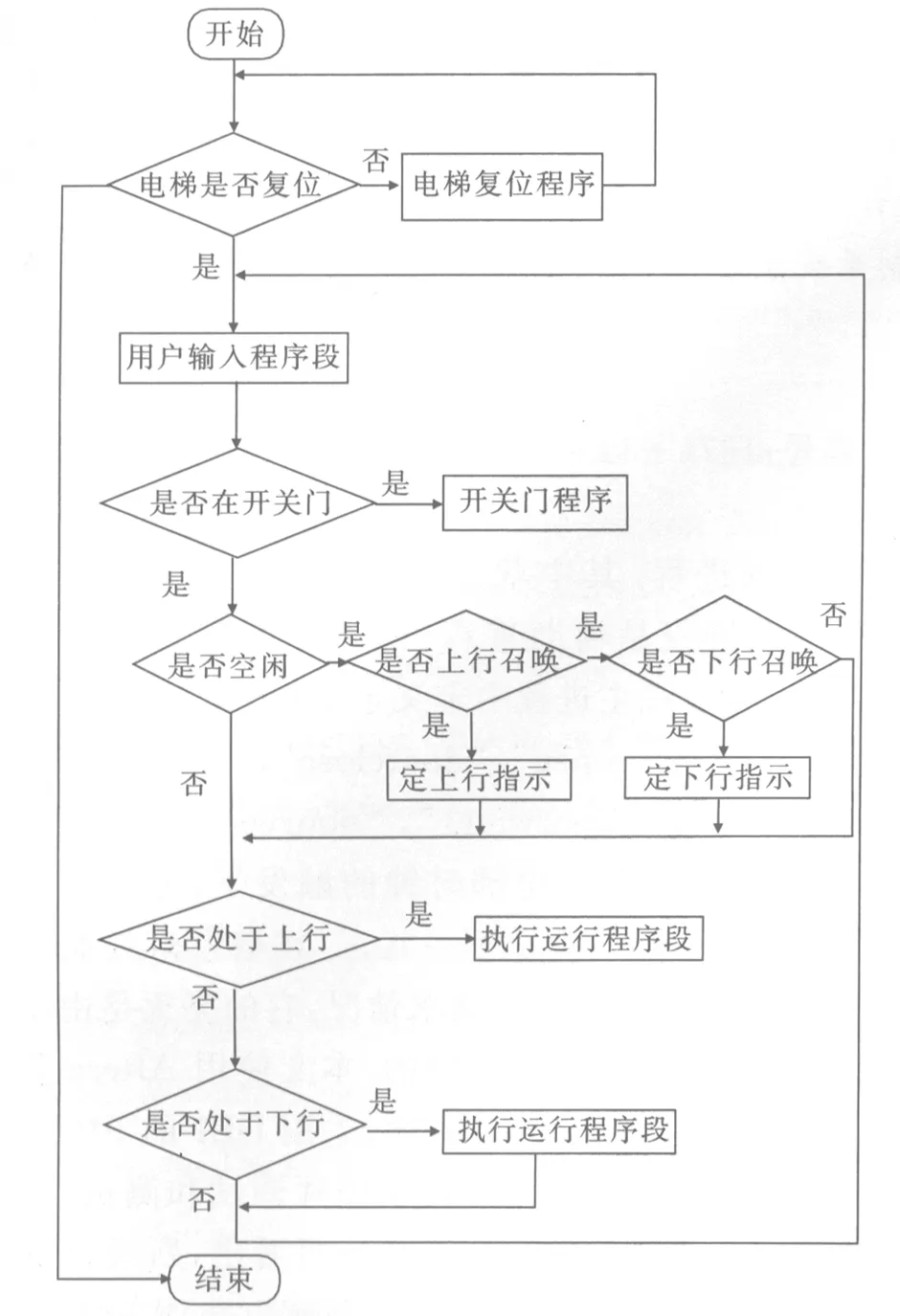

如图1所示,控制器的功能模块包括主控制器、状态显示器、楼层选择器、楼层显示器、译码器以及运算器模块.在这些模块中,主控模块是核心部分,其他模块比较简单.当乘客通过楼层选择器选择所要到达的楼层,信号经过主控制器的处理,电梯开始运行.状态显示器的功能是显示电梯的运行状态,为了显示电梯所在楼层信息,将输出信息先通过运算器处理,再经过译码器译码,最后送到楼层显示器中显示.整个电梯系统运行过程中的控制流程如图2所示.

图1 控制器的功能模块

图2 电梯运行控制流程图

1 14层电梯控制器的设计思路

本文采用状态机来实现主控制器,电梯运行过程中一共有7种状态,分别是“电梯停在1楼(stopon1)”、“电梯停止(stop)”、“电梯关门(doorclose)”、“电梯开门(dooropen)”、“电梯上升(up)”、“电梯下降(down)”、“电梯等待4 s(doorwait)”.在本次设计中,采用1 Hz时钟周期信号来实现电梯上升或者下降一个楼层的时间是1 s的设计要求,但对于“电梯等待4 s(doorwait)”状态来说,如果只有一种状态,电梯只实现了等待1 s的功能,故需要另外添加3种过渡状态,最后状态“电梯等待4 s(doorwait)”由4种状态组成,分别是“doorwait1”、“doorwait2”、“doorwait3”、“doorwait4”.各种状态之间的关系如图3所示.

图3 主控制器的状态图

2 顶层电路设计

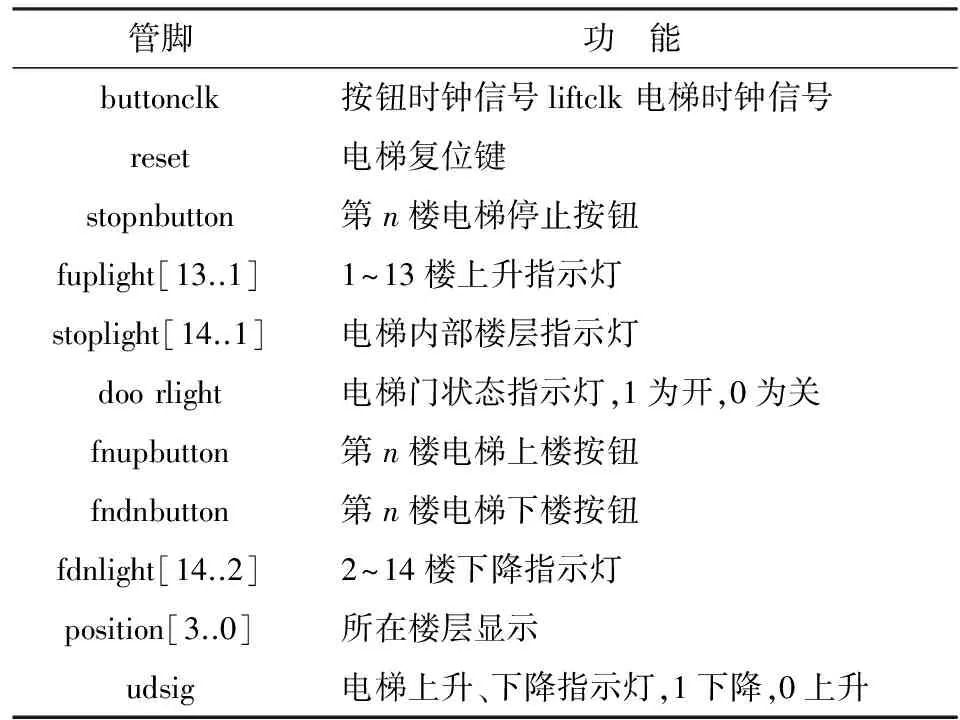

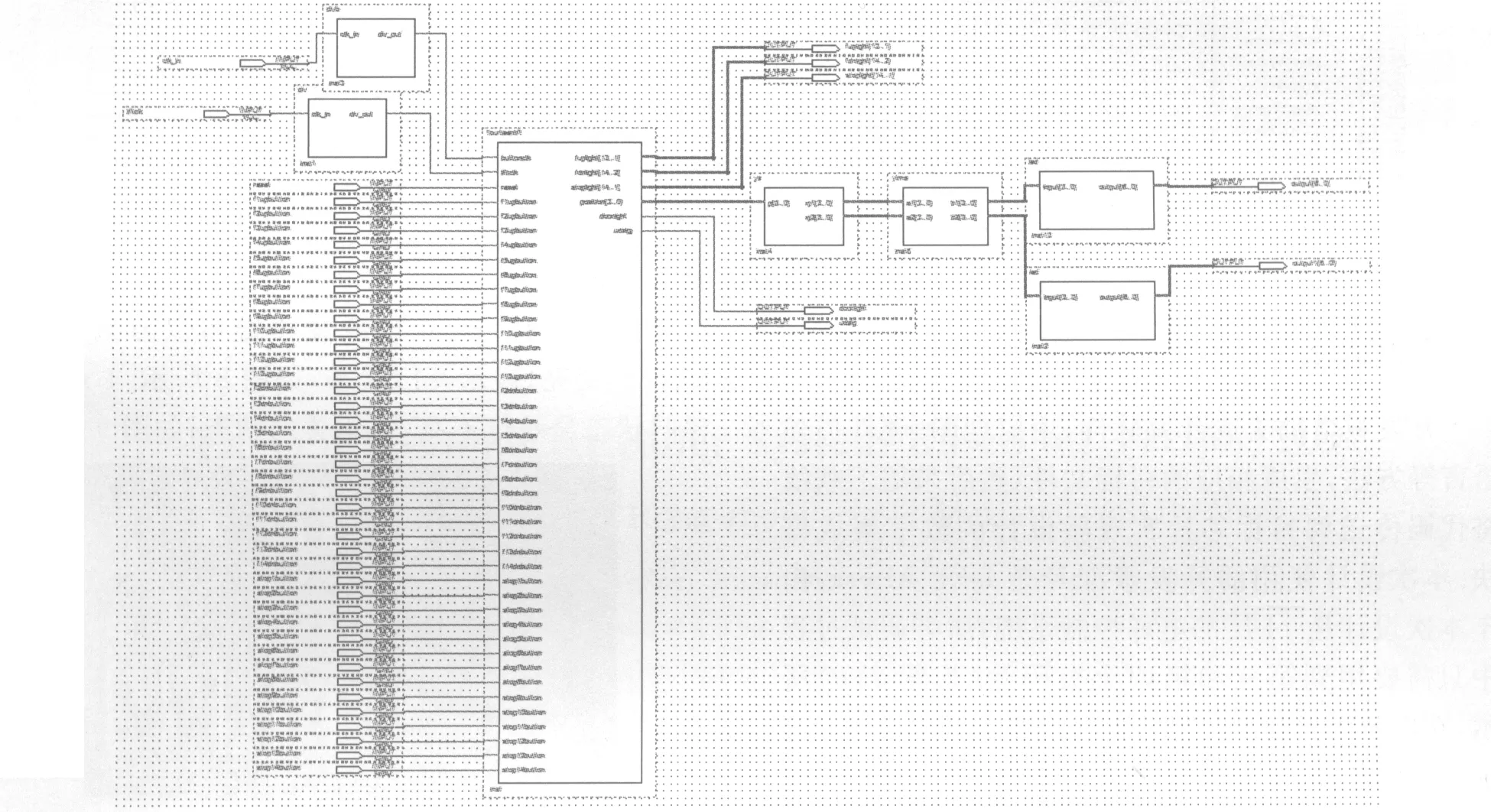

电梯总控制模块是最关键的部分,根据开发板内部时钟信号,采用了2个分频器,由于该电梯系统是14层的,在楼层显示过程中,需要2个数码管显示,因此,采用运算器模块实现此功能,译码模块实现将十进制数转变成4位二进制数,再通过数据显示模块,将4位二进制数转变成共阳数码管对应的电平显示.各个模块之间的联系如图4所示,其中电梯主控制模块各个管脚功能如表1所示.

表1 电梯主控制模块管脚功能

3 主控制模块仿真

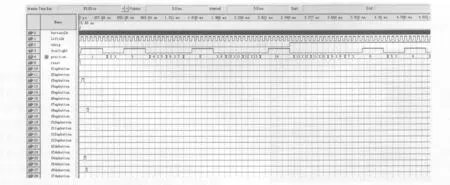

本设计采用Altera公司的Quartus II软件进行仿真和调试.由图5所示的主控制模块仿真结果能清楚的看出,初始时候电梯reset信号有过重置,电梯在3楼和8楼有上楼请求信号,在4楼和6楼有下楼请求,分析position和doorlight可以知道,doorlight为1表示电梯开门,否者为关门,图5中,明显可以观察到,在上升过程中,电梯在1楼、3楼、8楼有开门,对应的按键存在高电平的时间段,故上楼程序运行正确;在下降的过程中,电梯在6楼,4楼有开门,对应的单间存在高电平的时间段,故下楼程序也正常.开门等待时间与未开门楼层时间比是4∶1的关系,楼层上升或者下降1层是1 s,故实现了开门等待4 s的功能.

图4 顶层原理图

在图6中上升请求指示灯fuplight由“00000000000000”变成“0000000000010 0 ”,代表着按键扫描出3楼上升按钮,在未执行完这一操作,相应的位一直保持高电平,系统继续识别按钮,“00000000000 100”变成 “00000010000100”,表示成功识别8楼上升按钮,3楼的上升请求还没要执行完.一样的道理,下降请求指示灯fdnlight由“00000000000000”变成“00000 000001000”,接着变成了“00000000101 000”,说明4楼和6楼的下楼请求被识别.停止指示灯stoplight由“0000000000 0000”变成了“00000000000000”变成了“10000000000000”,接着变成了“100 00000000001”,表示14楼和1楼停止请求被识别.即电梯在1楼和14楼按下了停止键.

图5 主控制模块仿真结果

图6 主控制模块仿真结果2

4 硬件调试

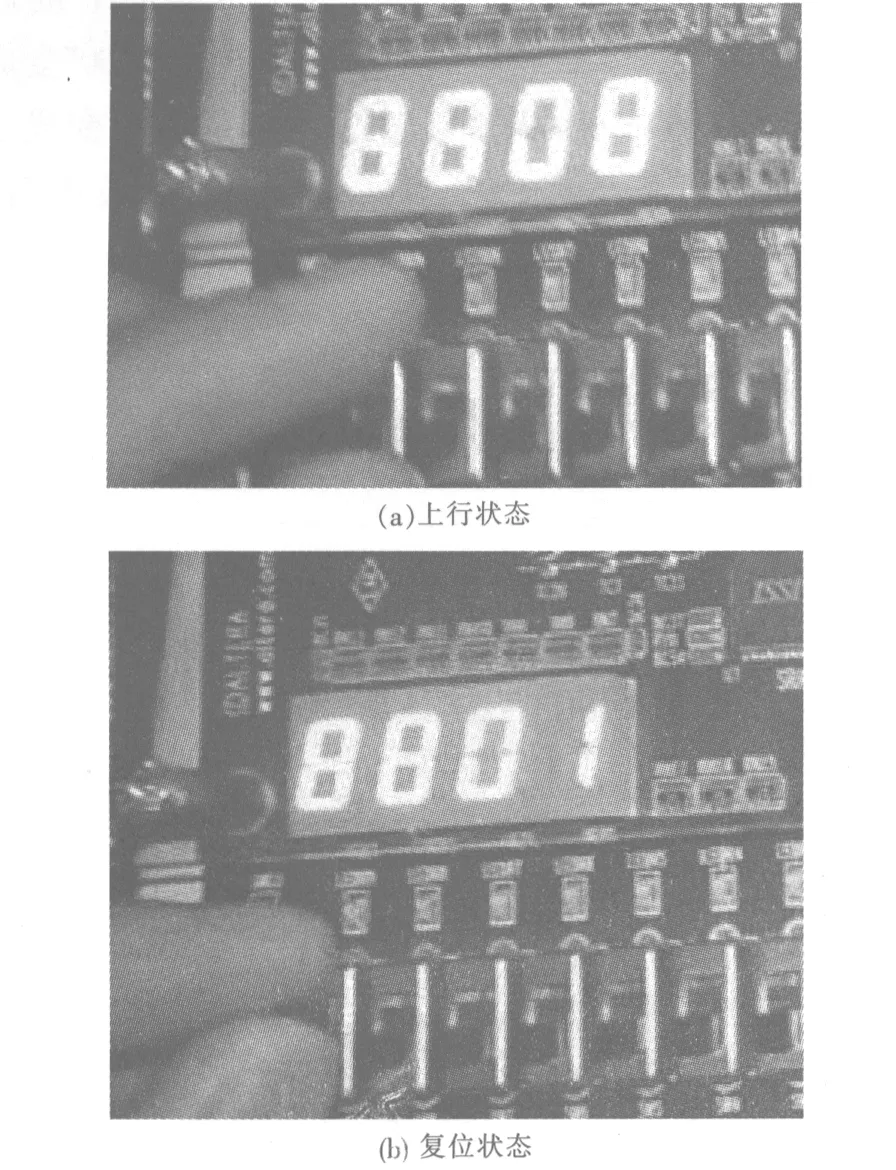

开发板借助集成开发软件,用原理图、硬件描述语言等方法,生成相应的目标文件,然后采用下载线将代码传送到目标芯片实现所设计的数字集成模块.本次设计使用的开发板型号是DE1 Altera,由于本次设计是14层的电梯控制系统,所有调试过程中只需要用到第三和第四个数码管.如图7(a)所示,在电梯上升过程:为了演示重置功能,数码管显示为08.将reset电梯复位键置于高电平,电梯实现重置功能,显示为01,表示电梯回到1楼,udsig电梯上升、下降状态灯不亮,表示电梯处于上升状态.如图7(b)所示.

图7 reset电梯复位键演示

电梯回到1楼,reset电梯复位键可以看到第一个LED灯变亮,表示开门状态,如图8所示.4 s后,电梯门状态显示灯不亮,表示关门状态,如图9所示.

图8 开门状态

图9 关门状态

5 小 结

本文设计了一个14层电梯控制系统.电梯能按照预定的规则上升、下降、载客等功能. 所设计系统的具有较好的扩展性,如在信号定义的时候使用了二进制的向量,而不是整数.采用随机逻辑控制方式很好的解决电梯请求信号优先级的问题,通过对程序做一定调整就可以改进成为任意层的电梯控制系统.如需要扩展成15层电梯控制系统.只要先对程序加上14楼的上升运行描述以及相关端口的设置.然后模拟原14楼的运行描述,对15楼的运行状态进行设计.再仿照原14楼的运行描述,对15楼的运行状态进行设计.最后对寄存器及各端口做出相关的调整,就可以扩展成15层电梯控制.本设计使用Verilog HDL语言进行程序设计,利用Quartus II进行仿真分析,最后采用FPGA开发板进行硬件调试,结果可靠、准确,调试结果说明此系统具有很强的实用性和适应性.

[1] 许 诺,陈 鹏.电梯历史回眸与发展展望[J].工程建设与设计,2014(1):21-22.

[2] 张汉杰.现代电梯控制技术[M].哈尔滨:哈尔滨工业大学出版社,2006.

[3] 彭 保,范婷婷,马建国. 基于Verilog HDL语言的FPGA设计[J].微计算机信信息,2004,20(10):80-82.

[4] 潘 松,黄继业.EDA技术实用教程[M].北京:科学出版社,2010.

[5] 王金明.数字系统设计与Verilog HDL[M].北京:电子工业出版社,2011.

[6] 包 明.EDA技术与可编程器件的应用[M].北京:北京航空航天大学出版社,2007.

[7] 陈兆芳.基于FPGA的电梯控制系统[J].福建电脑,2010(2):164-165.

[8] 许瑾娜.四层电梯系统的开发与设计[J].机电工程技术,2010(6):49-51.

14-Layer Elevator Controller System Based on Verilog HDL

ZHOU Xi-feng1,ZENG Rong-zhou2,LIU Mei-hua1,SUN Jing1

(1. College of Elect. & Information Engineering, Hunan Institute of Engineering, Xiangtan 411101, China; 2. The State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science & Technology of China, Chengdu 610054, China )

A 14 layer elevator controller based on Verilog HDL is realized in this paper. Both of the state machine process and traffic signal control process are adopted in the design. The state machine process is a major process, and the traffic signal control process is an assistant. The two aspects combine and complement each other to complete the whole control. The 14 layer elevator controller is designed and simulated by Quartus II. Finally the whole circuit is verified by FPGA and the test results are given. The results show that the designed system can control 14 layer elevator. The system has very strong practicability and high adaptability.

Verilog HDL; elevator controller; Quartus II; FPGA

2014-09-10

湖南省教育厅科研资助项目(11C0321); 湖南省自然科学基金资助项目(14JJ6040);湖南工程学院博士启动基金资助项目(Z).

周细凤(1979-),女,博士,讲师, 研究方向:CMOS数模混合成电路设计、有源滤波器设计、开关电容技术等.

TP273+.5

A

1671-119X(2015)02-0001-05