基于AD9680 的宽带高动态全数字雷达接收机设计

肖丹丹,宿绍莹,李 涛

(国防科学技术大学 电子科学与工程学院,湖南 长沙 410073)

现代雷达数字接收机的特点是环境化、模块化[1],日益复杂的电磁环境要求宽带数字接收机必须具备以下功能:大瞬时带宽、实时信号接收、大动态范围、高灵敏度和频率分辨能力[2]。基于软件无线电的宽带雷达数字接收机射频前端通过专用ADC(Analog-to-Digital Converter)芯片对射频信号直接采样,增加了射频前端的灵活性,减少了模拟环节[3]。某雷达升级改进要求系统的量化位数达到14 位,采样率为1 GSample·s-1,能从水平与垂直两个极化通道采集频段为1.2 ~1.4 GHz的射频信号。文献[4]实现了等效采样速率可达10 GSample·s-1的4 通道数字式脉冲超宽带雷达信号接收;文献[5]实现了基于拼接采样技术的宽带数字接收机,能对带宽1.2 GHz 的模拟信号以采样率3.2 GSample·s-1采样;但其的量化位数均只有10 位,能满足该雷达需求的数字接收机未见报道。

本文采用由AD 公司生产的新型ADC 器件AD9680,该芯片具有两个数据输入通道,量化位数14 bit,采样率1 GSample·s-1,支持高达2 GSample·s-1的射频信号直接采样,且内部集成4 个宽带抽取滤波器和12 位数控振荡器(Numerically Controlled Oscillator,NCO)、采用JESD204B 高速串行输出接口协议。不仅能满足某射频雷达对上述指标的需求,且还具有多频段接收、小型化、低功耗的特点。

1 系统简介

为满足某宽带射频雷达的需求,设计了一款基于AD9680 的仿真和验证平台,该平台由型号为AD9680-1000EBZ 的AD9680 采集板和型号为ADS7-V1EBZ的FPGA(Field Programmable Gate Array)载板组成。系统框图及硬件验证平台如图1 和图2 所示。

图1 基于AD9680 的宽带雷达信号直采验证平台

图2 系统验证平台

2 性能验证、分析与改善

首先是程序的编写,AD9680 的高速串行协议JESD204B 通过代码组同步、SYNCINB±、ILAS、用户数据和错误校正建立链路同步,输出串行线速率为每通道10 Gbit·s-1或5 Gbit·s-1。JESD204B 链路建立的关键参数有:转换器数M、物理通道数L、每帧的8 为字数F、每个多帧的帧数K 以及转换器分辨率N 和每个样本使用的位数N',本系统依据以上参数进行串行线速率及FPGA GTX(Gigabit Transceiver X)参考时钟配置。

2.1 全带宽模式

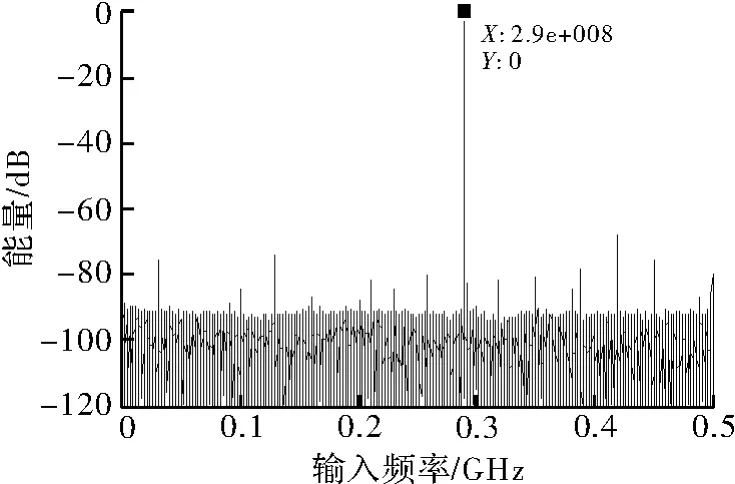

某雷达工作频段存在较强的干扰,对ADC 的瞬时动态要求较高,因此对ADC 采样率和分辨率的要求也较高。所以本文在配置满量程信号输入、采样点数、SPI 软复位、JESD204B 关键参数值等后得到全带宽模式下的FPGA 数字信号输出并对其进行ADC 性能计算[6],结果如图3 和图4 所示。

图3 1 290 MHz 正弦信号频谱图

图4 260 ~1 610 MHz 正弦信号ADC 性能图

图4 中采样信号的频率范围由系统的3 个带通滤波器决定,分别为260 ~460 MHz,1 170 ~1 290 MHz,1 570 ~1 610 MHz。射频数字化接收机动态设计时要求接收机模拟射频通道动态与接收机输入信号及ADC 的动态相匹配。这就要求接收机增益设计时最大输入信号不致ADC 饱和,同时最小信号输入并经过射频前端增益放大后能被ADC 充分量化。故本文在接收机大线性动态范围设计时主要考虑合理分配接收机各级增益和选择动态范围大的器件。另通过分析知调节电路输入端端接阻抗、模拟差分输入电压、输入缓冲电流可改善输出数据的动态性能。首先,合理的输入阻抗可满足驱动器、放大器的端接需求,阻抗小的情况下模拟信号输入幅度减小,ADC 性能变差,虽然谐波分量同时可能得到改善。其次,随着信号频率的增加,适当地减小模拟差分输入电压,增加输入缓冲电流,可达到抑制噪声分量,保护差分信号的线性,改善ADC 动态性能的效果。实测过程中发现在某射频雷达所需的带宽1 200 ~1 400 MHz 范围内,固定输入端接阻抗为400 Ω,模拟差分电压为1.46 Vp-p,并适当调节缓冲电流可得到最优的ADC 性能。优化后的结果如图4 所示,系统有效位数>8.4 位,SFDR 值>64.5 dB,可满足实际项目中ADC 器件选型一方面要达到特定指标需求,另一方面要具备较好的动态性能的要求。

2.2 下变频模式

射频数字化接收机的变频和滤波等都在数字域实现,为了适应不同频段信号接收和信道化通道数的要求,本系统采用内置4 个数字下变频器DDC0-DDC3的AD9680 对回波进行采集和处理。本文对AD9680在DDC 模式下的性能进行验证、分析和改善,具体过程如下:外部时钟输入后,通过设置DDC 抽取倍数、NCO 相位值、JESD204B 关键性能参数等得到输入信号的FPGA 数据输出,计算输出数据的ADC 性能值并对其进行分析和改善。部分频点抽取后频谱及性能如图5 和图6 所示。

图5 1 290 MHz 输入信号NCO 频率为270 MHz 的16 倍抽取频谱图

图6 2 ~16 倍抽取ADC 性能图

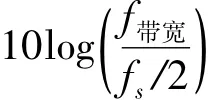

(1)系统在进行2n倍抽取时信号先后经过滤波器HB(n),HB(n-1)…HB1,n=4,3,2,1,由此,HB1 是滤波器的最后一级。本文以HB1 滤波器为例,分析随着抽取倍数的变大,实际SNR 性能值应提高的幅度。系统采用的HB1 滤波器有55 个抽头系数,其滤波器响应如图7 所示。

图7 HB1 滤波器响应图

(2)由前面的分析知DDC 2 倍抽取的SNR 性能值应稍大于全带宽模式,而图6 中当输入信号为1 601 MHz时,2 倍抽取的ADC 性能值明显偏低。为此,对系统输入信号的DDC 2 倍抽取进行Matlab 仿真,发现2 倍抽取性能变差的主要原因是镜像分量的混入:采集信号先后经过频率为fNCO的数控振荡器和半带抽取滤波器做数据输出。当信号与其的镜像分量与NCO 进行运算后同时出现在滤波器HB1 的通带内或镜像分量在HB1 的过度带内时,滤波器无法将其滤除干净,镜像分量混入2 倍抽取后信号的有效带宽内,导致输出数据的ADC 性能变差。为了实现某雷达频段的射频信号直接采样,必须采用带通采样或欠采样,因此需采用模拟抗混叠滤波器来抑制其他奈奎斯特频带的干扰或噪声,防止干扰混叠或噪声折叠对输出信噪比的影响。

2.3 系统同步性验证

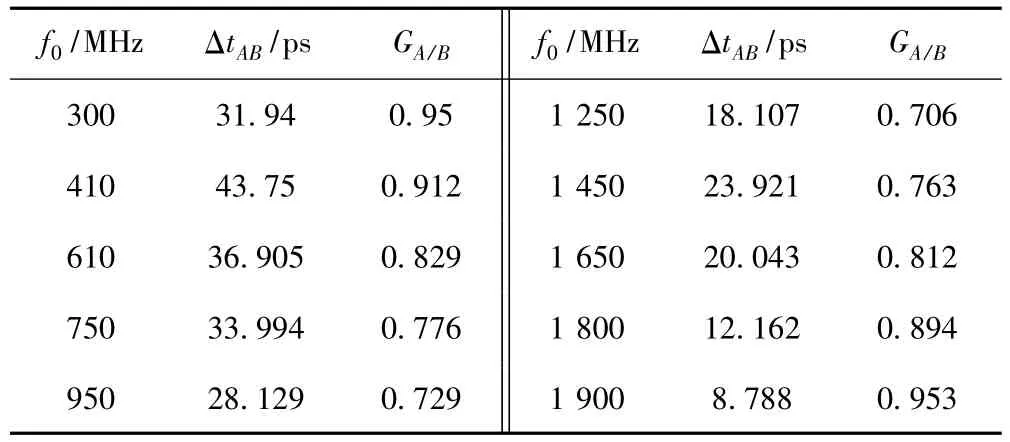

宽带雷达数字接收机多个通道之间的相位差大小决定后期成像质量的优劣。本系统用功分器将信号源输入在2 GHz 以下的信号分成两路输送给ADS7-V1EBZ 的通道A 和通道B,对输入信号进行全带宽和数字下变频模式数据采集,采用正弦信号在时域上的自相关和互相关计算两个通道输出数据间的增益误差和时间偏差[8]。分析知延时误差由以下几个因素导致:(1)两个输入信号在电路板上的布线差异。(2)AD9680芯片内部两个通道间的差异。(3)信号经过功分器和接线后产生时间误差。以上使两个通道输出数据相位和频率不完全同步的因素可通过下列方法进行改善:1)优化电路设计。2)调节NCO 相位值。3)算出功分器和接线的延迟误差并将其去除。本文去除了由功分器和接线造成的延迟误差并对系统下变频的NCO 相位值进行了调整,优化后的双通道延迟误差如表1所示。其中,f0为输入信号频率;ΔtAB和GA/B分别为两个通道之间的时间偏差和增益误差。为减小对后期成像的影响,需消除雷达系统的通道相位失真,即在实现双通道回波的高速采集和处理的同时需要达到一定的相位一致条件。本设计的通道A 和B 分别对应某雷达的水平和垂直两个极化通道,改善后的双通道延时误差在45 ps 以下,满足接收机的应用需求。

表1 改善后的双通道延时误差

3 结束语

本文通过分析基于AD9680 的宽带雷达数字接收机验证平台的基本特点及两种工作方式,结合雷达系统的实际要求,对系统FPGA 输出数据进行性能验证、分析、验证和改进。并对ADS7-V1EBZ 两个信号输入通道间的同步做了验证与分析,提出了双通道延时误差的改善方案。结果表明,新型ADC 器件AD9680在实际应用中具有高精度、高速度、动态范围大、灵活性强、双通道同步性能良好等特点,可满足某雷达对射频前端数字接收机的性能需求。下一步研究将继续完善双通道相位和幅度一致性校正、通过优化电路设计改善ADC 的性能、将AD9680 成功应用于某射频雷达中。

[1] 朱拥建,王宏.宽带数字接收机的设计与实现[J].中国电子科学研究院学报,2010,5(1):86-89.

[2] 龚仕仙,魏玺章,黎湘.宽带数字信道化接收机综述[J].电子学报,2013,41(5):949-959.

[3] 于渊,常青,张其善,等.导航接收机数字化射频前端的设计与验证[J].天津大学学报,2012,45(10):887-894.

[4] 谢跃雷,晋良念,欧阳缮,等.一种基于FPGA 的超宽带雷达数字接收机[J].现代雷达,2014,36(1):62-70.

[5] 向海生,马利祥,王冰.基于拼接采样技术的宽带数字接收机[J].雷达科学与技术,2014,12(4):450-453.

[6] 陈曾平.电路设计基础与专用系统构成[M].北京:科学出版社,2006.

[7] 宿绍莹.宽带实时频谱分析技术研究与实现[D].长沙:国防科学技术大学,2006.

[8] 张清洪,吕幼新,王洪,等.多片ADC 并行采集系统的误差时域测量与校正[J].电讯技术,2005,45(3):189-193.