基于可控采样率及断点保护的数据采编存储器设计

季 伟 ,苏淑靖 ,乔文生 ,张 斌

(1.中北大学 仪器科学与动态测试教育部重点实验室 电子测试技术国家重点实验室,太原 030051;2.中国航天科工集团第六研究所601所,呼和浩特 010076;3.中北大学 经济与管理学院,太原 030051)

随着信息技术的发展,采编存储器的采样速度、通道数、精度也随之提高[1-2],但是对其通用性也提出了要求。本设计采用FPGA(现场可编程门阵列)作为控制芯片,设计了16通道可以设置为不同采样率的同步采编存储器,该存储器还具有掉电监测功能和FLASH断点保护功能。本设计利用VHDL的并行特性,充分发挥了FPGA改动灵活方便和并行控制的特点[3],克服了多通道同步采集、不同采样率ADC数据混合编帧和断点保护等设计难点,提高了所设计的采编存储器的通用性。

本文设计的数据采编存储器可以同步采样16路0 V~5 V的模拟电压信号,可选择1 kS/s,5 kS/s,10 kS/s,25 kS/s和50 kS/s 5种采样率,具有0.1%FS的精度。

1 总体方案设计

采编存储器内的16路输入采集卡功能框图如图1所示。采集卡由阻抗匹配、减法电路、四阶抗混叠滤波器、放大电路、8路同步采样ADC、基准电压源、掉电检测电路、控制单元和背板总线组成。FPGA选用了XILINX公司的低成本Spartan-3E系列中的XC3S500E,可提供50万个系统门数、4656个Slice、73 kb分布式RAM和360 kb块RAM容量。其可灵活配置、低功耗的特性足以满足设计要求。

图1 采编存储器总体设计图Fig.1 Acquisition overall diagram

系统工作原理为16路模拟信号从输入接口接入,经过16路模拟信号调理,由FPGA控制ADC实现模数转换、编帧、存储,数据通过背板总线上传。为了满足通道数和采样精度的设计要求,实现同步采集,提高电路集成度,ADC采用ADI公司的AD7606,它可以8通道同步模拟采样,处理±5 V真双极性输入信号,有高达1 MΩ的固定输入阻抗,采样率最大达200 kS/s。上位机可以实时分析采样数据。采编存储器受上位机命令控制。

2 掉电监测电路设计

采编存储器工作时,需要写入或读取FLASH。如果此时基准电压源故障导致意外掉电,可以引起系统程序跑飞而无法继续工作,甚至造成大量数据的丢失,带来不可弥补的损失,影响数据的完整性、正确性。而且下次上电时,难以恢复上次的存取状态,导致数据因为掉电而损坏。为了避免出现这种情况,设计了掉电监测电路,采用MAX709监测电源电压,同时产生系统的复位信号。

MAX709能够在加电、掉电以及降压情况下,使其RESET引脚变为低电平,提供复位信号。MAX709不受短持续期的Vcc瞬变的影响,能够提供可靠的复位信号[4]。因此MAX709的RESET低电平信号可以用作掉电的监测信号。由于电容性器件的存在,当系统掉电时,工作电压下降到系统无法工作的危险电压之前有一定的时间延迟,这段时间可以执行数据保护操作。经过示波器测试,本采编存储器从监测到掉电信号到工作电压下降到危险电压的时间约为 4 ms。MAX709的RESET连接到FPGA,作为复位和掉电信号。

3 逻辑设计

3.1 总体逻辑设计

总体逻辑包括时钟产生模块、命令模块、全局复位模块、全局时钟模块、A/D控制模块、FIFO、编帧模块。由全局时钟模块产生全局同步时钟信号,同步所有模块的操作。A/D控制模块与编帧模块之间采用乒乓操作设计。2个ADC的数据交替地写入2个FIFO里,编帧模块对数据进行混合编帧,之后数据同时存储到上位机和FLASH中。模块框图如图2所示,总逻辑流程如图3所示。

图2 程序模块框图Fig.2 Program module diagram

图3 总逻辑流程图Fig.3 Flow chart of general logic

3.2 ADC采样率可变设计

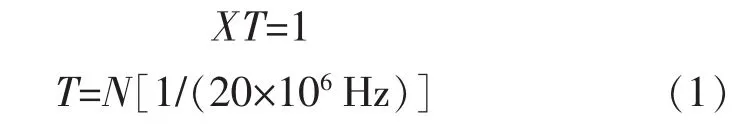

为了满足通道数要求,采用2片AD7606在FPGA的控制下进行同步采集。AD7606设置为并行字节模式,8通道同步采样,每个通道的数据以字节为单位,在并口DB[7:0]先输出高字节后再输出低字节。如果对2片ADC顺序控制,非但体现不出FPGA的并行控制的优势,而且无法实现16通道同步采集。设计中对2个ADC采用了双进程分别进行控制。在VHDL中同一个结构体内的2个进程是并行执行的[5],这就使2个ADC可以同时采样,而且2个ADC可以以不同的采样率同时采样。AD7606的采样周期受输入CONVST管脚的逻辑电平控制。为了使采样率变化,必须控制CONVST管脚的电平周期。AD7606的工作时钟为20 MHz,为了实现5种可选的采样率,在AD控制程序中需要对状态计数。在采样率为X时,每次采样对应的状态数N可计算为

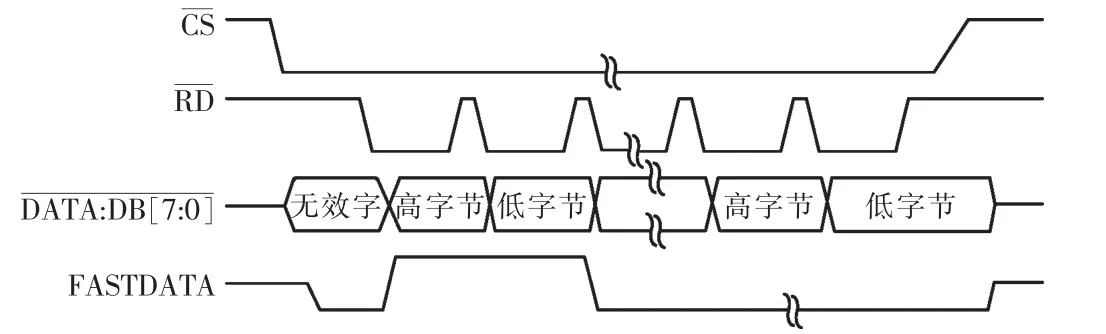

式中,T为CONVST电平变化的周期。在ADC采样转换后读取数据会占用采样时间使采样率降低,所以设计为在采样转换期间读取上一次采样数据,保证采样率按设计要求实现。并行字节模式在转换期间读取数据的时序如图4所示。

图4 并行字节模式读取数据时序图Fig.4 Parallel byte mode data read time sequence

3.3 数据混合编帧设计

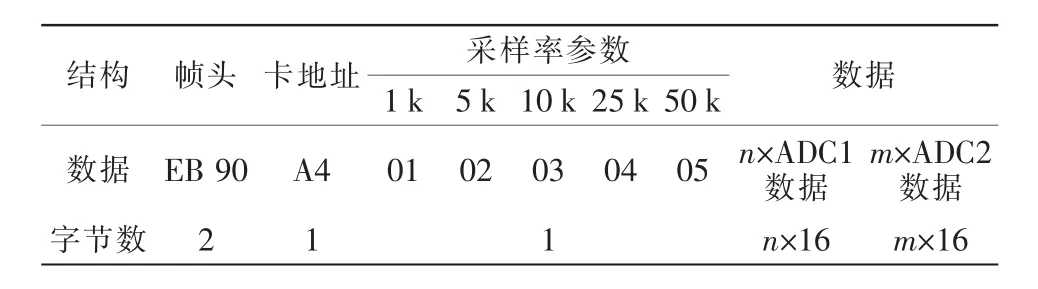

采样率的可选设计给数据编帧带来了困难,因为帧结构是随着采样率的不同而变化的。本设计中不同的ADC可以不同采样率同时工作,编帧模块必须根据每个ADC的采样率设置其帧结构。设计如图2所示,每个ADC分配了独立的缓存FIFO,使不同帧结构的数据不会混淆以至无法区分。而帧结构设计为如表1所示的16通道混合可变结构,每帧数据为16个通道1 ms采到的数据。其中n为ADC1即前八通道的每毫秒采样次数,m为ADC2即后八通道的每毫秒采样次数。n和m的值可以由采样率得出。编帧模块根据采样率参数设置n和m值,分别从2个FIFO中读出16 n个字节和16 m个字节,再加上帧头、卡地址和采样率参数组成一帧。编好帧的数据就可以传给上位机或者存储到FLASH中。

表1 帧结构表Tab.1 Frame structure

3.4 数据缓存设计

A/D控制模块控制着2片ADC,2片ADC可以设置为不同采样率进行采样。而这2片ADC的采样数据要按设计的帧结构存储在一起。编帧模块与FLASH模块的工作频率与数据传输速度不同,而且FLASH页编程的200 μs期间不能写入数据,上位机读数周期则为1 ms。这2段时间内数据不能存储和上传,需要数据缓存。按可设置的最快采样率50 kS/s计算缓存数据,参照表1,那么每帧的数据量D可用下式计算:

D=2+1+1+50×16+50×16=1604 B

因此,对FLASH而言,需要缓存的数据量为

200 μs×1604 B/ms=320.8 B

而上位机需要缓存的数据量为

1 ms×1604 B/ms=1604 B

选用容量为2048 B的FIFO作为缓存,足以满足缓存需要。

3.5 FLASH无效块检测及断点保护

FLASH存储芯片采用了三星公司的NAND芯片K9WBG08U1M。其块擦除时间为1.5ms,页编程时间为 200 μs,容量为 4 GB。

FLASH中不可避免地存在无效块,无效块不能被用来存储数据,因此在写入、读取操作前都要识别无效块。常规做法是对无效块建立地址表,通过对地址表的查询识别无效块。这种方法需要占用FPGA中宝贵的存储资源,而且每次操作之初都必需更新无效块地址表,否则如果出现新的无效块,存储数据就会出错。为此,本设计采用了在每次写入、读取、擦除之前对每一块进行无效块检测的方法。无效块检测采用读取每块前2页的第2048字节的内容来实现,如果读到非FFh的数据则认为该块为无效块。因为擦除操作失败会产生无效块,在每次擦除操作后必须对操作成功与否进行检测,即擦除操作完成后,查看I/O 0位的值,如果非0则擦除失败。在擦除失败的块前2页的第2048字节处写入00h,将其标记为无效块。

FPGA的FLASH模块检测到MAX709的RESET信号时,会进入断点保护程序。断点保护是在存储数据的过程中,为避免因系统电源电压欠压甚至切断而造成数据存储紊乱而采取保护的一种措施[6]。断点保护程序需要保存FLASH断点地址,即当前的写入地址和读取地址。本设计将断点地址保存在FLASH的第一块中,所以保存新地址之前需要擦除旧地址。这些擦除、写入操作需要在系统开始掉电的4 ms之内完成,而FLASH的页编程典型时间为200 μs,块擦除典型时间为1.5 ms,断点程序共需要约1.7 ms来完成断点保护,时间在4 ms之内,断点保护程序可以实现。

4 测试结果

如图5所示为采集卡采样到的数据的帧结构,每帧共100 B,其中,EB 90为帧头,A4为卡地址,21表示前八通道采样率为5 kS/s,后八通道采样率为1 kS/s,由表1计算可知与设计相符。

图5 帧结构图Fig.5 Frame structure

用GPS-4303C型稳压电源为采编存储器输入4.8008 V(使用6位半精度的高精度万用表测得)的直流电压,计算通道10的精度为(4.8008-4.7995)/5=0.026%,小于满量程的0.1%。

图6为给采编存储器输入0~5 V正弦波后,上位机通道1和通道9的输出波形。

图6 上位机输出波形Fig.6 Software output wave

5 结语

本设计使用FPGA做采编存储器的控制芯片,实现了16路数据同步采样、不同采样率ADC的混合编帧和FLASH存储器的断点保护。设计的采编存储器能够在采样率可选的情况下同步采样多路数据,达到了较高精度,提高了设计通用性,满足设计要求。

[1]李念强,魏长智,潘建军,等.数据采集技术与系统设计[M].北京:机械工业出版社,2009:1.

[2]胡晓军.数据采集与分析技术[M].2版.西安:西安电子科技大学出版社,2010:1-5.

[3]郭亮,卫一然,甄国涌.基于FPGA的高速数据采集系统设计实现[J].计算机测量与控制,2013,21(2):537-539.

[4]吴东,张冈,张志鹏,等.一种实用的掉电检测和保护电路[J].电子技术应用,1999,25(6):69-70.

[5]侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2000:10-60.

[6]冉自博.基于U盘高速串行数据记录器设计[D].山西:中北大学,2014.