一种改进的早迟积分型位定时同步方法

杜亚琦,周建英

(1.通信信息控制和安全技术重点实验室 浙江 嘉兴314033;2.中国电子科技集团公司 第三十六研究所,浙江 嘉兴314033)

位定时同步是数字系统中重要的同步技术之一,常用的有非线性变换-滤波法、早迟积分型锁相环同步法和数字插值法[1-2]等。非线性变换-滤波法实现的关键在于需要设计窄带滤波器,在数字系统实现时,滤波器带宽越窄需要的滤波器阶数越高,所需的硬件资源越多。数字插值法是根据误差信息贵采样值进行插值运算获得最佳符号采样值,也称为异步时钟恢复,适用于多通道解调,但实现复杂。

早迟积分型锁相环同步法应用匹配滤波原理,先对输入的基带信号进行最佳检测,有更好的抗干扰性能。同步过程与载波同步相似,通过比较本地时钟与接收数据码元,使本地时钟与接收数据码元同步,是应用最广泛的位定时同步方法之一。

关于早迟积分型位定时方法研究有很多,文献[3]提出在鉴相器早迟积分绝对值比较式加入动态门限控制,在开始阶段门限设置较低以尽快收敛,环路稳定后适当提高门限以减少误判,但没有给出门限设置方法。文献[4]提出一种新的积分结构和新的环路滤波,提高了位定时同步环路收敛速度,但设计复杂度也相对提高了。本文提出了一种改进的早迟积分型位定时方法,在相同的环路滤波参数下,新方法环路收敛速度最优可以提高2倍,但几乎不增加位定时同步环路的设计复杂度。

1 早迟积分型锁相环同步法

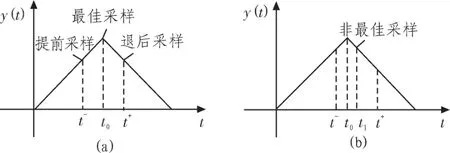

在理想状态下,基带信号经匹配滤波(相关积分)后输出信号在最佳采样时刻最大,而且以最佳采样时刻位置左右对称,如图 1(a)所示。其中,t0为最佳采样时刻,t-=t0-σ 超前采样时刻,t+=t0+σ为迟后采样时刻。显然,这时超前采样时刻的采样值和迟后采样时刻的采样值相等,最佳采样时刻就是超前采样时刻和迟后采样时刻的中点,即t0=(t-+t+)/2。

若假设初始采样不是最佳采样时刻t0,而是在t1时刻采样,如图 2(b)所示,这时超前采样时刻 t-=t1-σ,迟后采样时刻t+=t1+σ,显然,这时超前采样时刻的采样值和迟后采样时刻的采样值不相等。若t1>t0,有>,说明最佳采样时刻t0在当前采样时刻t1之后,则下一比特位的采样时刻要提前;若t1<t0,有<,说明最佳采样时刻t0在当前采样时刻t1之前,则下一比特位的采样时刻要推后。因此通过比较当前采样时刻左右两端的超前采样值和迟后采样值,不断调整下一比特位的采样时刻提前或推后,直至超前采样值和迟后采样值相等,则当前比特位的采样时刻即为最佳采样时刻。

图1 早迟积分采样示意图Fig.1 The diagram of the early-late integral sampling

早迟积分型锁相环同步法的结构框图如图2所示,主要包括:积分单元、采样单元、时钟单元、鉴相器和环路滤波器。基带信号同时送入两路积分单元,在采样单元内根据时钟单元提供的超前采样时钟和迟后采样时钟对积分单元输出采样,取采样后积分值的绝对值,经鉴相器、环路滤波器完成对采样时钟调整。

图2 早迟积分型同步法结构框图Fig.2 The structure diagram of the early-late integral synchronization method

2 改进的早迟积分型锁相环同步法

环路滤波器的设计是早迟积分型锁相环同步法实现的关键。由于干扰或波形本身的不对称性,如图1(b)所示,采样时刻t1将在最佳采样时刻t0左右两端摆动,前一个比特在超前区,下一个比特可能又在迟后区,锁相环路就需要不断调整,从而引入不希望的相位抖动。加入环路滤波器就是为了解决这个问题,环路滤波器的设计方法有很多,本文采用随机徘徊序列滤波器法[5-6],它由一个计数为2N的可逆计数器构成。

当鉴相器送出超前或迟后脉冲时,滤波器并不马上将它送去进行相位调整,而是要先对输入的超前或迟后脉冲计数。在计数开始时,可逆计数器的初值为N,若鉴相器输出为超前脉冲,则计数器的值减1,若鉴相器输出为迟后脉冲,则计数器的值加1。经过若干次调整后,若计数器的值等于0,则环路滤波器送出一个超前脉冲调整时钟单元,同时计数器的值重新置为N;若计数器的值等于2N,则环路滤波器送出一个迟后脉冲调整时钟单元,同时计数器的值重新置为N。只有在鉴相器输出为持续的超前或迟后脉冲时,计数器才会持续的加或减1,。在环路锁定时,受到随机噪声的影响,超前或迟后脉冲的产生概率趋于相等,计数器值将在N值上下摆动,这样就可以减少噪声引入的环路误调整。

在位定时同步的开始阶段,当前采样时刻位于超前区或迟后区,假设经过M次调整后,当前采样时刻调整为最佳采样时刻,显然整个过程至少要经过M*N次计数,也即只要经过M*N个比特位后,位同步环路采样进入锁定状态,计数器的值N越大,调整的时间越久。但如果减小计数器值N,环路滤波器的滤波作用就会减弱,环路收噪声影响加大,而变得不稳定。

基于上述问题,文中提出了一种改进方法,可以加速环路收敛,在计数器值N相等的情况下,该方法理论上比传统的环路滤波方法收敛速度提高一倍。

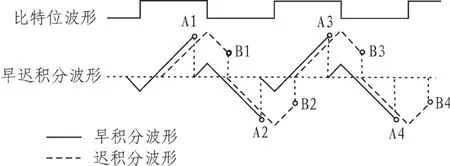

图3为早迟积分型锁相环积分检相示意图。假设比特位为“0101”交替波形,早积分时刻先于迟积分时刻1/2个比特位周期,A1、A2、A3、A4 为早积分时刻对应的积分值,B1、B2、B3、B4为迟积分时刻对应的积分值。

图3 早迟积分型锁相环积分检相示意图Fig.3 The phase detection diagram of the early-late integral phase locked loop

传统的环路滤波方法是在第一个比特周期内比较A1和B1,然后根据检相器输出调整一次计数器值N,在以后的每个比特周期内分别比较A2和B2、A3和B3、A4和B4等。从图3的早迟积分波形中可以看出,B1和A2也可以组成一对超前迟后检相组,同样B2和A3、B3和A4等也都是超前迟后检相组。因此从第二个比特开始,如果在一个环路检相周期内,对环路完成两次积分值检相,即依次比较B1和A2、A2和B2,每次检相送出一个超前或迟后脉冲,则在一个比特周期内鉴相器将送出2次超前或迟后脉冲,环路滤波器的计数值调整将调整2次,这样环路的收敛速度也将提高一倍。

3 改进的早迟积分型锁相环同步法性能分析

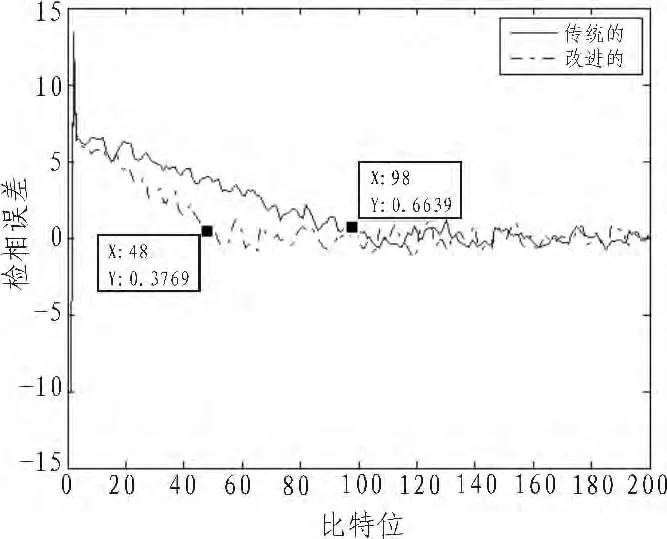

图4和图5中比较了在相同的基带数据采样频率和相同的比特位速率条件下,不同的环路滤波器计数值对环路收敛速度影响。

图4为计数器值N=3时,传统的早迟积分型锁相环位定时方法与改进的早迟积分型锁相环位定时方法收敛速度比较,从环路开始工作到环路锁定,改进的早迟积分型锁相环位定时方法经过了大约20个比特位周期,传统的早迟积分型锁相环位定时方法经过了大约30个周期。传统的早迟积分型锁相环位定时方法收敛所用时间是改进的早迟积分型锁相环位定时方法用收敛所用时间的约1.5倍。

图4 环路滤波器的计数器值N=3Fig.4 the count value of loop filter N=3

图5 环路滤波器的计数器值N=10Fig.5 the count value of loop filter N=10

图5 为计数器值N=10时,传统的早迟积分型锁相环位定时方法与改进的早迟积分型锁相环位定时方法收敛速度比较,从环路开始工作到环路锁定,改进的早迟积分型锁相环位定时方法经过了大约50个比特位周期,传统的早迟积分型锁相环位定时方法经过了大约100个周期。传统的早迟积分型锁相环位定时方法收敛所用时间是改进的早迟积分型锁相环位定时方法用收敛所用时间的约2倍。

比较图4和图5可以看出,相同位定时方法,环路滤波器的计数值N约小,环路收敛约快;相对于传统的早迟积分型锁相环位定时方法,环路滤波器的计数值N越大时,改进的早迟积分型锁相环位定时方法收敛速度优势约明显。

4 结论

本文提出了一种改进的早迟积分型锁相环位定时方法,其在传统的早迟积分型锁相环位定时方法的基础上,通过提高鉴相器的检相频率,提高环路的收敛速度。且环路滤波器的计数器值N较大时,改进的早迟积分型锁相环位定时方法的收敛速度约相对于传统的早迟积分型锁相环位定时方法的2倍,但设计复杂度几乎没有变化。

[1]季仲梅,杨洪生,王大鸣,等.通信中的同步技术及应用[M].北京:清华大学出版社,2008.

[2]杨小牛,楼才义,徐建良.软件无线电技术与应用[M].北京:北京理工大学出版社,2010.

[3]陈良灏,韩啸.数字锁相环位同步器及其FPGA设计[J].微机处理,2007(5):1-3.CHEN Liang-hao.HAN Xiao.A bit synchronizer with DPLL and its FPGA implement[J].Microprocessors,2007(5):1-3.

[4]王君,安建平.早迟门同步器跟踪速度的改进方法[J].电路与系统学报,2005(6):111-114.WANG Jun,AA Jian-ping.An improving tracking speed method in the early-late gate synchronizer[J].Journal of Circuits and Systems,2005(6):111-114.

[5]樊昌信,张甫翊,徐炳祥,吴成柯.通信原理[M].北京:国防工业出版社,2001.

[6]杜勇.数字通信同步技术的MATLAB与FPGA实现[M].北京:电子工业出版社,2013.