一种基于CMOS工艺2.4 GHz功率放大器的设计

吕 杰,刘林海,李 哲,曹 纯

(中国电子科技集团公司第五十四研究所,河北石家庄050081)

0 引言

随着无线技术的快速发展,单芯片CMOS收发机已经商用化了。在硅CMOS、GaAs、异质结和SiGe等众多工艺中,虽然CMOS的高频性能和噪声性能不是最好,但是由于它的工艺最为成熟、成本最低和功耗最小,并且随着集成电路工艺水平的提供,其特征尺寸不断减小,深亚微米CMOS工艺的特征频率已经达到 50 GHz以上[1]。

由于摩尔定律,随着工艺的不断进步,线宽进一步减小,晶体管能够工作的截止频率不断提高,因此CMOS射频功率放大器越来越多地采用CMOS工艺实现[2]。深亚微米工艺中低的击穿电压是设计中需要考虑的一个重要因素。低的击穿电压限制了栅漏电压,从而使得晶体管的供电电压受限,因此限制了功率放大器的输出功率[3]。提高功率放大器的线性度以及功率附加效率成为功率放大器的关键技术,也是功率放大器研究重点和热点。

当今世界商用的射频设计技术,尤其是CMOS功率放大器核心设计技术一直掌控在国外为数不多的大公司手中,这严重限制了我国信息产业的发展。本文基于RF CMOS工艺进行功率放大器的设计,采用双反馈结构实现高功率输出和高的功率附加效率,可以将射频及基带芯片单片集成在一颗芯片中,有助于实现射频基带芯片的一体化设计,降低设计及封装成本。因此基于CMOS工艺的射频功率放大器研究对于打破国外技术垄断、降低芯片成本具有重要的应用价值和现实意义[4]。

1 结构分析

功率放大器按照工作状态可分为线性和非线性2类,其中线性功率放大器主要有:A、B、AB和C四种类型,它们的主要差别是栅极偏置条件不同,这类放大器有相对不错的线性度,效率也可以达到较好的水平[5]。非线性功率放大器主要有D、E和F三类,这类放大器的输出功率比较高,但是线性度相对较差。B类放大器的效率明显高于A类放大器,实际中它的典型效率一般为60%。对于 AB类功率放大器,晶体管在大半个周期内处于导通状态,其导通角在180°~360°。当驱动电压幅度减小时,晶体管导通角增加,使得输出电流的直流成分、基频成分都会减小,在负载阻抗保持不变时,输出电压的幅度也会成比例减小,导致输出功率下降[6]。概括地说,AB类功率放大器的线性度要比A类差,但是比B类要好,而效率比A类好,但比B类差。由于它兼顾了线性度和效率,所以在实践中得到广泛应用[7]。

本文是基于SMIC 0.18 μm RF CMOS工艺设计一款高线性度和高功率的功率放大器,随着CMOS工艺的发展,其供电电压逐渐降低,这就对高功率功率放大器的设计提出了一定的要求,在SMIC 0.18 μm RF CMOS工艺中,最高供电电压为3.3 V,在负载阻抗为50 Ω时其最大输出功率仅为

此时输出功率约为0.108 9 W(约20 dBm),距离目标设计的23 dBm(约为0.199 mW)的最大输出功率尚有一定的差距,此时电源电压已经是该工艺提供的最大工作电压,因此必须进行阻抗变换,变换后的电阻最大值为:

在实际电路中,由于存在一些不可避免的功耗损失,如晶体管上的电压降以及互连线上的损耗。因此,在实际设计中可以根据仿真情况看该输出阻抗是否满足设计要求。当输出功率小于所希望的值时,那么变换后的电阻还需要更小[8]。若输出功率超过了应满足的值,那么变换后的电阻可以加大以提高效率。对于CMOS PA的设计,效率和线性度是2个非常关键的指标。根据以上分析,本文功率放大器采用2级放大,AB类工作:驱动级采用自偏置的共源共栅结构,不仅可以提高增益,增加反向隔离,而且能有效缓解栅氧击穿和热载流子效应带来的可靠性问题;功率级利用厚栅器件,从而可以在更高的电压下工作以提高输出功率[9]。

2 电路设计

根据PA的指标要求,综合考虑到效率和线性度,本文提出一种双负反馈结构的AB类的PA,如图1所示。

图1 双负反馈CMOS功率放大器

射频放大器包括2级:驱动级和功率输出级,级联后增益可以大于23 dB。AB类的结构,使得功率附加效率可以在35%以上。工作在2.4 GHz频段上,分别在PA的输入、2级之间、PA的输出设计匹配网络,容易实现3 dB带宽不低于200 MHz,其中输出匹配网络将50 Ω的天线阻抗变换到一个更小的阻抗,便于输出大的功率;驱动级和功率输出级之间的阻抗变换网络将功率输出级的输入阻抗变换到更大的阻抗,使驱动级得到一个高的增益;输入匹配网络将驱动级的输入阻抗匹配到50 Ω,减小输入反射系数。

其中,M4采用厚栅MOS管设计,用于输出大功率;M1~M3采用薄栅MOS管设计。一条反馈路径在第1级的输入和第2级的输入之间,由一个可变电容CA和电容C1构成,这个反馈路径抑制二次谐波,进而提高PA的线性度;另一条反馈路径由电容C2和C3构成,将共栅极放大管M2和M4的栅极相连。这样一来,耦合到M4栅极的信号经180°相移后反馈到M2的栅极,这个信号和M2管源极和漏极的信号变换在相位上一致,使得M2和M4这2个共栅管的栅源、栅漏电压的变化减小,进而减小非线性。因此,可以实现输出1 dB压缩点不小于23 dBm。M1~M4均采用多个管子并联构成,通过开关进行切换。通过SPI总线来控制M1~M4,每个开关由一个主开关管和一个辅助管构成,确保能有效地打开和关断:主开关管控制栅极偏压和栅极直接的通断,辅助管在栅极关断时将栅极接到地,以确保完全关断。这样一来,就能实现在SPI接口的3 bit控制下,功率调整范围18~23 dBm。

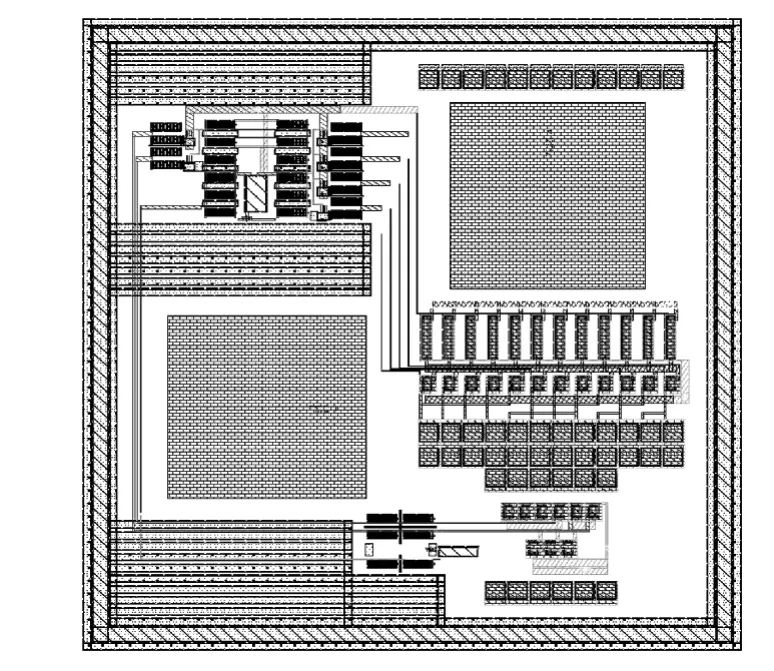

功率放大器版图如图 2所示,采用 SMIC 0.18 μm RF CMOS工艺,占用芯片面积0.9 mm×0.9 mm,其中左半部分为偏置电路,右半部分为功率放大器核心电路,芯片外围由P衬底和N衬底构成的保护环环绕,用来减小功率放大器与其他模块间的干扰。

图2 功率放大器版图

3 仿真结果

功率放大器功率增益随输出功率变化曲线如图3所示,由图3可以看出,在不同工艺角下,功率放大器的功率增益均大于24 dB,功率增益压缩点均大于23 dBm。

图3 功率放大器功率增益随输出功率变化曲线

功率放大器另一个重要指标是对功率附加效率(PAE)的要求,功率放大器PAE后仿真结果如图4所示。由图4可以看出,在不同工艺角下,功率放大器的峰值附加效率均大于40%。在工艺角为ff,环境温度为-45°时,功率放大器的峰值附加效率甚至达45%。

在输入功率设定为0 dBm的条件下,在输入信号频率为1.8~3.2 G,不同输入频率下功率放大器的功率增益曲线如图5所示,在后仿真环境下,由于寄生参数的影响,放大器的频带明显变窄,其带宽由前仿真的500 MHz减小到400 MHz,这个主要是由于高频下寄生电容等参数等影响,使得其带宽减小,该指标依然满足系统对带宽的要求。

图4 附加效率(PAE)随输入功率变化曲线

图5 功率放大器功率增益随频率变化曲线

功率放大器输入端口设计为50 Ω输入阻抗,对功率放大器作S参数扫描,得到其输入反射系数S11,用来衡量其输入阻抗匹配特性,其结果如图6所示。

图6 输入反射系数随频率变化曲线

其中实线为前仿真结果,虚线为后仿真结果,与增益特性曲线相类似,后仿真结果与前仿真结果相比带宽明显变窄,但是在要求的2.0~3.0 GHz,S11<-15 dB,能够满足设计要求。

4 结束语

基于2.4 GHz无线接入方式的应用,采用SMIC 0.18 μm RF CMOS工艺,实现了2级功率放大器从结构选择、电路、版图及后仿真等方面的研究和设计。结果表明,功率放大器在功率输出、线性度及附加效率方面都取得了较好的性能,后仿真结果表明,电路在工作频率范围内,功率增益为24 dB,输出1 dB压缩点为23 dBm,峰值功率附加效率为40%。对于基于CMOS工艺的功率放大器设计具有一定的参考价值。

[1] LARSON L E.Integrated Circuit Technology Options for RFIC’s-present Status and Future Directions[J].IEEE J Sol Sta Circ,1998,33(3):387-399.

[2] 张国燕,黄 入,张 兴,等.CMOS射频集成电路的研究进展[J].微电子学,2004,34(4):377-382.

[3] 龙 强,吴玉广.射频CMOS功率放大器的研究与应用[D].西安:西安电子科技大学硕士毕业论文,2007:9-13.

[4] 徐 谦,刘太君,叶 焱,等.可重构多波段射频功率放大器设计[J].无线电通信技术,2014,40(3):61-64.

[5] KANG J,YU D.Highly Linear 0.18um CMOS Power Amplifier with Deep n-Well Structure[J].IEEE JSSC,2006,41(5):1 073-1 079

[6] CHRISTIAN F.A ComprehensiveAnalysisofIMD Behavior in RF CMOS Power Amplifiers[J].IEEE JSSC,2004,39(1):24-34.

[7] 张书敬.SiC宽带功率放大器模块设计分析[J].无线电工程,2011,41(5):39-42.

[8] 殷素杰,杜 浩.射频功率放大器的宽带匹配设计[J].无线电工程,2013,43(2):48-51.

[9] 刘传洋,蓝永海.L频段高效功率放大器设计[J].无线电工程,2014,44(4):47-49,61.