北斗接收机载波跟踪环设计与实现

刘征岳,赵秋明

(桂林电子科技大学 信息与通信学院,广西 桂林541004)

0 引 言

北斗系统的空间星座计划由5 颗地球静止轨道卫星、27颗中圆地球轨道卫星与3颗倾斜地球同步轨道卫星组成,截止目前最多有14 颗星参与服务。其中B1 频点(1561.098MHz)信号由I(同相)、Q(正交)两个支路的 “测距码+导航电文”正交调制在载波上构成[1]。导航接收机进行定位解算的过程,就是先剥离卫星信号中的载波分量和伪随机码[2],最后输出导航电文用于后续定位解算。载波跟踪环路的跟踪性能是决定接收机定位效果优劣的关键指标之一,其高动态性能与抑制噪声的能力是相互矛盾的。这两项性能在一般的导航接收机中往往不能兼得,这就需要对载波跟踪环路的结构和跟踪策略做相应的改进。采用FPGA 和DSP相结合的结构对于实现信号处理和导航定位有很大的灵活性,可以根据不同需求设置不同算法,开发周期短,具有很强的通用性和扩展性。

1 载波环路总体设计

B1频点的信号从天线接收,经过放大,以及I/Q 下变频的混频后输出2.098MHz的中频信号。经过AD 进行采样量化后输送给FPGA 进行后续处理。在FPGA 收到中频数据后,为了能让接收机跟踪环路成功地跟踪上卫星信号,必须先通过对各颗卫星的搜捕来使复现载波和伪随机码与相应卫星信号中的载波频率和码相位达到一定的粗略吻合,并让相应通道进入牵引状态,在误差抖动进一步缩小后,最后对其进行严密跟踪。

载波跟踪环主要分为4个部分:积分器清除器、载波环鉴别器、环路滤波器和载波NCO(数控振荡器)。这4个部分的设计基本决定了载波环的性能[3]。首先输入信号与FPGA 本地产生的同相及正交复现载波分别进行相关运算,与本地复现伪随机码进行解扩,再送往DSP 进行误差的鉴定与环路控制,同时,载波环路输出载波生成器的步进值反馈回载波发生器,从而进一步拉近本地与复现载波的误差,最终实现载波的跟踪。载波跟踪方框架如图1所示。

图1 接收机载波跟踪环方框架

FPGA 采用Altera的EP2C70F672来实现基带数字信号处理,DSP采用T1的TMS320C6713实现环路控制。根据导航算法的特点和FPGA 与DSP的运算特点,在载波跟踪环路方案中对FPGA 与DSP做如下划分:

FPGA 端实现功能:

(1)本地载波成生器(载波NCO)

(2)乘法器

(3)积分和清除器

(4)产生对DSP的中断信号,向DSP发送相关结果

DSP端实现的功能

(1)对FPGA 端的载波NCO 控制

(2)载波环鉴别器

(3)环路滤波器

(4)载波环对码环的辅助

关于乘法器,载波NCO的设计请参见文献[4],这里不再赘述,后文将把重点放在DSP端对载波跟踪环路的控制。

1.1 接口设计与中断控制

DPS端通过集成的外部存储器接口(EMIF)模块来实现与FPGA 端的高速数据交换。C6000 系列的DSP 的EMIF支持与各种外部器件的无缝接口,其输入工作时钟ECLKIN 和输出时钟ECLKOUT 均可通过相应的配置寄存器进行设置。EMIF数据线、地址线、片选信号及其它接口控制信号与FPGA 的IO 口连接。其余信号均通过FPGA的通用I/O 管脚接入。

通过FPGA 配置两个计数器产生20ms的TIC 中断和0.505ms累加中断。前者的TIC 中断包括提取载波周数和NCO 的步长值,伪随机码的周计数和码NCO 的值,另外为了使FPGA 与DSP同步,还需要从FPGA 中提取计数校准值对DSP进行校正。后者的累加中断包含了牵入、比特同步以及跟踪3个过程。

2 载波环跟踪环分析与设计

2.1 积分清零器

在图1所示的载波环中,积分清除器用来消除信号中的高频成分与噪声,发挥着低通滤波器的作用。信号经过积分清除器后,去除了高频分量和噪声,可得

其中,相干积分时间Tcoh是接收机设计中相当关键的参数。提高相干积分可以提高信噪比,且其增益与相干时间Tcoh内的点数Ncoh成正比,但实际设计时不能任意加长相干时间Tcoh,主要限制因素来自于导航数据比特的跳变。与GPS有所区别的是,北斗的导航信息上还调制有NH(霍夫曼编码)码[5,6],在相干时间Tcoh的区间内,必须保证导航数据电平与NH 码没有发生跳变,在积分时间Tcoh内的输入信号必须对应同一个数据比特,这个区间以一个导航数据比特持续时间20ms为最大值。在位同步之前,为了保证大多数积分结果不受到数据比特跳变影响,本方案将Tcoh设置为1ms,在位同步完成,能够分出比特跳变边缘后可将之提高为10ms,这样可以大大提高跟踪环路的信噪比,适合用于跟踪状态的精密跟踪。

2.2 载波跟踪环环路控制

环路控制采用FPGA 提供的积分结果,经过DSP 鉴相、鉴频、环路滤波等运算,最后反馈给FPGA,以控制载波。为应对高动态情况下对环路控制的实时性要求,设置反馈控制每0.5ms进行1次。为应对动态性能和抗噪声性能的矛盾,以及更好地提高信噪比。环路对载波的控制策略采用先以较大带宽的二阶FLL 锁频环来闭合环路进行粗跟踪,然后逐渐过渡到三阶PLL 锁相环进行牵入,在位同步完成后,采用变环路带宽机制,以10ms相干积分时间的窄带宽PLL来对跟踪环进行精密跟踪。

2.2.1 载波环鉴别器设计

输入信号中存在有数据调制,即存在180°的相位翻转,所以选用对数据调制不敏感的Costas-PLL(科斯塔斯锁相环),即使导航数据发生比特电平的跳变,依然能保持对载波信号的跟踪。在Costas-PLL的鉴别器算法中二象限反正切算法是唯一一种在输入范围的一般区间保持输出的鉴相器。另外考虑到DSP正好有反正切函数可以直接使用,故本方案采用二象限反正切法做为鉴相器的算法。

鉴频器算法采用交叉·符号(点)的鉴相器算法,该算法对数据比特跳变不敏感,适合牵引状态。另外此算法运算量小,频率牵引范围为检测带宽的1/4,那么1ms的积分时间的1000Hz带宽对应的频率牵引范围为250Hz。由于其斜率正比于信号-幅度,故在计算时需要进行归一化。

2.2.2 环路滤波器设计

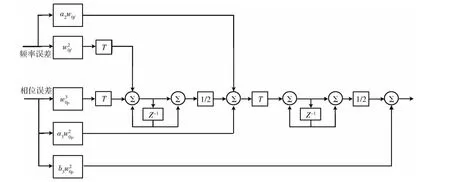

环路滤波器在载波环路中对输入信号的噪声起抑制作用,调节环路的校正速度,最后将结果反馈给载波NCO,使得本地载波与接收信号最终达到完全同步。噪声带宽和阶数对信号的动态响应有直接影响。阶数的选取主要考虑环路的动态性能。本方案中载波跟踪环滤波器采用由二阶FLL辅助的三阶PLL 滤波器。因为有FLL 的辅助,使得该环路组合能在高动态环境下对信号进行快速牵入,又因为有高阶PLL,能实现载波相位的精确测量。环路滤波器结构如图2所示。

图2 环路滤波器结构

文献[7]给出了各阶环路滤波器对应的经典参数值。

BL为噪声带宽又称环路带宽。在高动态环境下,接收的信号载波频率和相位会有大幅度的变化,为保证对信号的跟踪,环路带宽又要大到足以承受由动态引起的波动,保持接收信号的真实性,所以带宽的取值必须在低噪声与高动态之间做出平衡。环路带宽根据频率和相位跟踪的误差来确定,本方案的带宽选取策略是:在牵入阶段,FLL与PLL的带宽在测量误差低于误差门限的情况下选取大带宽以适应高动态环境,在位同步之后的PLL 选用较小带宽以提高搜索精度。

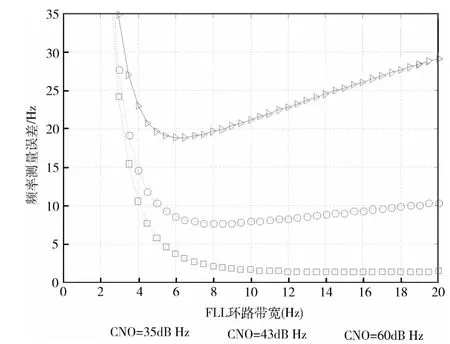

对于锁频环来说,频率测量误差的主要来源是热噪声和动态应力所引起的频率误差。锁频环跟踪门限的一种保守估计方法请参考文献[8],其公式为

式中:σFLL——频率测量的均方误差,σtFLL——热噪声频率抖动均方差,fe——频率跟踪误差。

热噪声频率抖动均方差σtFLL的估算公式为

式中:C/N0——载噪比,当其值较高时参数F 为1,否则为2。另外可以看到热噪声频率抖动均方差与相干时间Tcoh成反比,且Tcoh越大热噪声抖动越小。

频率跟踪误差fe的公式为

式中:wn——与环路带宽BL有0.53 倍关系的特征频率,dN+1R/dtN+1——最大视线方向的加加速度。

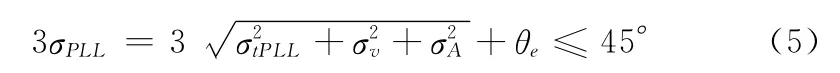

对式(2)~式(4)进行仿真,测试在低、中、高3 种载噪比情况下FLL不同噪声带宽的噪声误差抖动。设定高动态环境,速度为900m/s,加加速度为10g/s,载波波长为19.2cm,相干时间Tcoh为1ms。

由图3可知对于FLL来说,载噪比的差异对带宽的选择有较大影响,在低信噪比环境中提高过多的提高带宽不能降低频率误差。在10g/s的加加速度环境下带宽选择5-12Hz之间噪声最小,若选择带宽为12hz,取一般状态下的载噪比43dBHz,则FLL的测量误差不到10Hz。

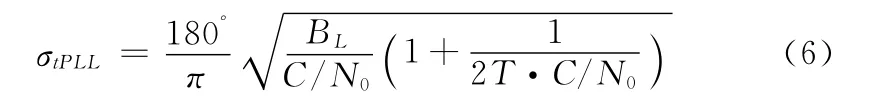

引起PLL频率误差的主要来源是高阶动态应力误差和热噪声均方误差[9,10],选择PLL带宽值的方法与FLL 类似,对PLL的门限进行保守估计。对于二象限反正切法而言,牵入范围为180°则有PLL门限公式[8]

式中:σv、σA——由晶振引起的数量级较小的误差,可忽略不计[7],σtPLL——热噪声均方误差其公式为

图3 二阶FLL在不同信噪比下频率测量误差

θe为动态应力误差,其公式为

对于PLL的带宽选取应分为牵引和跟踪两个部分。在牵引状态下,与FLL的验证方式类似,对式(5)~式(7)进行仿真,在相干时间为1ms时测试高、中、低3种信噪比下,测试PLL不同噪声带宽的测量误差。

在牵入状态中Costas-PLL选用较宽的带宽,从图4中可以看到,带宽越大,误差越小,当带宽大于15Hz时误差开始小于15°。又因为当带宽大于18Hz则系统会出现稳定性问题,故本方案选择带宽为18Hz。

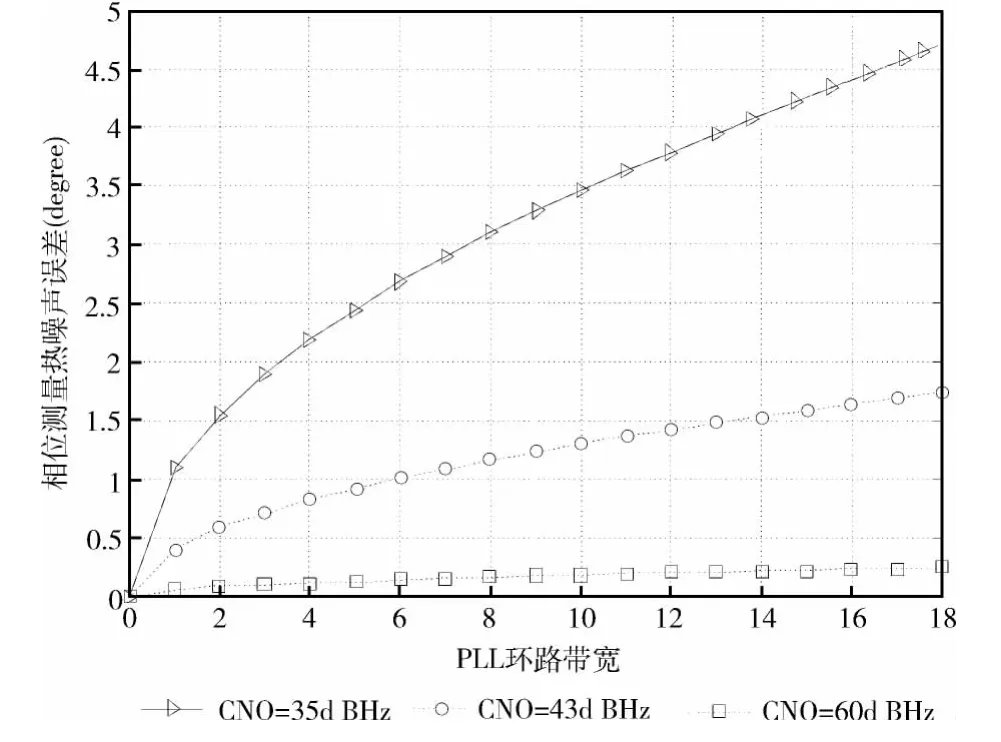

图4 不同载噪比下带宽和相位测量误差的关系

在系统完成位同步之后,环路将改变其带宽,进入窄带宽PLL精密跟踪。此时的高动态特性已经被前面牵入的FLL与PLL 锁定,所以动态引起的误差已经不是跟踪状态造成测量误差的主要因素,需要更窄的带宽来减少热噪声的干扰,从而提高跟踪的精度。由于此时信号比特边缘已经确定,可以选用更长的积分时间(大于1ms)提高信噪比,设定积分时间Tcoh为10ms,在不同载噪比下,测试PLL 带宽与热噪声震动的关系。结果如图5所示。

图5 窄带PLL不同载噪比下不同带宽和相位测量误差的关系

由图5可以看到,热噪声误差随带宽减少而减少。取带宽BL=10Hz为变环带宽后的方案,在一般载噪比情况下,热噪声误差不到0.5°。

3 环路控制软件流程

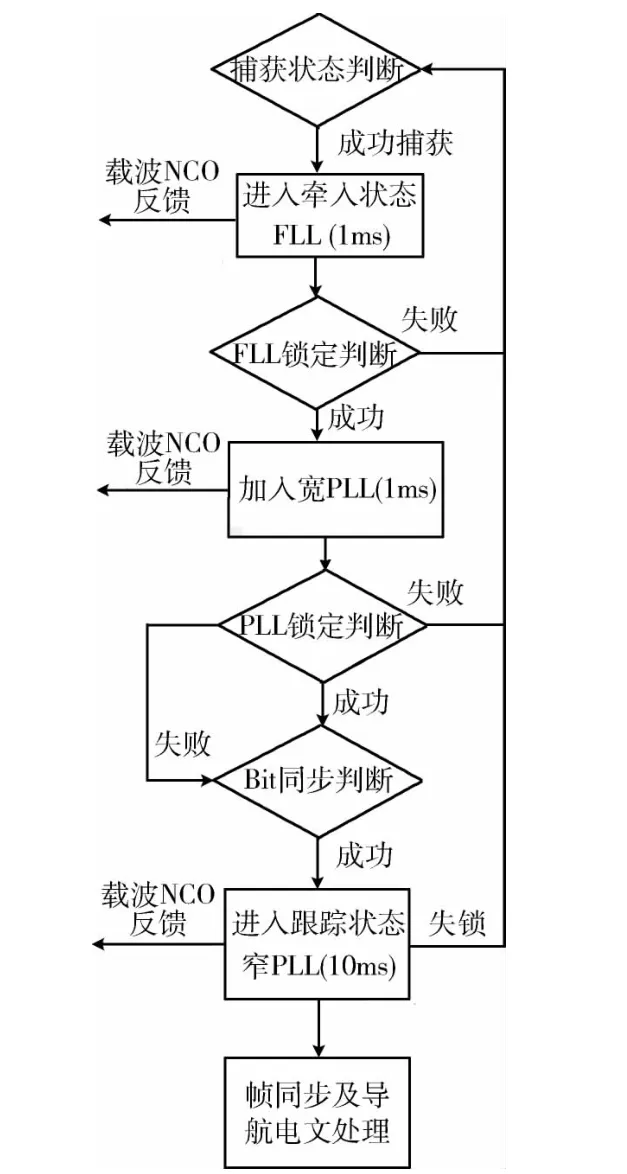

本方案环路控制利用数字电路易于调节的优势,采用变环路带宽机制,在牵入和跟踪状态使用不同的环路带宽和不同的相干时间。接收机工作中对卫星进行捕获,当捕获到某颗卫星后该系统便进入牵入状态,DSP 端软件流程如图6所示。

图6 环路控制流程

在捕获完成后需要把信号误差牵引进跟踪可扫描到的范围之内,先用10Hz的环路带宽,相干积分时间1ms的FLL进行频率牵引,设置牵引时间500ms,对FLL 进行锁定判定,判定成功后,加入带宽BL为18Hz的PLL进行相位牵引,积分时间选用经典值1ms,此时FLL与PLL 同时工作。当位同步成功,即能分辨得出数据比特跳变后,系统进入跟踪状态,此时频率误差已经被牵入到很小的范围,为提高信噪比,增加相干累积时间为10ms,将PLL环路带宽减小至10Hz,对其进行严密跟踪。要注意的是,因为北斗B1频点的导航数据调制有NH 码,故10ms的相干积分要与NH 码相乘,要在偶数毫秒上进行相干积分的累加。在牵引和跟踪过程中,DSP 利用每隔0.505ms的中断,反馈一个载波NCO 对载波进行实时剥离。若在跟踪过程中发生了失锁,则程序跳回捕获状态重新捕获。

4 测试结果与性能分析

将射频前端系统,预处理模块和本方案设计的载波跟踪系统共同组成一个北斗接收机平台,通过天线接收导航信号,对本方案进行实际测试。在DSP端显示输出波形。

在环路滤波器控制程序中PLL 鉴相器输出端口和FLL的输出端口生成数组,并于CCS软件界面显示波形图如图7所示,上图是FLL与PLL两环路误差之和,下图是锁频环单独的输出。可以看到,程序刚开始时,环路误差很大,此时先通过FLL 快速削弱频偏,过了500 个点后(对应500ms)FLL输出趋于稳定,误差之和逐渐趋于稳定,此时再切换PLL通过反馈,对载波进行快速牵引。测试表明本方案有良好的载波跟踪性能。

图8为北斗7号卫星在接收机剥离了载波和伪码之后I支路和Q 支路的输出,因为本方案采用的I/Q 解调法,所以其剥离结果会使Q 支路的信号功率仅仅只剩下噪声,而I支路输出信号功率会保持最大,呈现方波变化,每20个点(对应20ms,北斗7号卫星是MEO 卫星,数据速率50bps)就可能有电平变化,此时呈现的正是导航电文。测试表明,接收机在实际工作中,载波跟踪环能很好地对输入信号载波进行剥离,FPGA 端的载波NCO 模块能即时反馈的载波频率步长,对载波频率进行实时控制。

图7 FLL与PLL误差输出和 (上)锁频环误差输出 (下)

图8 北斗7号卫星I支路 (上)Q 支路 (下)载波剥离后的输出结果

5 结束语

本方案采用FPGA+DSP 实现北斗接收机中载波跟踪环的功能,在高动态环境下对FLL和PLL的测量误差进行分析,得到相应的优选参数,并利用变带宽技术完成对环路的控制。与接收机其它模块组合在一起,最终得到导航电文。实时测试结果表明,该设计具有很好的导航信号载波跟踪性能,灵活性强,很容易移植到其它导航接收机中。下一步的工作,在不断完善该设计的同时,将对其跟踪精度和抗多径干扰性能进一步进行研究测试。

[1]FIE Pan,SONG Peng,QI Jianzhong.The compass B1frequency navigation receiver research and implementation [C]//Third Annual Meeting of China Satellite Navigation Conference Anthology-S07Compass/GNS Navigation Application,2012(in Chinese).[费攀,宋鹏,齐建中.北斗二代B1频点导航接收机的研究与实现 [C]//第三届中国卫星导航学术年会电子文集-S07北斗/GNSS用户终端技术,2012.]

[2]YAN Feng,XIE Jing,MAO Zhigang.GPS carrier tracking loop design [J].Electronic Measurement Technology,2008,31 (11):140-142 (in Chinese).[言峰,谢憬,毛志刚.GPS载波跟踪环设计 [J].电子测量技术,2008,31 (11),140-142.]

[3]Alizera Razavi,Demoz Gebre Egziabher.Carrier loop architectures for tracking weak GPS signals[J].Aerospace and Electronic System,2008,44 (2):697-710.

[4]Elliott Kaplan D,Christopher Hegarty J.Understanding GPS principles and applications[M].Beijing:Publishing House of Electronics Industry,2007:119-121 (in Chinese). [Elliott Kaplan D,Christopher Hegarty J.GPS原理与应用 [M].北京:电子工业出版社,2007:119-121.]

[5]SHI Xiangnan,BA Xiaohui.Research on acquisition methods for the B1signal of MEO/IGSO in BDS [J].Foreign Electronic Measurement Technology,2013,32 (4):19-21 (in Chi-nese).[史向男,巴晓辉.北斗MEO/IGSO 卫星B1频点信号捕获方法研究 [J].国外电子测量技术,2013,32 (4):19-21.]

[6]ZHANG Bingqi,LIU Feng,CHEN He.Research on compass B1open service signal modulation [J].Scientia Sinica Physica,Mechanica & Astronomica,2011 (5):52-57 (in Chinese).[张炳琪,刘峰,陈禾.北斗B1频点公开服务信号调制方式研究 [J].中国科学:物理学,力学,天文学,2011 (5):52-57.]

[7]XIE Gang.Principles of GPS and receiver design [M].Beijing:Publishing House of Electronics Industry,2009:266-301 (in Chinese).[谢钢.GPS原理与接收机设计 [M].北京:电子工业出版社,2009:266-301.]

[8]WU Cailun,LU Mingquan,FENG Zhenming.Carrier loop’s performance evaluation and simulation in high dynamic GNSS receiver[J].Modern Radar,2011,33 (7):65-66 (in Chinese).[伍蔡伦,陆明泉,冯振明.高动态GNSS 接收机载波环性能评估与仿真 [J].现代雷达,2011,33 (7):65-66.]

[9]HU Rui,XUE Xiaozhong,SUN Ruisheng.Carrier loop design for high dynamic GPS signal based on DSP+FPGA [J].Master’s Degree Thesis of National University of Defense Technology,2010,34 (1):76-77 (in Chinese). [胡锐,薛晓中,孙瑞胜.基于DSP+FPGA 的高动态GPS信号载波环路设计 [J].南京理工大学学报 (自然科学版),2010,34(1):76-77.]

[10]WANG Jun,LI Jiaqi.Tracking error analysis of FLL-assisted-PLL [J].Journal of Beijing Institute of Technology,2011,31 (7):838-839 (in Chinese).[王俊,李加琪.锁频环辅助下锁相环的跟踪误差分析 [J].北京理工大学学报,2011,31 (7):838-839.]