基于FPGA的视频信号采集技术研究

梁发云,何 辉,施建盛,王思涵,刘 果,张 华

(1.南昌大学裸眼立体技术与虚拟现实研究中心,江西南昌330031;2.南昌兴亚光电科技发展有限公司,江西南昌330031)

裸眼3D设备使用双视图模拟双眼图像,其视频文件数据量大并要求实时处理,电路设计有其特殊性[1]。ARM芯片兼容多种操作系统,显示界面美观,有丰富的应用程序,具有多种通用外部设备接口如:Flash Memory、SD card、网络接口、LCD接口等。FPGA(可编程逻辑门阵列)以其高速并行的数据处理能力在视频数据处理领域中应用广泛,FPGA特别适合在立体视频数据实时处理和传输中的应用。

本文提出一种ARM+FPGA的电路结构[2],通过FPGA的内部逻辑设计实现对ARM的LCD接口视频数据进行采集、缓存等处理,实验表明系统准确采集视频数据为立体视频图像算法实现提供支持[3]。

1 系统总体结构

ARM处理器是32位精简指令集处理器架构,具有高性能、体积小、功耗低等特点,FPGA的灵活性和高速数据处理能力使其很适合系统的视频数据采集和处理,系统采用ARM+FPGA的硬件结构。

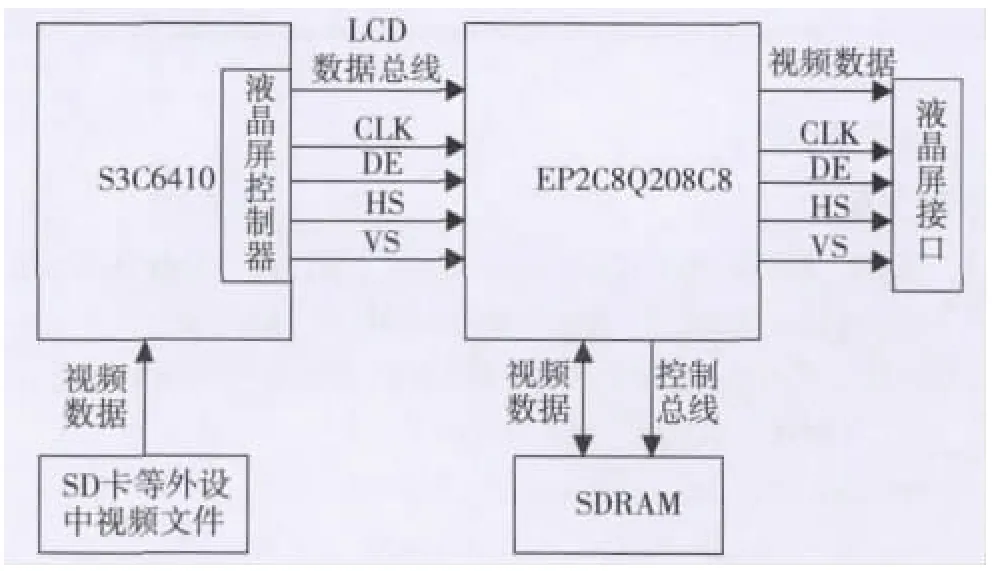

ARM选用S3C6410作为主控模块,FPGA选用Altera Cyclone II系列EP2C8Q208C8为从模块。S3C6410安装经过个性化定制的Windows CE6.0系统,负责管理外设和支持各种应用程序。ARM的LCD接口信号主要有:DE(Data Enable,显示数据有效信号)、HS(Horizontal Synchronization,行同步信号)、VS(Vertical Synchronization,场同步信号)、CLK(像素时钟)和RGB像素数据线[4]。将数字RGB和液晶屏控制信号连接到EP2C8Q208C8的管脚,通过FPGA处理后再输入到3D液晶屏的信号接口,系统总体结构如图1所示。

图1 系统结构图

为了完成ARM输出的视频信号采集,FPGA的控制逻辑应包括系统控制模块、数据采集模块、SDRAM控制器、LCD 驱动模块[5](见图 2)。ARM 输出的像素时钟CLK 为33.3 MHz,EP2C8Q208C8外部时钟为50 MHz,而SDRAM控制器工作频率为120 MHz,所以在此结构中涉及到异步时钟域数据的同步问题。系统控制模块具备时钟管理功能,产生3个时钟信号33.3 MHz、120 MHz、120 MHz相移-108°,并产生稳定的复位信号。

图2 FPGA逻辑设计结构图

2 视频数据采集

2.1 视频接口

FPGA采集管脚连接ARM的LCD数据接口,对ARM输出的视频数据进行采集,通过缓存和数据处理,在输出端连接3D液晶屏。S3C6410和EP2C8Q208C8相互配合完成视频数据的高速采集[6]。ARM视频输出接口、FPGA数据采集管脚和LCD接口相互对应关系如表1所示。

表1 ARM视频输出、FPGA采集管脚和LCD接口定义

2.2 数据采集

视频数据采集模块使用ARM显示输出接口的像素脉冲作为时钟,FPGA内部设计异步FIFO_in实现采集像素时钟与SDRAM控制器时钟匹配,FIFO_in位宽为16 bit,深度1 024大于一行视频数据像素个数[7]。FIFO_in的写入端由S3C6410控制,当INDE信号为高电平时格式转换模块将ARM视频输出的24 bit RGB888数据做位拼接,拼接成RGB565格式便于16位宽的SDRAM数据读写,数据拼接代码

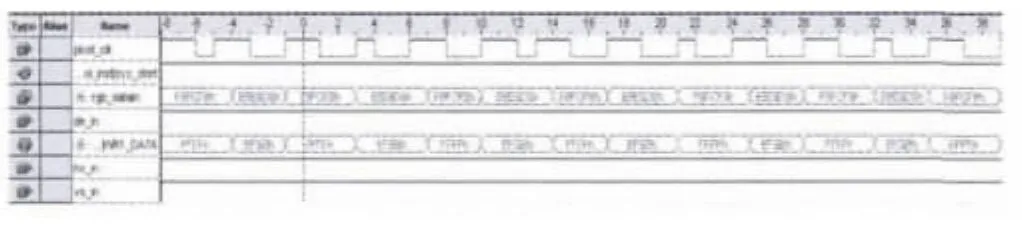

图3是使用Quartus II 10.1软件中嵌入式逻辑分析仪捕获到的数据采集模块采集数据和位拼接的波形图,拼接完成后16 bit数据WR1_DATA写入到FIFO_in中,每个INDE周期写入一行视频数据。FIFO_in的输出端连接到SDRAM控制器,当一行像素数据写入完成且优先级控制信号有效时,向SDRAM控制器发出写请求,将采集到的数据突发写入到SDRAM中。FIFO_in的复位信号连接到系统控制模块的全局复位端。

图3 采集ARM视频输出数据并进行位拼接(截图)

3 图像数据缓存

视频图像数据量大,像素时钟较高。SDRAM(同步动态随机存储器)需要不断地刷新每个存储单元来保持数据,控制较复杂。系统设计专门的SDRAM控制器,完成SDRAM的初始化、预充电、刷新、读、写等操作。将SDRAM操作封装成控制器,只留出控制和数据接口,使SDRAM的操作大为简化[8]。SDRAM控制器状态机如图4。

图4 SDRAM控制器状态机

SDRAM选用Hynix公司的HY57V641620,内部结构为4 Bank×1M×16 bit,共64 Mbit存储容量。SDRAM控制器上电延时200μs进行初始化,首先对所有Bank预充电,随后连续进行8次刷新操作,刷新完成加载模式寄存器设置SDRAM工作方式,初始化完成进入空闲等待状态,可以响应读、写或刷新命令。数据采集模块检测VS(场同步信号)的下降沿,当检测到下降沿表明一帧视频图像的开始,将系统开始信号sys_start置为高电平。图5是使用嵌入式逻辑分析仪捕获到的检测到VS_in下降沿时的波形。

图5 捕获VS_in下降沿系统开始工作(截图)

图5中pixel_clk是ARM显示输出33.3 MHz像素脉冲,nege_vsin检测到VS_in的下降沿时拉高一个时钟周期,sys_start信号锁存nege_vsin高电平状态,整个系统开始工作。SDRAM读和写都采用全页突发模式,提高了数据存取效率。当FIFO_in中写入一行像素数据和优先级控制信号有效时,对SDRAM控制器发起写请求。系统视频分辨率为800×480,每一帧图像包含800×480=384 000个像素点,经过采集模块转换后一帧图像有384 000个16 bit数据,需要在SDRAM中开辟2个相同大小的缓存区。HY57V641620一个Bank的容量为1M×16 bit=1 024×1 024×16 bit=1 048 576×16 bit,满足系统一帧视频数据缓存要求且留有足够的余量便于系统升级。VS_in信号的下降沿作为帧缓存区选择信号,当帧数据缓存区写满时将data_valid拉高,LCD_DE液晶屏控制模块按照LCD时序从FIFO_out中读出视频数据,FIFO_out使得SDRAM控制器和LCD控制模块的数据跨时钟域稳定传输。

4 图像显示

采用普通7 in(1 in=2.54 cm)分辨率为800×480的液晶显示屏作为系统前期验证,在LCD控制模块中使用了参数化设计,将行像素脉冲数、场像素脉冲数、消隐前肩、消隐后肩、同步脉冲宽度等使用参数化定义,只要修改相应的参数就可以支持非标准时序的3D液晶屏。

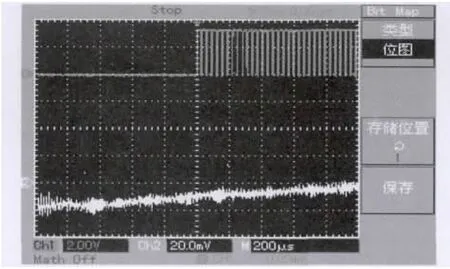

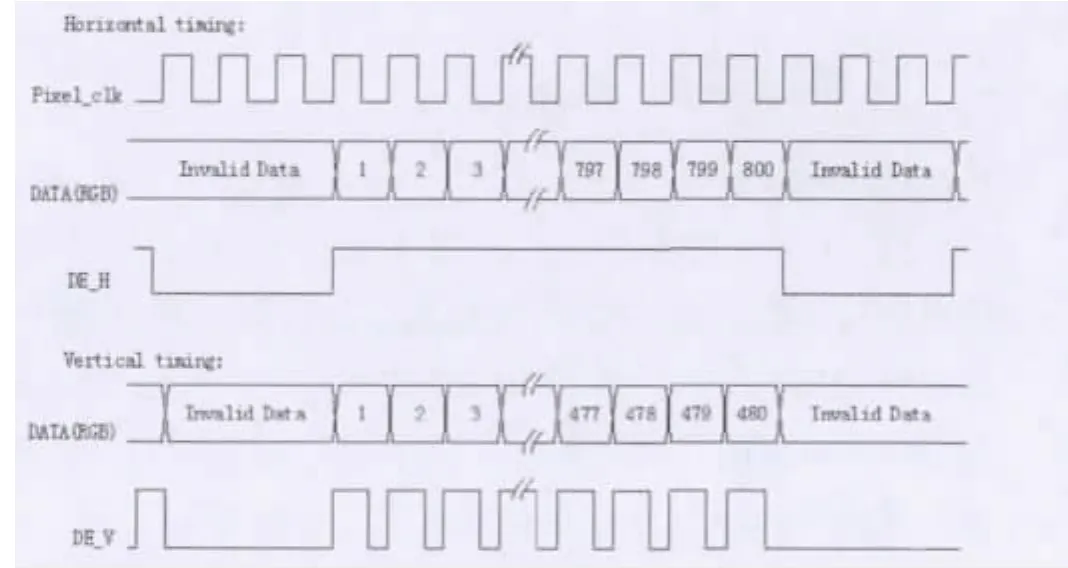

LCD驱动方式分为DE模式和SYNC模式[9]。其中DE模式中的DE信号包含有行场时序信息,相当于HS、VS两个信号的复合同步信号,在内部逻辑实现时使用h_cnt和v_cnt两个计数器来产生DE信号,DE信号为高电平时LCD显示当前接收到的图像数据。使用示波器测得的液晶屏控制器输出DE信号波形如图6所示。每行DE信号周期为30 ns×1 056=31.68μs,每场DE信号周期为31.68 μs×740=23.443 2 ms。SYNC 模式可以称它为同步模式,使用HS做为行同步信号,VS作为场同步信号,数据有效信号作为数据传输的使能信号。系统采用了DE模式,只使用像素时钟CLK和DE信号来控制LCD图像显示更为简便。7 in LCD的DE模式时序如图7所示,LCD控制模块使用行、场计数器产生DE信号和rdf_outreq(FIFO_out读请求信号)。

图6 液晶屏控制器DE信号(截图)

图7 LCD的DE模式时序

5 仿真分析及实验

使用ModelSim对LCD控制模块和数据采集过程进行仿真。数据采集过程时序波形如图8a所示。数据采集过程以行像素为单位更新写缓存区,当FIFO_in中写入0~799的24位像素数据和优先级控制信号有效时,对SDRAM控制器发出写请求,SDRAM突发控制逻辑响应写请求写入一行数据到帧缓存区。行显示周期为31.68μs,写入一行数据需800×(1/(120 MHz))=6.667μs,加上SDRAM突发操作所消耗的时间也能满足LCD时序,行周期剩余时间SDRAM数据总线由LCD控制器控制,使得图像数据稳定传输。图8b是在硬件平台上加载配置文件使用嵌入式逻辑分析仪调试波形图,可以看到LCD控制模块从FIFO_out中读出数据输出到液晶屏上显示。

图8 仿真和硬件测试波形(截图)

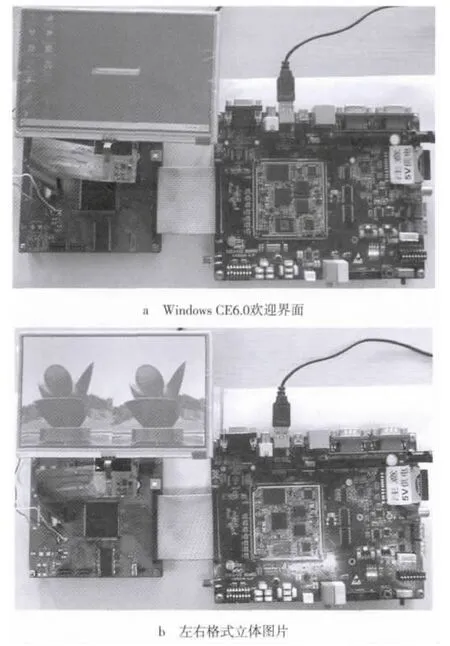

系统使用普通7 in LCD进行了实验,完整采集到ARM输出的视频信号,系统工作正常,且复位稳定。图9a是FPGA完成视频数据采集、缓存和驱动LCD显示的Windows CE6.0欢迎界面,图9b是使用图片浏览器播放左右格式立体图片。

图9 系统调试完成实验显示效果

6 小结

便携式裸眼3D设备具有广阔的发展前景,本文提出的ARM+FPGA硬件结构,充分利用两者的优势,解决视频文件解码和较大数据量的视频数据缓存问题,完成了数据采集、缓存和显示功能。系统工作稳定,且通过修改FPGA逻辑设计可以采集ARM输出的多种分辨率视频信号,可以支持不同尺寸和非标准时序的裸眼3D显示屏,具有较强的通用性,为便携式裸眼3D设备图像数据处理提供支持。

[1]梁发云,邓善熙,杨永跃.立体图像视频格式及其转换技术研究[J].仪器仪表学报,2005,26(12):1233-1237.

[2]张挺飞,樊永生,孙凌云.基于FPGA+ARM的智能图像门控系统[J].电视技术,2012,36(17):156-158.

[3]吴禄慎,任丹.面外“moire”计算机图像处理技术的研究[J].南昌大学学报:工科版,2000,12(22):1-5.

[4] 邓中亮,肖冠兰.Windows CE6.0下LCD驱动程序移植[J].计算机与现代化,2011(1):14-17.

[5]吴继华,蔡海宁,王诚.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2011.

[6]刘爽,赵凯生,龙再川,等.基于ARM和FPGA的嵌入式CCD采集系统[J].光电子·激光,2007,18(11):1296-1298.

[7] Altera Corporation.Cyclone II device handbook[EB/OL].[2013-11-6].http://www.altera.com.

[8] ZHU Jiayi,LIU Peilin,ZHOU Dajiang.An SDRAM controller optimized for high definition video coding application[C]//Proc.ISCAS.Seattle:IEEE Press ,2008:3518-3521.

[9]干莽,齐贵宝,陈捷,等.基于FPGA与SDRAM的高效LCD控制器设计[J].吉林大学学报:信息科学版,2013,31(4):380-384.