基于FPGA的成像系统自动曝光算法设计

李 华

(商洛学院 电子信息与电气工程学院,陕西商洛 726000)

在基于CCD/CMOS图像探测器的成像过程中,曝光控制对成像质量影响很大[1],特别是视场处在背光或者正对强光时,如果曝光不当,将会使成像效果很差,甚至成像失败。所以,曝光时间的正确选择将直接影响到整个成像系统的成像质量。自动曝光控制技术是用来调节CCD/CMOS图像探测器中像素单元的曝光时间和前端模拟电路中数字可编程增益放大器的增益,从而使图像亮度达到目标亮度值范围内,以符合用户对成像质量的需求[2]。所以自动曝光是电子技术与人工智能的产物,即不需要外部人为操控,因此,在成像系统中使用的越来越普遍[3-4]。可见,对自动曝光控制算法的研究与设计具有重要的理论意义与现实应用价值。

本文系统以Xilinx公司的FPGA—XC2V3000为主控芯片,实现了对CMOS图像探测器—LUPA-4000图像的采集,重点介绍了图像分块自动曝光算法在FPGA中的实现。同时给出了系统的实际成像效果。

1 系统组成及工作原理

本文设计的应用于CMOS成像系统的自动曝光算法以FPGA为核心[5-7],其作用是用于产生LUPA-4000图像探测器的参数配置时序和工作驱动时序信号;同时运行自动曝光算法,利用当前帧图像计算得到曝光参数,作用于下一帧图像;并适应存储与显示需要对输出图像进行格式重组等。整个系统充分发挥了FPGA并行运算的优势,有效提高了自动曝光控制的实时性和精度。本文系统的原理框图见图1所示。

图1 系统原理框图

系统的具体工作过程为:FPGA上电稳定后根据默认成像环境参数,首先利用寄存器配置单元通过SPI配置LUPA-4000探测器的相关寄存器,配置结束后为其提供包括曝光时间在内,正常工作所需的时序信号,由于LUPA-4000探测器内部集成了10位的AD,这时,LUPA-4000就可以输出10 bit数字图像用于后端FPGA处理。由于本文系统图像帧频为10 f·s-1,图像输出比较慢,因此采用了连续帧曝光调节,即当第一帧图像进入FPGA时,首先将其送入自动曝光算法,通过图像分块、亮度统计、结果比对等操作,输出新的曝光时间参数,同时将参数输送给LUPA-4000时序控制模块,产生新的时序信号,并在探测器工作间隙提供给探测器,这样,第二帧图像就会按照新的曝光时间进行工作。假如这时成像环境发生变化,第二帧图像的曝光参数显然又不能应用到下一帧,所以这时还要将矫正好曝光时间的图像继续送给自动曝光算法,用于统计图像亮度信息,计算得出新的曝光参数,作用于第三帧图像的曝光,如此反复就完成了图像的自动曝光控制。最后再按照存储与显示单元对图像格式的要求对输出的图像进行格式重组,包括图像信息添加、数据填充、并串转换等操作后输出,完成整个过程。

2 系统设计

分析图1所示的系统原理框图可以看出,整个成像系统主要由三大功能组成:LUPA-4000时序设计、自动曝光算法和图像格式重组。

2.1 LUPA-4000驱动设计

LUPA-4000是ONSEMI公司生产的一款CMOS图像探测器,有效像素2048×2048,像素大小 12 μm×12 μm,采用改进的 6 T 快照式像素结构,读出速度最高达66 MHz。线性响应下的光学动态范围为66 dB,如果采用双线性或者多线性响应,最高可以达90 dB[8]。

LUPA-4000时序由两部分组成,参数配置和时序驱动[9]。其中,参数配置的宽度为32位,包括Y方向、X方向、开窗等8个功能,采用SPI方式,由 clock_spi,spi_in 和 load_addr完成。而时序驱动主要由 mem_hl,sample,precharge,reset,norowsel,pre_co,sh_co,vol_average,sync_y,clock_y,sync_x,clock_x等信号组成,用于完成曝光和读出等操作。特别强调的是LUPA-4000的曝光时间是由reset信号的作用时间决定的,其低电平持续时间越长,曝光时间就越长,因此,本文自动曝光算法的控制本质上是对reset低电平长度的控制。

2.2 自动曝光算法设计

2.2.1 传统的自动曝光算法

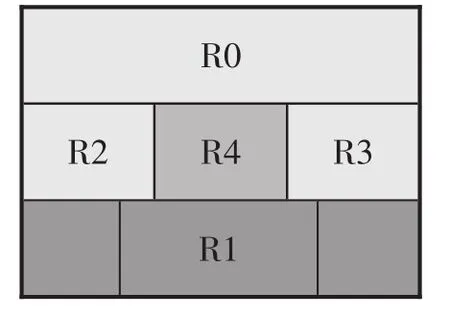

传统的自动曝光系统将整幅图像的亮度均值与预先设定的参考值比较进行曝光控制。当图像中主要拍摄对象与背景对比度较低时,图像能够得到较好的重现。然而当主要拍摄对象与背景反差过大时,图像中高亮度区域产生过饱和,低亮度区域显得黑暗,从而导致图像中主要拍摄对象的过曝或欠曝。而目前很多自动曝光算法是将图像分为若干块,按照块之间的亮度对应关系判断背光或者正面强光场景,并对不同的块分配不同的权重。根据加权像元灰度值来改变曝光时间。图2所示为文献[10]给出的一种常用的自动曝光算法中的图像分割方法,将一帧图像分为5块,在大多数情况下,背景处于图像的上半部分,主体被摄物处于中下位置。根据亮度不同对背景及主体物附加不同比重的加权值,这样它们之间的亮度差就得到了补偿。

图2 传统自动曝光算法图像分块原理

2.2.2 本文改进算法原理

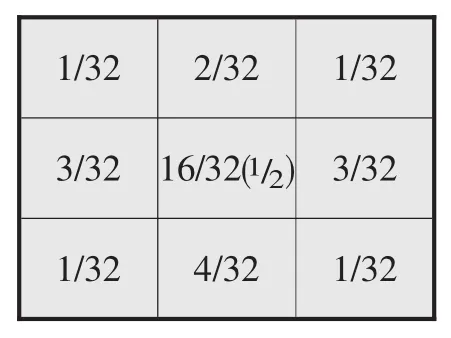

针对传统自动曝光算法的不足,本文在文献[10]思想的基础上结合实际项目成像要求对自动曝光算法进行了改进,主要是增加了图像块数目的划分,同时增加了中心感兴趣区域的权重,本文算法图像块的划分和权重分配如图3所示。这样,即使感兴趣区域以外处于背光或正对光也不会对整体成像效果产生太大的影响。

图3 本文自动曝光算法图像分块原理图

本文自动曝光算法具体设计方面主要是通过调整低电平持续时间来调整曝光时间,调整范围分为0-511档,每档步距为20 μs。曝光时间和曝光档位的关系是:曝光时间=曝光档位 *20 μs+10 μs,曝光档位范围为[0,511]。

考虑到图像的像元灰度值与曝光时间在图像探测器的未饱和区域符合线性关系,因此根据当前帧图像的曝光档位told、灰度均值DNold以及设定的下一帧图像的期望灰度值DNnew,就可以计算出下一帧图像的曝光档位tnew,计算过程如式(1)所示:

其中:told表示当前帧图像曝光时间档;DNold表示当前帧图像的灰度加权值;tnew表示下一帧图像曝光时间档;DNnew表示下一帧图像的灰度加权值。

当系统加电正常工作时,由于是按照默认曝光时间注入的参数,因此探测器输出的图像是默认曝光时间,即当前帧图像曝光档位told是已知的,这时将该帧图像进行像元灰度值的加权统计得到DNold。考虑到现实中一幅图像的亮度并非一定要达到一个绝对的理想值时图像亮度才算是合理的,在理想亮度周围稍微有些偏差并不会对图像的质量造成很大影响,因此定义图像期望亮度不是某一个定值,而是为某一个区间,本文设定的图像期望灰度均值为[550,650],即DNold也是已知的。因此,利用公式(1)可以求出下一帧图像曝光档位tnew,再将其通过LUPA-4000时序控制单元注入探测器,完成自动曝光。

2.2.3 改进算法的FPGA硬件实现

由于FPGA逻辑单元丰富、并行运算能力强大、购买渠道畅通,且高等级产品(宇航级等)比较多,考虑到算法的应用范围,本文系统使用了FPGA作为算法硬件实现平台。

本文算法基于FPGA的硬件实现过程为:当LUPA-4000图像探测器正常工作,输出第一帧图像进入FPGA时,首先根据感兴趣区域的大小,定义了9个图像块的宽度和高度。然后再定义9个寄存器,用于存放分块图像中各个图像块包含像元的和 (寄存器可根据分块图像的大小设置成不同的位宽),这样,就可以计算每个图像块的像元和了。具体操作过程以左上角第一个图像块为例进行说明,当FPGA捕获到第一个行有效的上升沿时,开始将像元逐个累加至第一个数据寄存器,当第一行累加到第一个图像块的宽度时,停止操作,等待第二行图像的到来继续进行累加操作,如此重复,直到第一个图像块的高度时结束累加,第一个图像块的像元累加结束,再将求和结果求平均,因为在分块时尽量将图像块取成2的指数倍,例如:256、512等,因此,在求平均时仅用移位寄存器即可完成,因此,计算量很小。其它图像块的计算与第一个图像块的计算大同小异,这样,在一帧图像结束时就可以求出各个图像块的加权DN值,然后根据权重求出一帧图像的平均DN值,这时只要应用式(1)就可以得到新的曝光时间参数,从而完成自动曝光控制。

从以上分析可以看出,整个过程仅有一次除法,其它计算均由加法和移位操作组成,因此,整个算法占用的硬件资源很少,同时可以做到实时处理。

2.3 图像数据重组功能设计

图像重组功能主要是按照存储与显示单元的要求对来自探测器的图像进行格式的重组,主要是添加帧头信息、填充数据等,然后进行组帧,并串转换后输出给存储与显示单元。帧头信息包括图像拍摄的时间、曝光时间、增益等,填充数据主要是将图像数据包填满,以固定长的数据包传输。并串转换则主要为了简化数据传输宽度,减少误码率。

帧头信息的添加在FPGA内的实现主要是先在FPGA内开辟一小块存储区(一般为若干行图像的宽度)将图像暂时缓存,待信息添加完毕,再传输图像,从而完成帧头的添加。并串转换也是在FPGA内完成,主要的原理是设计一个控制过程,判断一个数据的10位转换是否完成,如果完成,将下一个转换数据进行转换,如果没有完成,可将下一个输入数据进行存储,当前转换完成后再进行转换。

3 实验结果与分析

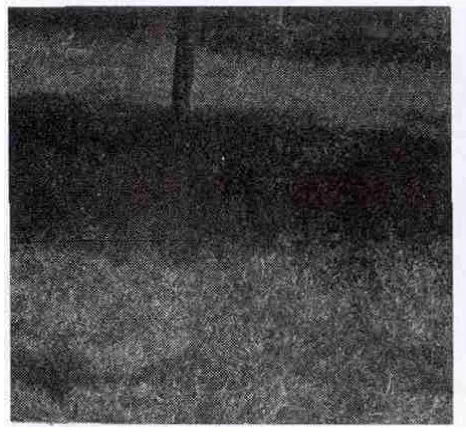

算法硬件设计好后结合光机系统进行了成像试验,图4所示为应用文献[10]思想设计的算法得到的图像,由于过于强调下半部分,所以中心感兴趣区域曝光不足;而图5是本文算法拍摄的图像,可以看出,虽然图像的上下部位光线比较强,但是,拍摄到的图像依然能将中心感兴趣区域景物清晰的展现出来,证明了本文算法的可行性与正确性。

图4 传统算法图像

图5 本文算法图像

4 结语

本文利用图像分块与权重分配原理,设计了一种易于FPGA硬件实现的改进自动曝光算法,并将其应用到了实际成像系统中,取得了较好的效果。本文算法设计灵活,可以根据实际成像环境对图像分块大小和权重大小进行更改;另一方面,本文算法硬件设计简单,没有使用复杂的IP核,方便移植,适合各种以FPGA作为逻辑控制单元的成像系统,因此,具有较好的通用性。

[1]陈绕青,曹 国,毛志红.一种空间面阵CCD成像的曝光时间计算方法[J].计算机工程,2012,38(12):1-4.

[2]戈志伟,姚素英,徐江涛,等.一种应用于CMOS图像传感器的快速自动曝光控制方法[J].天津大学学报,2010,43(10):854-859.

[3]Kuno T,Sugiura H,MatobaN.A new automatic exposure system for digital still cameras[J].IEEE Transactions on Consumer Electronics,1998,44(1):192-199.

[4]Cho M H,Lee S G,Nam B D.The fast auto exposure algorithm based on the numerical analysis[C]//SPIE conference on sensors,cameras,and applications for digital photography.San Jose,1999:120-128.

[5]邸丽霞,张彦军,洪应平.基于FPGA的高速图像数据采集存储系统设计[J].电视技术,2013,37(13):49-52.

[6]李 华.基于SDRAM的Bayer格式图像插值算法硬件设计[J].电视技术,2013,37(5):49-51.

[7]杨光宏,高 伟,黎向阳,等.利用FPGA实现TDICCD自动曝光控制[J].科学计算与工程,2007,7(16):4179-4182.

[8]LUPA-4000 Datasheet[DB/OL].http://www.onsemi.cn.

[9]陈 彦,张宏伟,林宏宇.基于FPGA的CMOS图像传感器LUPA-4000时序设计[J].航天器返回与遥感,2012,33(5):62-67.

[10]甘玉泉,高 伟.一种基于图像分区的自动曝光算法[J].微计算机信息,2009,25(3/4):303-305.