一种模数混合结构的延迟锁相环设计

唐 宁,张莲莲,张 可

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.东北大学理学院物理系,沈阳110004)

一种模数混合结构的延迟锁相环设计

唐 宁1,张莲莲2,张 可1

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.东北大学理学院物理系,沈阳110004)

数字系统通信的不断发展,多种延迟锁相环结构的出现满足了不同应用要求。提出了一种模/数混合结构的延迟锁相环,改善了传统模拟锁相环和传统数字锁相环各自的缺点,在数字系统中作为集成电路模块单元使用。采用TSMC的0.25μm,1P5M,CMOS混合信号工艺进行加工制备,模块单元面积140×190μm2。

延迟锁相环;混合结构;集成电路模块

1 引 言

随着集成电路工艺技术进入深亚微米时代,对微处理器和图像处理等系统电路提出了加快时钟频率和降低功耗的要求。集成电路模块之间的时钟同步成为设计上关注的重要问题,因而,大量的设计努力集中在高性能的数字接口电路与数字系统之间的通讯上。

延迟锁相环作为一阶反馈系统,具备无条件稳定,快速锁定时间及更好的防抖动特性,一直广泛地应用于微处理器、存储器及集成电路通讯中。传统的模拟延迟锁相环,具有更好的防抖动和偏移特性,但是受工艺、温度等因素影响严重;传统的数字延迟锁相环,具有更快的锁定时间,更好地抑制工艺、温度因素的影响,但是更差的防抖动和偏移特性。提出了一种新型的模数混合结构的延迟锁相环,能够有效地改善上述问题,作为IC模块嵌入在C8051F500系列微处理器系统中。

2 结构及原理

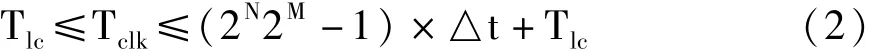

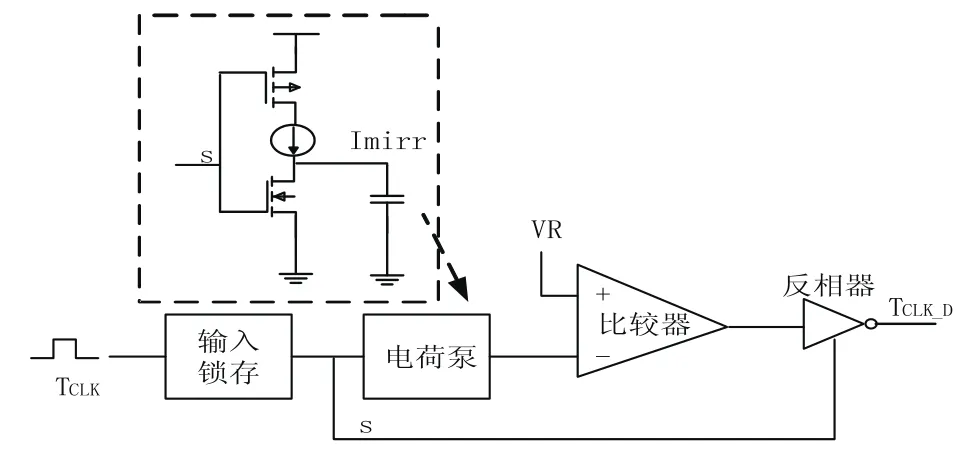

图1给出模数混合结构延迟锁相环的框图,主要由鉴相器、控制器、压控延迟线和延迟单元四部分组成。鉴相器单元捕捉输入时钟和输出时钟相位差,通过控制器转换为N位粗调控制信号和M位精调控制信号,依次调节压控延迟线中电荷泵结构的充放电电流路数,从而达到延迟单元延迟时间的功能,最终保证输出时钟和输入时钟相位差趋近于零,进入锁定状态。

精调控制信号产生的延长时间是对粗调控制信号产生的1LSB延迟时间(td)的插值,精调最小延迟分辨率可以表示为:

当延迟锁相环进入锁定状态时,总延迟时间为一个时钟周期,延迟锁相环能够处理的时钟频率范围为:

式中,Tclk是输入时钟周期;Tlc是当所有控制信号都为低时延迟锁相环固有的延迟时间;设定的输入时钟范围越大,容纳外界干扰锁定的能力越强。由式(1)和式(2)可知,可以增大N或td来扩展输入时钟频率范围,但增大N意味着增大电路硬件的复杂度,增大td意味着降低时序的分辨率,因此,输入时钟频率范围的设计是这两个因素的折中考虑。

图1 混合结构延迟锁相环功能框图

3 主要单元模块设计

3.1 延迟单元

如图2所示,延迟单元通过压控延迟线调节环路滤波电容的充电电流(Imirr)的镜像值,设定充电电压的上升时间,依次调节延迟单元的延迟时间。

图2 延迟单元功能框图

3.2 压控延迟线单元

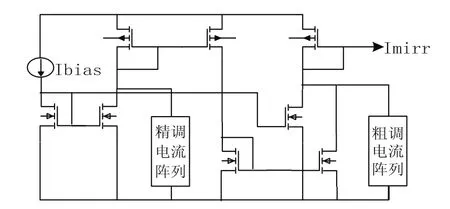

如图3所示,压控延迟线单元的主要功能是利用2N个粗调控制位和2M个精调控制位调节镜像电流(Imirr)与偏置电流(Ibias)的比例关系,控制延迟单元的延迟时间。精调电流与粗调电流的权重关系由电流镜加权实现。

图3 压控延迟线单元功能图

4 仿真结果

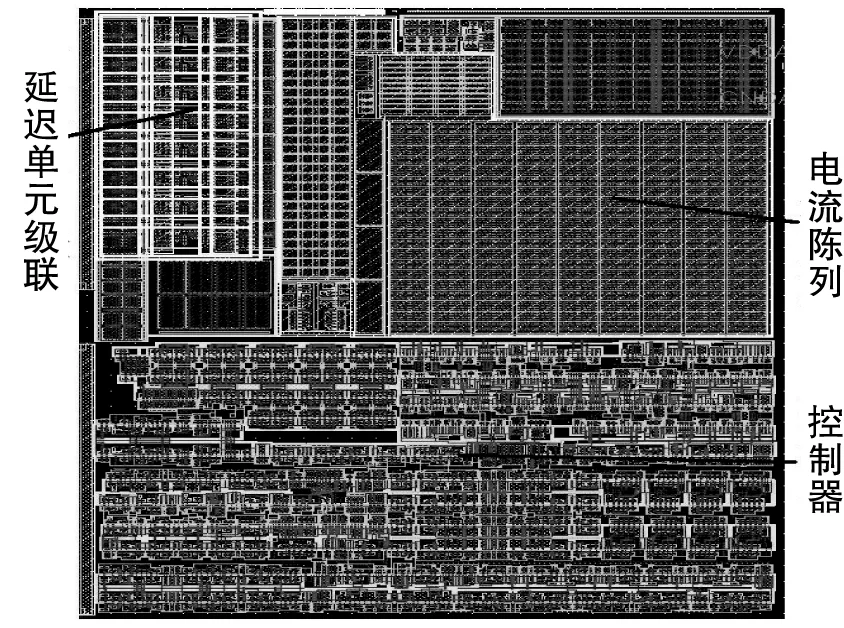

本电路基于TSMC的0.25μm,1P5M,CMOS混合信号工艺进行加工制备,版图结构如图4所示。

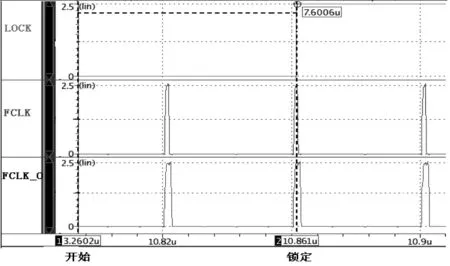

利用CALIBRE工具对版图数据抽取进行仿真,得到图5所示的波形。由图可知,对于25MHz的输入时钟信号,电路经过192个时钟周期,进入锁定状态,捕获时间7.6μs。仿真结果证明了该混合结构延迟锁相环性能的优良性。

图4 延迟锁相环版图结构

图5 TT,25℃下25MHz输入频率锁定波形图

5 结束语

提出了一种数模混合结构的延迟锁相环电路,它能够有效地改善传统的数字DLL和模拟DLL各自的不足之处,可以作为单片电路或单元模块应用到微处理器等数字系统通讯领域。

[1] YMoon,et al.An all-analog multiphase delay-locked loop using a replica delay line for wide-range operation and low-jitter performance[J].IEEE J.Solid-State Circuit,2000,35(3):377-384.

[2] Y Okajima,M Taguchi.Digital delay locked loop an design technique for high-speed synchronous interface[J].IEICE Trans.Electron,1996,E79-C(6):798-807.

[3] HH Chang,S J Liu.A wide-range and fast-locking all-digital cycle-controled DLL[J].IEEE J.Solid-State Circuit,2005,40(3):661-670.

Design of A Kind of Hybrid-structure Delay Locked Loop

TANG Ning1,ZHANG Lian-lian2,ZHANG Ke1

(1.The47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China 2.Physics Department,Collage of Sciences,Northeast University,Shenyang 110004,China)

With the development of digital communication system,the advent of several structures of delay locked loop can satisfy the demand of specs in different applications.An analog-digital hybridstructural delay locked loop,as an IC-modular utilized in a large scale digital system,which improved the drawbacks of traditional analog DLL and digital DLL,is described in this paper.TSMC 0.25μm,1P5M,CMOSmixed-signal process are used in the circuitwith themodular area of 140×190μm2.

Delay locked loop(DLL);Hybrid-structure;IC-modular

10.3969/j.issn.1002-2279.2014.02.004

TP492

A

1002-2279(2014)02-0011-02

唐宁(1981-),男,辽宁鞍山人,工程师,主研方向:混合信号集成电路设计研究。

2013-03-15