基于FPGA的P2020处理器显示接口设计

陈 武,夏坤健,袁 静

(重庆金美通信有限责任公司,重庆400030)

基于FPGA的P2020处理器显示接口设计

陈 武,夏坤健,袁 静

(重庆金美通信有限责任公司,重庆400030)

针对目前使用的飞思卡尔高性能通信处理器P2020无内置LCD控制器,不方便在某些需要显示界面的中小设备中直接应用的问题,提出了基于CPU+FPGA的显示接口设计方案,给出了硬件原理框图、FPGA逻辑实现原理框图以及设计结果,在项目中成功应用并满足需求。

现场可编程门阵列;LCD控制器;RGB接口;有限状态机

1 引 言

在中小型通信设备尤其是需要满足严酷工作环境的设备中,需要一个简洁的显示窗口时,由于目前大部分通信处理器没有提供显示接口,很多方案设计时选择增加专用显示控制器或增加负责人机界面的协处理器,这样的方案既增加设备成本又增加PCB尺寸。

随着FPGA技术的成熟应用,大部分通信设备采用的是基于CPU+FPGA的方案实现,因此为系统在FPGA中添加设计LCD控制器,是一种方便、经济实用的方案。本方案就提出了基于xilinx公司XC3S200AN和处理器P2020的LCD显示方案及其设计实现。

2 系统硬件设计

系统采用CPU+FPGA为主架构,采用SDRAM存储芯片作为LCD控制器的显示缓存。处理器采用飞思卡尔公司新推出的低功耗45nm高性能双核处理器P2020E,该处理器最高主频为1.2GHz,集成PCIE、SGMII等接口,系统原理如图1所示。

图1 系统原理框图

3 系统逻辑及软件设计

3.1 LCD控制器逻辑组成

系统FPGA使用XC3S200AN,该FPGA内部集成flash,不需要外部配置芯片,并包含288Kb的块RAM,系统使用这些内部块RAM作为读写缓存,调度SDRAM的读写。

图1中FPGA部分为LCD控制器逻辑组成及各模块的数据流连接关系。处理器通过总线将显示内容写入数据缓存,总线读写控制模块通过判断数据缓存以及显示缓存的状态,将数据送至SDRAM控制器,SDRAM控制器负责SDRAM数据的读写控制。LCD时序控制模块从显示缓存中读取显示数据并将其转换为RGB接口数据格式送至外部的LCD显示屏。

3.2 LCD控制器设计原理

本系统使用TFT显示屏,分辨率为320×240,刷新率60Hz。根据TFT显示屏原理,其显示总线接口主要包括像素时钟(DOTCLK)、像素数据(DATA)、数据使能(DEN)、行同步信号(HSYNC)、场同步信号(VSYNC)。本系统场同步信号(VSYNC)频率为60Hz,每一帧包含240行显示数据,则行同步信号(HSYNC)的周期为1/(60×240)s,加上场回扫时间tvFP及tvBP,那么行同步的周期为15KHz,又因一行有320个像素点,同理计算,像素时钟(DOTCLK)可取5MHz。系统时钟(sys_clk)为100MHz,与DOTCLK一样均由FPGA内部PLL输出。

3.3 LCD时序产生

时序产生模块使用两个简单关联的有限状态机(Finite-state machine,FSM)实现,其中HBP、HFP、VBP、VFP以及HSYNC和VSYNC的极性设计为变量,可由处理器通过参数寄存器模块按需进行设置。图2是LCD接口时序信号产生状态机的状态图。其中H_cnt、D_cnt以DOCLK时钟计数,V_cnt以H_start_flag计数,HBP、HFP、VBP及VFP为参数寄存器的值。用VHDL语言设计实现图2状态机,通过Modelsim仿真,其仿真结果如图3所示,满足LCD接口时序要求。

3.4 SDRAM控制器及读写控制

SDRAM控制器完成SDRAM上电初始化及读写控制。使用SDRAM必须先进行初始化,设置SDRAM工作模式。根据使用的芯片手册,其初始化流程如图4所示。其中预充电命令需要对所有bank进行预充电。各命令间均需要至少等待上一条指令执行的时间。在使用SDRAM期间为保持数据内容,SDRAM需要定时自动刷新,这一时间间隔要求由芯片手册给出。本系统使用的SDRAM芯片要求自动刷新命令的最大间隔时间为15.625μS。

图2 LCD时序产生状态机

图3 接口时序仿真结果

图4 SDRAM初始化流程

系统利用两个内建FIFO及LCD接口回扫时间(HFP、HBP)调度SDRAM数据的读写。首先在判定CPU接口FIFO的empty_flag有效时读取显示FIFO的状态和RGB总线状态。当FIFO为full或者almos empty_flag无效时则将CPU接口FIFO的数据读取写入SDRAM中,否则应从SDRAM中读取数据存入显示FIFO中。当显示FIFO的almos empty_ flag有效时,则判断RGB总线状态是否处于回扫(HFP或HBP),若是则将CPU接口FIFO的数据读取写入SDRAM中,否则应从SDRAM中读取数据存入显示FIFO中。

3.5 内建FIFO

显示缓存FIFO由FPGA内部块RAM设计为环形FIFO缓存,并有指针清零使能。该使能位用于复位块RAM读写指针,每当一帧开始时使能该标志以使得FIFO中数据与显示坐标点一一对应。

由于P2020的LocalBUS的高16位地址与数据位为复用接口,需先对地址锁存,之后与数据一同存入CPU接口FIFO,SDRAM读写模块根据地址将数据写入SDRAM相应地址中,这样系统就可以单独修改任意一个像素点数据。

3.6 系统软件设计

本项目操作系统为linux2.6.x,显示部分采用传统的帧缓冲(framebuffer)接口,framebuffer通过对图像硬件底层的屏蔽以及显示缓冲区的抽象,允许上层应用程序直接操作显示缓冲区而不关心底层的具体硬件实现,是Linux系统为显示设备提供的一个接口。

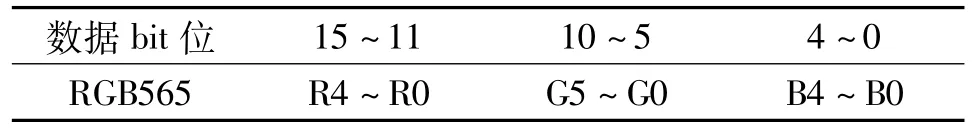

Framebuffer设备为标准的字符设备,系统中对应/dev/fb%d设备文件,主设备号29。对于这类framebuffer设备而言,只要在与显示像素点一一对应的显示缓冲区域写入颜色值,对应的像素点将自动显示写入的颜色。表1列出了RGB565接口中显示缓冲区与显示像素点的对应关系,例如要在第n点显示红色,则在缓冲区偏移量为n的地址写入0xf800即可。

表1 显示缓冲与像素点对应关系

图5展示了系统利用framebuffer接口移植的QT图形界面。

图5 QT图形界面

4 结束语

本系统利用FPGA的高度灵活性,在不增加系统成本及PCB空间的基础上,为通信处理器设计实现了显示接口,在实际应用中刷新率达到了60Hz,完全满足项目的需求。同时通过简单的修改接口逻辑,该显示方案还支持军用设备常使用的超宽温的4位EL显示屏,并且已经在多个项目中使用。

[1] 薛小刚,葛毅敏.Xilinx ISE 9.X FPGA/CPLD设计指南[M].北京:人民邮电出版社,2007.

[2] 宋宝华.Linux设备驱动开发详解[M].北京:人民邮电出版社,2008.

[3] 余春蕾,张长明.基于FPGA的TFT-LCD控制器设计[J].电子技术,2008,45(5):15-17.

[4] Xilinx Corp.Spartan-3AN FPGA Family DataSheet[M].2008-6.www.xilinx.com.

Design of Disp lay Interface of P2020 Processor Base on FPGA

CHENWu,XIA Kun-jian,YUAN Jing

(Chongqing Jinmei Communication Co.,Ltd.,Chongqing 400030,China)

Aiming at the problems caused by the most of the high-performance communication processor,which has no built-in LCD controller and is not convenient to be used in some middle and small size communication apparatus for display interface,a new design of the display interface based on CPU+FPGA is described in this paper.It provides the block diagram of hardware,FPGA logic block diagram and achievement results,which are successfully applied in the project tomeet the requirements.

LCD control;FPGA;Framebuffer;FSM

10.3969/j.issn.1002-2279.2014.02.003

TP37

A

1002-2279(2014)02-0008-03

陈武(1984-),男,桂林人,本科,主研方向:嵌入式系统硬件设计及其应用。

2013-07-26