HDLC协议IP核的设计与实现

闫军虎,张明社,郗海燕

(中国电子科技集团公司 第39研究所,陕西 西安 710065)

HDLC协议IP核的设计与实现

闫军虎,张明社,郗海燕

(中国电子科技集团公司 第39研究所,陕西 西安 710065)

文中针对专用ASIC芯片实现HDLC协议针对性强,使用不灵活等特点,提出了使用FPGA IP核来实现HDLC接口的设计方案。HDLC IP核包括3个模块:对外接口模块、接收模块和发送模块。IP核接收到新数据后存入接收FIFO,对外接口模块将接收到的数据通过总线将数据送入数据处理单元;当需要发送数据时数据处理单元通过总线将数据存入发送FIFO,启动发送模块将数据送出。接收和发送模块自动完成数据的"插零"及"删零"操作。仿真结果表明该IP核能够正确的接收和发送数据。该方法已在某雷达天线的同步引导数据的收发通信链路中,成功实现了双向数据通信。

FPGA;HDLC协议;IP核;FIFO;CRC 校验

在某雷达测控系统中,采用面向位的、简化的高级数据链路控制(High-Level Data Link Control或简称HDLC)协议进行数据交换。 HDLC协议具有数据报文透明传输、全双工通信、传输可靠性高等特点,从而广泛应用于数据通信领域。

通常HDLC协议的实现是采用专用的ASIC 器件来实现的[1]。HDLC的ASIC芯片有ST公司的MK5025、Motorola公司的MC92460、Zarlink公司的MT8952B等[2]。这些集成电路功能针对性强,性能可靠,适合应用于特定用途的大批量产品中。但由于HDLC标准的文本较多,ASIC芯片出于专用性的目的难以通用于不同版本,缺乏应用灵活性。HDLC的软件编程方法功能灵活,通过修改程序就可以适用于不同的HDLC应用。但程序运行占用处理器资源多,执行速度慢,对信号的时延和同步性不易预测。

FPGA(Field Programmable Gate Array, 现场可编程门阵列)采用硬件技术处理信号,又可以通过软件反复编程使用,能够兼顾速度和灵活性,并能并行处理多路信号,实时性能能够预测和仿真。在中小批量通信产品的设计生产中,

用FPGA实现HDLC功能是一种值得采用的方法。正是有鉴于此,Innocor、Xilinx等公司推出了能在FPGA中实现HDLC功能的IP Core(Intellectual Property Core,知识产权核),但这些IP Core需要付费购买许可(License)才能使用,且在应用中受到各种限制。本文从HDLC的基本定义出发,通过对FPGA设计输入的模块化描述,介绍一种能够在FPGA中实现HDLC功能的方法。

1 HDLC的帧结构

首先回顾一下HDLC基本的帧结构形式。HDLC是面向比特的链路控制规程,其链路监控功能通过一定的比特组合所表示的命令和响应来实现,这些监控比特和信息比特一起以帧的形式传送。每帧的起始和结束以"7E"(01111110)做标志,两个"7E"之间为数据段(包括地址数据、控制数据、信息数据)和帧校验序列。帧校验采用CRC算法,对除了插入的"零"以外的所有数据进行校验。为了避免将数据中的"7E"误为标志,在发送端和接收端要相应地对数据流和帧校验序列进行"插零"及"删零"操作。

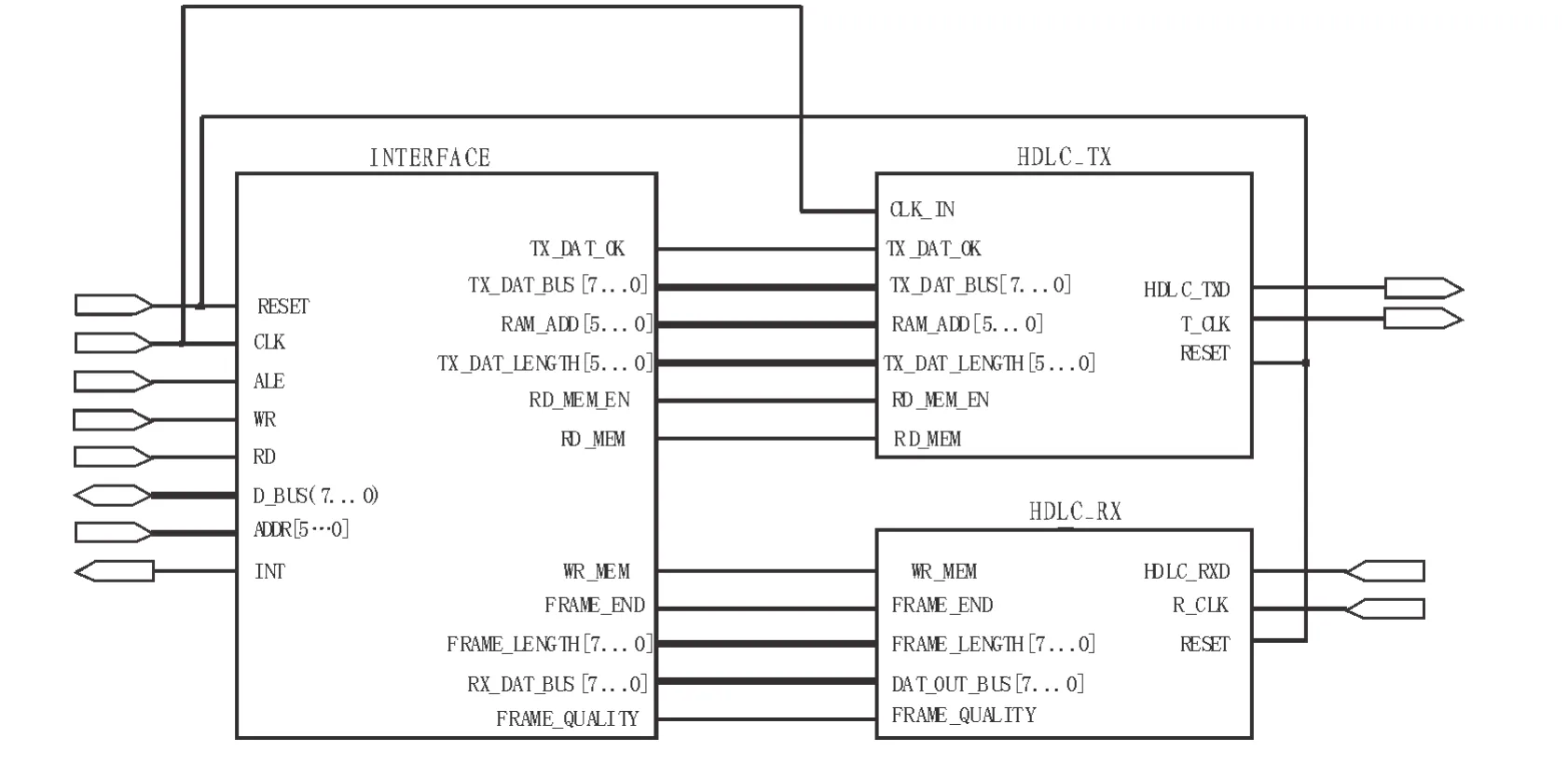

2 原理框图

基于FPGA的HDLC协议的实现原理框图如图1所示。该框图包括3个部分:对外接口部分、HDLC发送部分、HDLC接收部分。以下对3个部分的实现分别进行论述。

2.1 对外接口模块

图1 HDLC协议原理框图Fig. 1 Block diagram of HDLC protocol

对外接口部分主要实现HDLC对外的数据交换。包括CPU接口、发送FIFO、发送接口、接收FIFO以及接收接口。本设计是以总线的形式实现HDLC与外部CPU的通信。当需要发送数据时,外部CPU通过总线将待发数据写入FIFO(FIFO的IP核在各开发软件中都是免费提供的,在程序中只需直接调用即可,故在此不再详细描述)。之中。发送数据准备就绪标志(TX_DAT_OK);接收数据时,当对外接口模块接收到数据有效信号时,根据接收模块发来的写信号(WR_MEM)将数据写入接收FIFO中。接收完一帧数时向CPU发送中断信号(INT),通知CPU读取数据。

2.2 HDLC发送模块

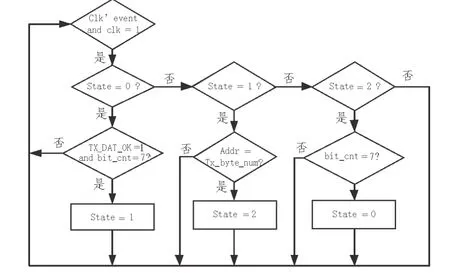

HDLC发送部分主要实现HDLC发送功能。当接收到数据准备就绪标志(TX_DAT_OK)后,向对外接口模块发送读使能(RD_MEM_EN)和读信号(RD_MEM),通过局部总线将待发数据存入发送缓冲区,在T_CLK的控制下将数据从HDLC_TXD管脚发出。数据发送模块采用状态机来完成发送各个阶段的切换。状态切换流程图如图2所示。

图2 发送模块状态切换流程图Fig. 2 Switch flow diagram of transmit module

State0状态是发送的起始状态也是空闲状态。当没有数据要发送时(TX_DAT_OK=0),程序以7E填充发送;当程序检测到有新数据时(TX_DAT_OK=1),程序检测7E是否发送结束如果没结束则继续发送7E,如果7E发送结束则状态在下一周期切换为State1。

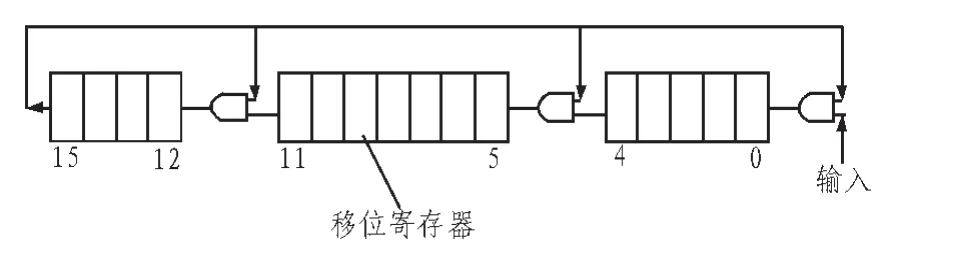

State1状态主要完成接收并发送数据功能,在第二个CLK周期先将读使能和读信号拉高,在第三个CLK周期再将其拉低,在第五个CLK周期开始读数。在并行的数据发送PROCESS中根据CLK周期和发送计数器,将接收到的数据通过移位进行发送同时对连续‘1’的个数和发送个数进行计数。当连续‘1’的个数为5时在下一个周期插入发送‘0’,将连续‘1’的计数器清零,发送个数不变。在发送数据的同时进行CRC校验的计算。帧校验序列字段使用CRC-16,对两个标志字段之间的整个帧的内容进行校验。CRC的生成多项式为X16+X12+X5+1,对在校错范围内的错码进行校验。标志位和按透明规则插入的所有‘0’不在校验的范围内。程序设计中的CRC校验算法的原理框图如图3所示。

图3 CRC校验算法的原理框图Fig. 3 Block diagram of CRC verfiy

State3 状态主要完成发送字尾,发送完成后直接转入state0。

2.3 HDLC接收模块

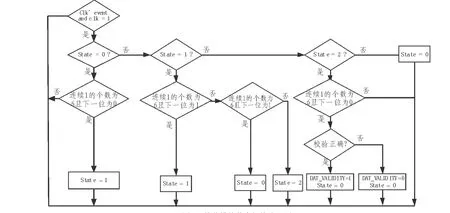

接收模块接收到一个非“7E”字节时,即判定为地址数据,直到再次接收到“7E”即判定为接收到了一个完整的一帧数。当接收到一个非“7E”数据后就通过内部数据总线(DAT_OUT_BUS)传送给接口模块,接口模块根据FRAME_LENGTH和DAT_VALIDITY来判断数据帧的长度和有效性。接收数据个阶段的状态切换流程如图4所示。

在State0状态程序判断接收到的数据是否为7E,如果为

图4 接收模块状态切换流程图Fig. 4 Switch flow diagram of receive module

7 E,则表明已收到了帧头,状态切换到State1。在State1状态程序接收到的下一个数不是7E则表明收到了地址数据,将状态机切换到State2。在State2状态判断是否收到字尾,如果不是字尾则将接收的数据存入接收缓冲区同时启动写数据,将接收到的数据通过总线写入接收fifo。在收数的过程中同时进行删除‘0’的操作,即当收到连续5个1时将下一个‘0’主动删除。当收到字尾时对地址数据、控制数据和信息数据的CRC校验结果与最后两个字节进行比对形成数据有效标志(DAT_VALIDITY)。

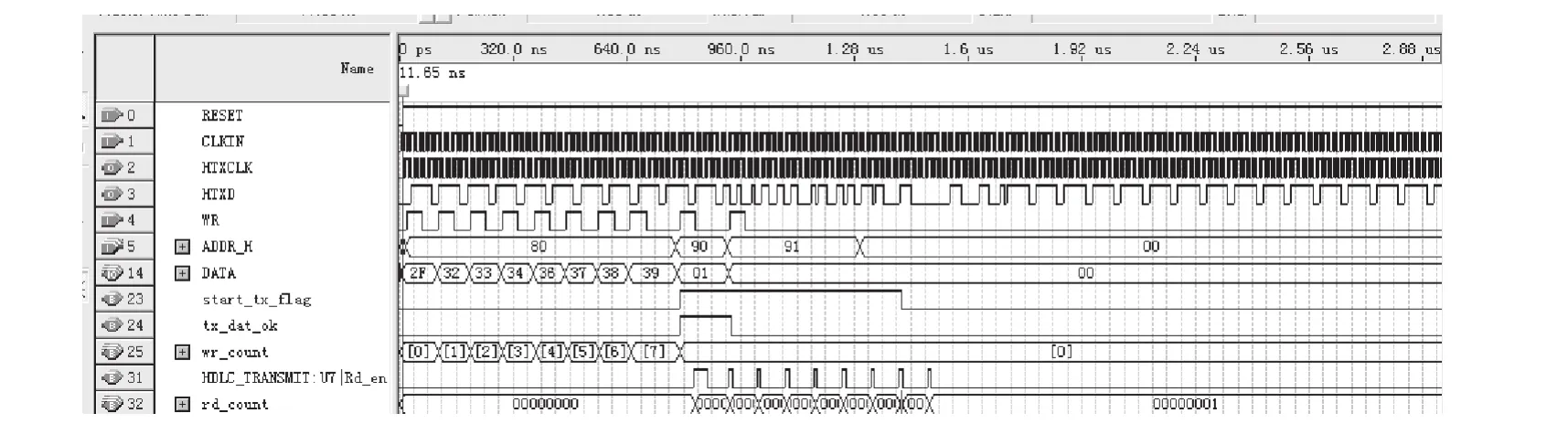

图5 发送数据仿真波形Fig. 5 Simulation waveform of transmit data

3 仿真与应用

根据上述设计,在Quartus II 9.0上对发送数据和接收数据进行了仿真如图5、6所示。

图6 接收数据仿真波形Fig. 6 Simulation waveform of receive data

从仿真波形可以看出发送模块能够将FIFO中的数按照设计的波形输出到HTXD管脚;接收模块能够正确的将HRXD管脚的波形数据解出来并存入接收缓冲区中,接收完成后给接口模块发出END标志。根据上述设计方法,已成功地在可编程逻辑芯片上实现。FPGA芯片选用的是Altera公司的Cyclone系列FPGA:EP1C6T144。

4 结束语

上述详细介绍了一种基于FPGA的HDLC协议IP核的方案及设计实现方法。根据本文介绍的实现方法设计出的HDLC接口板已应用于某雷达天线的同步引导数据的收发通信链路中,成功实现了双向数据通信。应用结果表明该方法具有简单实用、性能可靠以及成本低等特点。能够广泛应用于HDLC协议应用场合。

[1] 韩露.专用HDLC协议芯片的应用[J].移动通信,2003,27(11):231-232.

HAN Lu.Application of special HDLC protocol chip[J]. Mobile Co mmunication,2003,27(11):231-232.

[2] 付新虎,史浩,等.HDLC协议在通信系统中的应用[J].电子技术,2005,32(8):58-60.

FU Xin-hu,SHI Hao,et al.Application of HDLC protocol in a communication system[J].Electronic Technology,2005,32(8):58-60.

[3] 李宥谋,房鼎益.CRC编码算法研究与实现[J].西北大学学报:自然科学版,2006,36(6):895-898

LI You-mou,FANG Ding-yi.Research and implementation of a new CRC coding algorithm[J].Journal of Northwest University:Natural Science Edition,2006,36(6):895-898.

[4] 刘岩俊,闫海霞.HDLC通讯协议中CRC的应用[J].电子测量技术,2010,33(3):21-23.

LIU Yan-jun,YAN Hai-xia.Application of CRC during HDLC protocol [J].Electronic Measurement Technology,2010,33(3):21-23.

[5] 肖静娴,戴亚文.基于FPGA的异步FIFO缓存设计[J].电子测量技术,2010,32(11):92-94.

XIAO Jin-xian,DAI Ya-wen.Implementation of asynchronous FIFO buffer based on FPGA[J].Electronic Measurement Technology,2010,32(11):92-94.

[6] 范昌平,应三丛.多雷达的一种高可靠智能接入和规范处理[J].四川大学学报:自然科学版,2006.43(4):763-765.

FAN Chang-pin,YIN San-cong.a high reliable intelligent access and standard treatment of multi radar[J].Journal of Sichuan University:Natural Science Edition,2006,43(4):763-765.

Design and realization of the HDLC protocol with FPGA IP core

YAN Jun-hu, ZHANG Ming-she, XI Hai-yan

(The 39th Institute ,Electronic Science and Technology Group Corporation of China, Xi’an 710065, China)

Using the special ASIC to realize the HDLC protocol is not flexible. The paper describes a scheme which using the FPGA IP core to realizing the HDLC protocol. The IP core includes the external interface module;receive module; transmit module. When the IP core receive new data ,it will storage the data in receive fifo. The external interface module will send out the data to the processor form the data bus. When send data, the processor will send the data to the transmit fifo,and startup the transmit module. The receive and transmit module will execute the“insert zero”and“delete zero”automatic. The emulational result indicate that the IP core can receive and transmit date correctly. The scheme has carried out the communication of the synchronous lead date in radar antenna.

FPGA; HDLC protocol; IP core; FIFO; CRC verify

TN820.4

A

1674-6236(2014)11-0181-04

2013–09–16 稿件编号:201309121

闫军虎(1971—),男,陕西渭南人,高级工程师。研究方向:微电子技术应用。