一种对失调和电容失配误差进行补偿的流水线ADC子级电路

戴 强,薛 颜,杨霄垒,周启才,2,吴 俊,郭良权*

(1.中国电子科技集团第五十八研究所,江苏 无锡 214035;2.江南大学物联网工程学院,江苏 无锡 214122)

一种对失调和电容失配误差进行补偿的流水线ADC子级电路

戴强1,薛颜1,杨霄垒1,周启才1,2,吴俊1,郭良权1*

(1.中国电子科技集团第五十八研究所,江苏 无锡 214035;2.江南大学物联网工程学院,江苏 无锡 214122)

摘要:设计一种用于高速高精度流水线ADC的流水线ADC子级电路,采用伪随机序列控制子ADC电路中比较器阵列的参考比较电压。比较器的高低位被随机分配,消除某个比较器的固有失调对子ADC量化的影响,温度计码的伪随机性可以消除MDAC电容的失配误差对余量输出的影响。电路采用0.18 μm 1P5M 1.8 V CMOS工艺,运用于12 bit 250 Msample/s流水线ADC电路中,实际测得流水线ADC电路的SNR为69.92 dB,SFDR为81.17 dB。

关键词:流水线模数转换器;伪随机序列;失调误差;电容失配误差

数字处理技术和数字处理系统的快速发展和更新换代,为模数转换器ADC(Analog to Digital Converter)提供了大量的应用机会,近年来,高速高精度的模数转换器在高清视频、3 G通信、医疗器械以及雷达等领域得到了广泛的应用,作为高速高精度领域模数转换器的最佳选择,流水线ADC的性能更是得到了飞速提升。

为实现更高性能(更高速度、更高精度、更低功耗)的流水线ADC设计,各大机构投入了大量的研究,如在流水线ADC的高位子级电路中对MDAC(Multiple Digital to Analog Converter)电容使用DITHER技术补偿电容的失配误差[1],并结合数字校准技术来提高流水线ADC的转换精度;在流水线ADC的高位子级电路中对比较器内部电路进行失调电压补偿[2],降低高速动态比较器固有的较大的失调电压对流水线ADC转换精度的影响;使用简单的运放电路来替代高增益高带宽的放大器电路,并结合后台的数字校准技术校准比较器失调和MDAC电容失配[3-8],在实现所需精度的前提下达到降低功耗的目的。

本文设计另一种应用于高速高精度流水线ADC的子级电路,该子级电路基于伪随机控制技术,以一种自适应的方式来达到提高流水线ADC转换精度的目的。

1 电路设计

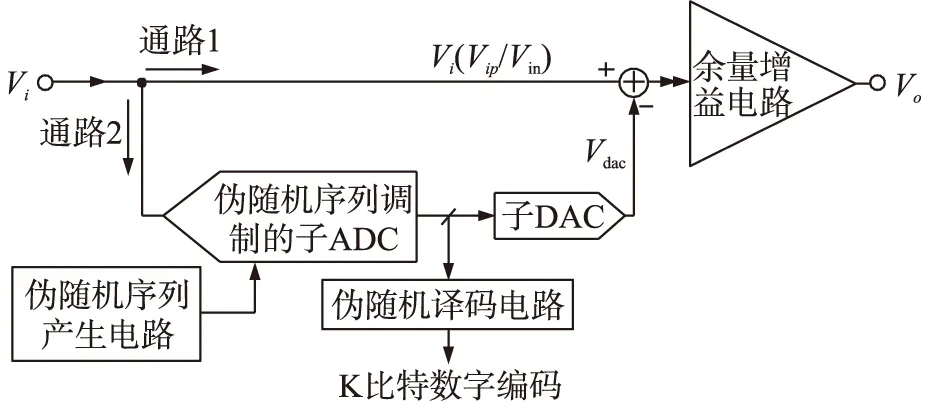

图1所示为本文设计的流水线ADC的K比特子级电路的原理框图,该子级电路包括伪随机序列调制的子ADC电路、子DAC电路以及余量放大器、伪随机译码电路和伪随机序列产生电路。

图1 子级电路原理框图

该子级电路的工作原理如下:通路1由余量增益电路中的采样开关对前级输出的信号(或输入信号)Vi(Vip/Vin)进行采样/保持,通路2由伪随机序列调制的子ADC电路对前级输出的信号(或输入信号)Vi(Vip/Vin)进行采样/保持并进行比较器量化,子ADC电路中的比较器阵列的参考电压受伪随机序列产生电路生成的伪随机序列控制,因此该子ADC电路输出的温度计码具有伪随机性质,温度计码一方面经子DAC电路转换得到模拟信号Vdac,另一方面经伪随机译码电路译码得到该子级电路的Ni-bit数字编码输出,通路1采样到的原信号Vi(Vip/Vin)与通路2转换输出的Vdac进行相减后经余量放大器放大输出得到该子级电路的余量输出Vo。

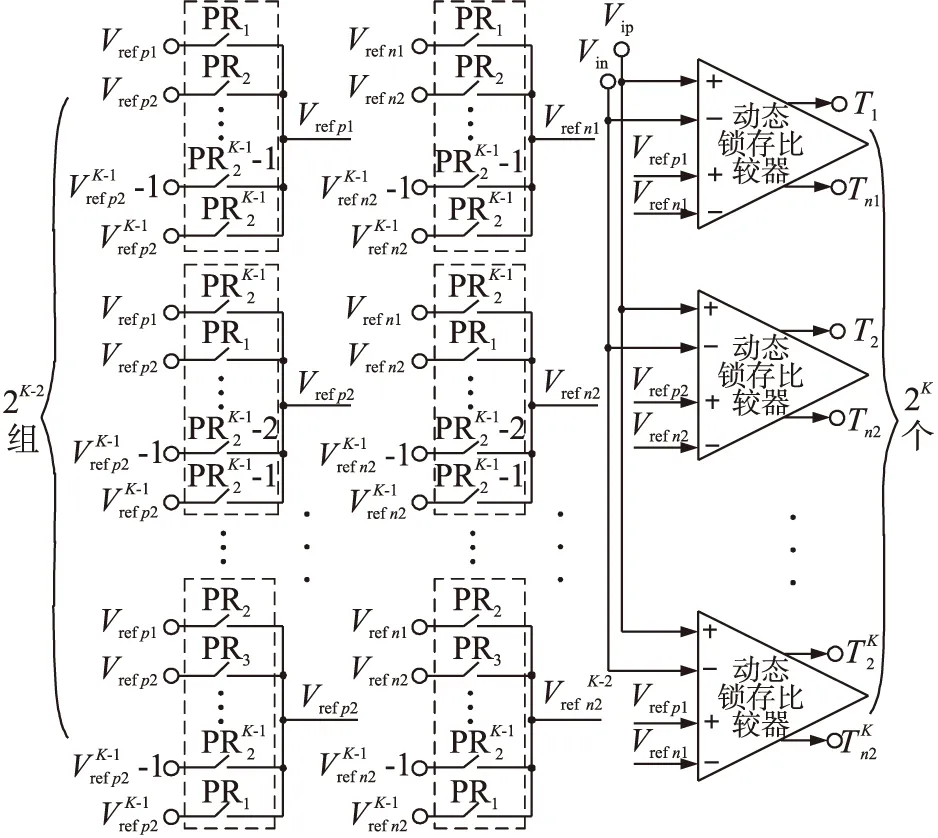

1.1伪随机序列调制子ADC电路

图2 伪随机序列调制子ADC电路结构图

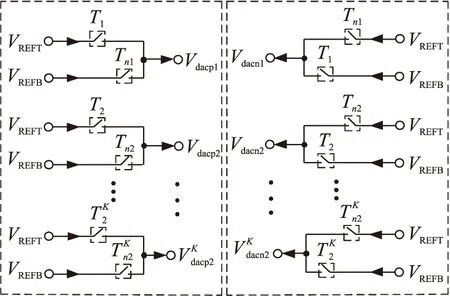

1.2子DAC电路

图3 子DAC电路原理图

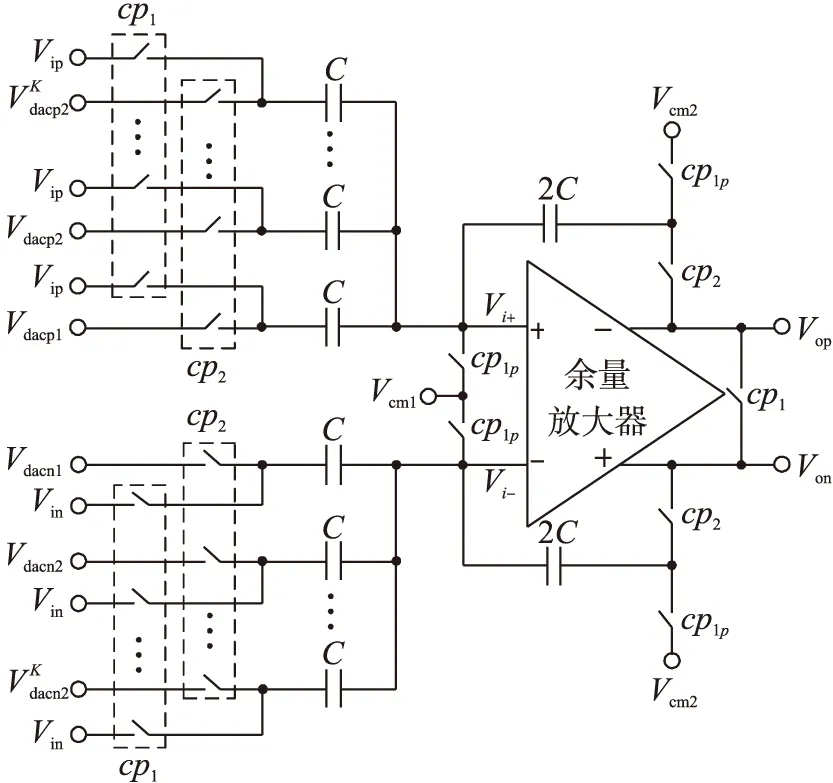

1.3余量增益电路

图4所示为余量增益电路原理图,该余量增益电路采用传统的电路架构,该电路工作在两相不交叠时钟cp1、cp2下,cp1p是比cp1稍提前的时钟。①在采样阶段:cp1、cp1p为高,cp2为低,采样电容对Vip进行采样,余量放大器处于复位状态,对于P端(正端)有:

Qp=2KC·(Vip-Vcmi)+2C·(Vcm2-Vcm1)

(1)

对于N端(负端)有:

Qn=2KC·(Vin-Vcmi)+2C·(Vcm2-Vcm1)

(2)

图4 余量增益电路原理图

+2C(Vop-Vi+)

(3)

对于N端(负端)有:

(Vdacn2K-Vi-)]+2C(Von-Vi-)

(4)

2K(Vip-Vin)=[(Vdacp1-Vdacn1)+…+(Vdacp2K-

Vdacn2K)]+2K+1(Vi+-Vi-)+2(Vop-Von)

(5)

2K(Vip-Vin)=[x·Vref-(2K-x)·Vref]-2K+1(Vi+-

Vi-)+2(Vop-Von)

(6)

又设余量放大器的低频开环增益为A0,则有:

2K(Vop-Von)=-A0·(Vi+-Vi-)

(7)

设Vip-Vin=Vi,Vop-Von=Vo由式(6)、式(7)得:

(8)

从式(8)可以看出,余量放大器的有限低频增益A0会给余量输出带来增益误差,若A0>60dB,式(8)可以近似为:

Vo=2K-1·Vi+(2K-1-x)·Vref

(9)

2 电路仿真与测试

图5所示为一个12bit250Msample/s流水线ADC芯片主通道电路的照片,电路采用0.18μm1P5M1.8VCMOS工艺,本文设计的流水线ADC子级电路运用到该ADC电路的第1级4比特分辨率子电路中。

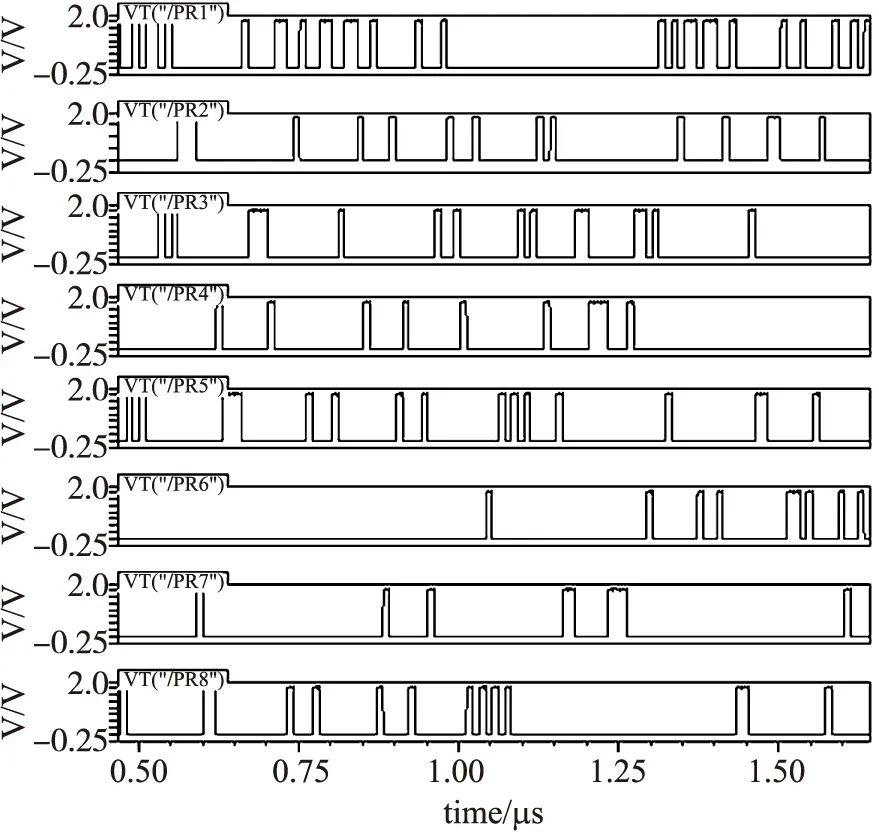

图6 伪随机码的产生

对于4比特的子级电路来说,子ADC电路的伪随机控制序列共有8组,图6所示为伪随机序列PR1~PR8的仿真波形,可知在任意时刻PR1~PR8中只有一个为高,且成随机分布,也意味着随机选通一组基准电压作为比较器阵列的参考比较电压,从而可以消除某个比较器因工艺制造带来的固有失调给子ADC的量化造成影响。

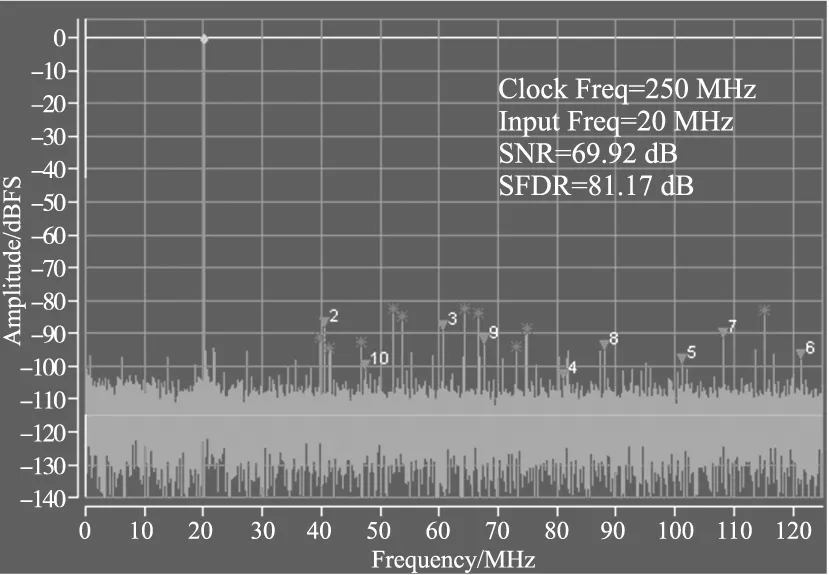

图7所示为运用了本文设计的子级电路的12 bit 250 Msample/s流水线ADC的FFT测试结果,输入为250 MHz正弦信号,峰峰值为2 V,幅度为0 dBm,测得SNR为69.92 dB,SFDR为81.17 dB。

图7 ADC的动态性能测试

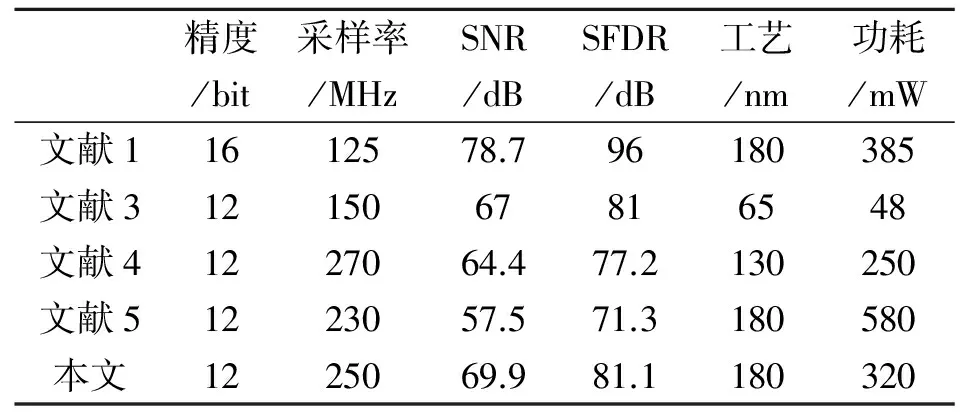

表1所示为部分参考文献与本文设计的流水线ADC间动态性能的对比,可以看出,本文设计的流水线ADC在250 MHz采样率下还能达较高的性能。

表1 本文与部分文献的参数对比

3 结论

设计一个对子ADC失调误差和电容失配误差进行动态补偿的流水线ADC子级电路,子ADC电路的比较器阵列的参考比较器电压受伪随机序列控制,比较器阵列间的高低位被随机分配,消除某个比较器的固有失调对子ADC电路量化的影响,具有伪随机性质的温度计码通过控制子DAC电路消除MDAC电容的失陪误差对余量输出的影响,提高了流水线ADC的动态性能。

参考文献:

[1]Devarjan S,singer L,Kelly D,et al.A 16-bit,125 Msample/s,385 mW,78.7 dB SNR CMOS Pipeline ADC.[J].IEEE J Sol Sta Circ,2009,44(12):3305-3313.

[2]Liu Ke,Yang Haigang.A CMOS Dynamic Comparator for Pipeline ADCs with Improved Speed/Power Ratio[J].半导体学报,2008,29(1):75-80.

[3]Peng Bei,Huang Guangzhong,Li Hao,et al.A 48-mW,12-bit,150-Msample/s Pipelined ADC with Digital Calibration in 65 nm CMOS[C]//IEEE Custom Integrated Circuitsc,San Jose,CA,USA.2011:1-4.

[4]Wang Xuan,Yang Changyi,Zhao Xiaoxiao,et al.A 12-bit,270 Msample/s Pipelined ADC with SHA-Eliminating front end.[C]//IEEE Int Circ and Syst,Seoul,Korea,2012:798-801.

[5]Lieghti T,Tajalli A,Akgun O C,et al.A 1.8 V 12-bit 230-Msample/s Pipeline ADC in 0.18 μm CMOS Technology[C]//IEEE Int Circ and Syst,Macao,China,2008:21-24.

[6]Grace C R,Hurst P J,Lewis S H.A 12 b 80-Msample/s Pipelined ADC with Bootstrapped Digital Calibration[C]//IEEE Int Sol-Sta Circ,San Francisco,CA,USA,2004:460-539.

[7]Wang Haoyue,Xiao Yue,Hurst P J,et al.Nested Digital Background Calibration of a 12-bit Pipelined ADC Without an Input SHA[J].IEEE Sol-Sta Circ,2009,44(10):2780-2789.

[8]Murmann B,Boser B E.A 12 b 75 MSs Pipelined ADC Using Open-Loop Residue Amplification[C]//IEEE Int Sol-Sta Circ,San Francisco,CA,USA,2003,pp:328-497.

戴强(1979-),男,汉族,江苏丹阳人,东南大学本科学历,工程师,现在中国电子科技集团第58研究所从事集成电路的研究工作;

薛颜(1983-),男,汉族,江苏邳州人,国防科技大学硕士学位,工程师,现在中国电子科技集团第58研究所从事集成电路的研究设计工作;

郭良权(1964-),男,汉族,江苏宜兴人,研究员高工,主要研究方向为微控制器以及数模混合集成电路设计。

ASub-StageCircuitwithComparatorOffsetandCapacitorMismatchesErrorsCompensatingforHighSpeedPipelinedADC

DAIQiang1,XUEYan1,YANGXiaolei1,ZHOUQicai1,2,WUJun1,GUOLiangquan1*

(1.No.58 Research Institute,China Electronic Technology Group Corporation,Wuxi Jiangsu 214035,China;2.IOT Engineering,Jiangnan University,Wuxi Jiangsu 214122,China)

Abstract:A sub-circuit for high-speed,high-resolution pipelined ADC is presented.Reference voltages in comparators array are controlled by pseudorandom sequences.MSBs and LSBs of comparators are assigned randomly,accordingly the effect of offset of some comparator on ADC quantization is eliminated.Pseudo-random thermometer code cancels the effect of the mismatches of MDAC capacitors on residue output.This circuit implemented in 0.18 μm 1P5M 1.8 V CMOS process is applied to a 12-bit 250 Msample/s pipelined ADC.Test results shows that the ADC has an SNR of 69.92dB and an SFDR of 81.17 dB

Key words:pipelined analog-to-digital converter;pseudo-random sequence;offset voltage;mismatches of capacitor

doi:EEACC:0170L10.3969/j.issn.1005-9490.2014.05.003

中图分类号:TN405

文献标识码:A

文章编号:1005-9490(2014)05-0812-04

收稿日期:2013-10-09修改日期:2013-10-26