基于SIXS-ASIC的半导体传感器信号读出电子学系统的研制

徐英姿,余庆龙,梁金宝,荆 涛,孙 莹

(1.中国科学院 国家空间科学中心,北京 100190;2.中国科学院研究生院 北京 100049)

基于SIXS-ASIC的半导体传感器信号读出电子学系统的研制

徐英姿1,2,余庆龙1,梁金宝1,荆 涛1,孙 莹1

(1.中国科学院 国家空间科学中心,北京 100190;2.中国科学院研究生院 北京 100049)

介绍了一种用于半导体传感器信号读出的专用集成电路(ASIC,Application -Specific Integrated Circuit)的基本结构和工作原理,分析其测试需求,设计并实现了基于该ASIC芯片的探测器读出电子学系统。描述了测试系统的主要硬件电路设计以及对该芯片的控制流程,上位机通过USB与该电子学系统进行双向通讯,并利用FPGA对该ASIC芯片进行时序控制以及数据采集。最后,对测试系统进行功能测试,采用信号发生器给系统注入模拟不同沉积能量的半导体传感器信号,得到能谱图及相应的线性响应曲线。最后,分别用放射源90Sr/90Y和207Bi对该电子学系统进行性能测试,得出各自的能谱图。

ASIC芯片;测试系统;FPGA;信号读出

随着半导体技术的迅速发展,很多新型的半导体探测器,如硅条探测器、二维像素探测器、SDD等,得到了快速发展[1],并逐步应用到空间辐射环境监测中,为卫星运行提供了安全保障。这些新型探测器大部分都具有读出密度高、通道数多等特点,传统的基于分离元件组成的电子学系统已经很难满足这些要求,因此具有功耗小、集成度高的ASIC芯片正慢慢取代传统电子学系统,被广泛应用于半导体传感器信号读出电子学中[2-3]。

SIXS-ASIC是RAL为欧空局的SIXS[4](SIXS,The Solar Intensity X-ray and particle Spectrometer)项目研发的一款传感器信号读出ASIC芯片。本文基于该ASIC芯片,研制了一套半导体传感器信号读出电子学系统,并对该系统进行了详细测试。

1 SIXS-ASIC芯片概述

SIXS-ASIC采用0.35μm CMOS工艺,如图1所示,其内部集成了8个互相独立的传感器信号处理通道,其中6个Si半导体传感器信号处理通道,2个碘化铯(CsI)闪烁探测器信号处理通道。每个通道包含电荷灵敏前置放大器,CR-RC滤波成形电路,峰值保持电路,阈值设置及阈值比较电路。8个通道通过多路选通器,共用一个ADC进行信号峰值采集。SIXS-ASIC还设计了一个串行配置接口,可方便设置内部各工作点的偏置电压、电流,比较阈值,以及ADC等相应参数。SIXS-ASIC的相关参数如表1所示。

图1 SIXS-ASIC结构框图Fig.1 Block diagram of SIXS-ASIC

表1 SIXS-ASIC主要性能参数Tab.1 The main performance parameters of SIXS-ASIC

整个ASIC内部的地被严格的分为数字地和模拟地,从而降低了系统的噪声。而且,其内部的数字逻辑都采用了三模冗余逻辑触发器,这样可以有效避免单粒子翻转(SEU,Single Event Upset)事件的发生。以上这个优势使得这款ASIC可以很好的适应于SEU高发的空间粒子探测领域。

2 测试系统的研制

测试系统的主要目的是通过FPGA给SIXS-ASIC芯片提供控制信息并且进行适当的配置,再接收ASIC芯片发出的科学数据,并对接收到的数据进行处理,最后上传至上位机。本节主要介绍了测试系统的整体电路设计、主要模块的实现方法及SIXS-ASIC芯片的工作流程。

2.1 测试系统的整体电路设计

2.1.1 电路整体框架

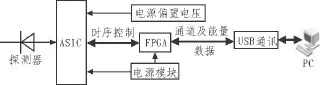

基于该芯片的信号电子学读出性能测试系统有4个主要模块:电源模块(高压和供电),FPGA模块,ASIC模块,USB通讯模块。如图2所示。

图2 SIXS-ASIC测试系统结构框图Fig.2 Block diagram of SIXS-ASIC test system

其中,电源模块主要用于给传感器提供高压和给整个系统供电。USB通讯模块实现了上位机和FPGA之间的双向通讯,可以简单通过PC端对整个系统进行实时控制,也可以接收到系统输出的科学数据。

2.1.2 系统运作流程

ASIC芯片接收探测器输出的模拟信号,该信号在ASIC内部经过相应的信号处理(见图1),最终由片内的ADC将模拟信号转成数字信号传送到FPGA控制单元。FPGA接收和处理由ASIC芯片发送出来的科学数据,将接收到的能量的数据以及通道的数据进行整合,简单处理后存入FPGA内部的RAM中。最后由PC端发送出控制信息,利用FPGA将采集的数据通过串口转USB接口发送给PC端的界面程序进行处理并实时显示,得到能谱图和科学数据[5]。同时也可以将PC端的控制数据通过USB通讯模块传到FPGA,通过FPGA实现对ASIC的实时控制。

2.1.3 系统数据RAM存储

在FPGA对科学数据进行存储的过程中,由于测试系统对信息实时存储的要求较高,因此采取乒乓存储数据的方法来存储数据,原理如图3所示。乒乓存储的处理流程[6]为:输入数据流通过输入数据选择单元将数据流等时分配到两个数据缓冲区,数据缓冲模块选择双口RAM。第一个周期,将输入的数据流缓存到数据存储单元A;第二个周期,通过输入数据选择单元切换,将输入的数据流缓存到数据存储单元B,同时将数据存储单元A的缓存的第一个周期数据通过输出数据选择单元的选择,输送到数据处理单元即上位机读取,再进行处理,如此循环。

图3 乒乓存储Fig.3 Ping-pong storage

实际运用中,采用FPGA内部中的IP核——RAM核,选择2块双端口RAM。其中一块存储单元读取数据的时候,另外一块存储单元进行写入数据的操作。这样系统可以同时进行读写操作,效率更高,使用方便。而且还可以避免板级间的干扰,既节省印制板空间又节约成本。

2.2 测试系统的数据采集和PC端显示

PC端对系统数据的获取直接通过USB模块实现,图4是在Lab View 8.6平台下开发的数据获取软件界面,这是整个系统人机交换的界面。其可实现以下4项基本功能:在界面直接更改ASIC的96位配置数据流,修改ASIC的工作参数来达到对ASIC做初始化配置或根据要求做重配置的目的;更改从FPGA内部RAM中接收科学数据的频率;接收FPGA发送过来的数据并解包,得出每个通道对应的科学数据,显示于图4中并进行实时存储;将数据进行简单的处理,画出其能谱图。

3 测试结果及分析

3.1 ASIC芯片测试系统的线性度测量

3.1.1 线性度测量原理

对测试系统进行功能测试,使用信号发生器产生下降沿跳变脉冲信号,该脉冲信号经电容微分后可用来模拟物理实验探测器的输出信号。测试脉冲经过0.6 pF的输入电容交流耦合到ASIC的输入端,由此来测试该传感器信号读出电子系统的线性度,其等效电路图如图5所示。

图4 PC端控制软件界面Fig.4 The control software interface of PC

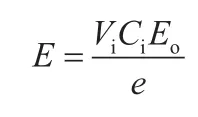

可以得出,信号发生器的输入幅值与其等效能量E的关系,表达式为:

图5 信号发生器连接信号电子学等效电路图Fig.5 Equivalent circuit schematic of signal generator connected to signal electronics

其中,Vi为信号发生器的输入信号电压,Ci为耦合电容,E0为硅半导体传感器平均电离能,E0=3.6 eV,e为电荷常量,e=1.6×10-19C。

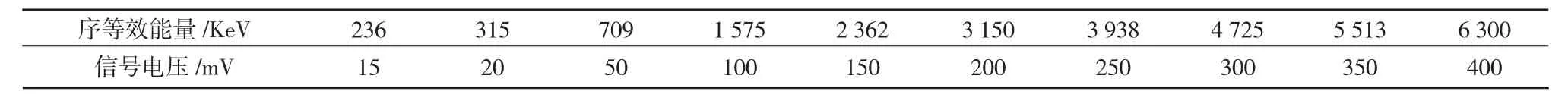

由上面公式,可以得出信号发生器输入信号幅值与半导体传感器粒子沉积能量的近似等效关系,表2列出了部分输入信号幅值及其对应的等效能量。

表2 输入信号电压与对应等效能量Tab.2 Voltage of input signal and equivalent energy

3.1.2 线性度测量结果

将信号发生器产生的信号的频率调为固定值1 kHz,幅值为15~460 mV,步进长度为5 mV。利用这种方式对ASIC的8个通道依次进行测试,得出每个通道对应幅值的科学数据。

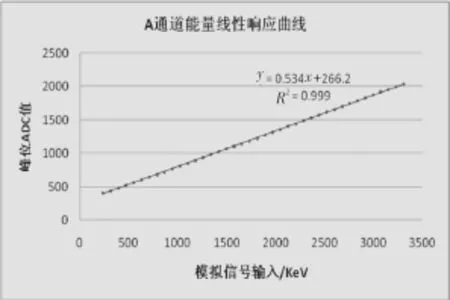

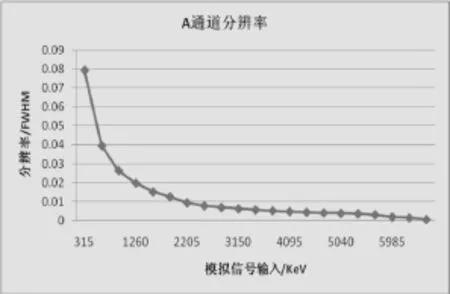

图6是A通道输出幅值与模拟信号输入的线性拟合曲线,图7是该通道分辨率与模拟信号输入的拟合曲线。从图6的曲线图可以看出,ASIC能量响应线性拟合值R2≥0.99,说明输入信号从15~460 mV(即能量值为236~7 000 KeV)间,系统都有很理想的线性度。从图7中可以得出,ASIC采集到的能谱分辨率均好于7.9%。而且,由测试结果可知,ASIC的8个通道都很独立,没有串扰。

图6 A通道输出幅值与模拟信号输入的线性拟合曲线Fig.6 Linear regression curve of A channel output amplitude and analog signal input

3.2 放射源下的能谱测量

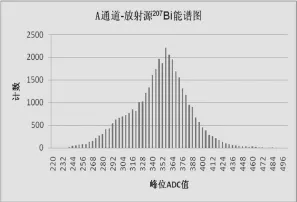

将完整的测试系统接上50 V的高压电源,并将其中一个输入端与探测器相连,分别使用放射源90Sr/90Y和207Bi对该信号读出测试系统进行放射源实验,由此得到能谱图。从图8中可以看出,对放射源207Bi,能得到很漂亮的全能峰能谱图,分辨率等于13.48%@168.16KeV。而对于放射源90Sr/90Y下的射线,测试系统得不到其全能峰能谱图。

图7 A通道的分辨率与输入信号的拟合曲线Fig.7 Fitting curve of the resolution and the input signal of A channel

图8 放射源207Bi下A通道获得的能谱Fig.8 The spectrum under radioactive sources 207Bi of A channel

4 结 论

由上述结论可知,基于SXIS-ASIC所研制的半导体传感器读出电子学系统,对在236 KeV到7 000 KeV间的能量值,都有非常理想的线性响应度。经测试,在放射源207Bi下,其能得到很漂亮的全能峰能谱图,分辨率约等于13.48%@168.16 KeV。而且,该测试系统能很方便的对SIXS-ASIC进行配置,极大的方便了操作。

[1] 孟祥承.新型半导体探测器发展和应用[J].核电子学与探测技术,2004,24(1):87-96.

MENG Xiang-cheng,Development and application of new semiconducting detector[J].Nuclear Electronics & Detection Technology,2004,24(1):87-96.

[2] 千奕.硅条传感器信号ASIC 芯片测试系统电路设计[J].核技术,2008,31(3):229-232.

QIAN Yi.A testing system circuit for front-end ASIC of silicon strip detector[J].Nuclear Techniques,2008,31(3):229 - 232.

[3] 程泽浩.基于ASIC的Si- PIN 探测器读出系统[J].核电子学与探测技术.2009,29(1):186-189.

CHENG Ze-hao.A Si-PIN readout system based on ASIC[J].Nuclear Electronics&Detection Technology,2009,29(1):186-189.

[4] Huovelin J.Solar Intensity X-ray and particle Spectrometer(SIXS)[J].Planetary and Space Science,2010(58):96-107.

[5] 余庆龙.HXMT高能电子学测试系统的研制[J].核电子学与探测技术,2010,30(8):1003-1007.

YU Qing-long.Development of the test system for ES /HE of HXMT[J].Nuclear Instruments and Methods in Physics Research,2010,30(8):1003-1007.

[6] 钱黄生.基于FPGA双RAM乒乓操作的数据存储系统的研究[J].科技信息,2010(21):93-96.

QIAN Huang-sheng.Research of data storage system based on dual RAM Ping-pong operation of FPGA [J].Science & Technology Information,2010(21):93-96.

Design of the system of semi-conductor detector readout electronic based on SIXS-ASIC

XU Ying-zi1,2,YU Qing-long1,LIANG Jin-bao1,JING Tao1,SUN Ying1

(1.National Space Science Center,China Academy of Sciences,Beijing 100190,China;2.Graduate School of the Chinese Academy of Sciences,Beijing 100049,China)

This article introduced the basic structure and principal of an ASIC chip for front-end readout of semiconductor detector and analyzed its test requirements,and a testing system for the detector readout electronics based on the ASIC chip was designed and implemented. The main circuit,the control flow of the ASIC chip,the realization of timing control for the chip and data acquisition based on FPGA,and the implementation of communication of the ASIC chip and PC by using the USB were introduced.The semiconductor sensor signal which was simulated in different depositional energy was injected into the system by using signal generator,and the energy spectrum and then the linear response curve was achieved.In the end,the testing results of the system under90Sr/90Y and207Bi radioactive source were given.

ASIC chip;test system;FPGA;front-end readout

TN4

A

1674-6236(2014)11-0054-03

2014-03-01 稿件编号:201403003

国家自然科学基金资助项目(Y32113BA9S)

徐英姿(1988—),女,湖南邵阳人,硕士。研究方向:空间环境中高能粒子探测。