基于FPGA的高功率脉冲电源控制系统设计

高 梁,李贞晓,栗保明

(南京理工大学 瞬态物理国家重点实验室,江苏 南京 210094)

基于FPGA的高功率脉冲电源控制系统设计

高 梁,李贞晓,栗保明

(南京理工大学 瞬态物理国家重点实验室,江苏 南京 210094)

针对高功率脉冲电源对电热化学炮负载的特殊需求以及现有控制器的不足,设计了一种基于现场可编程门阵列(FPGA)的Nios II嵌入式控制系统,从而有效调节脉冲电源的放电波形。采用自顶向下的模块化设计方法,通过VHDL语言设计了一种高性能控制器的IP核,并进行仿真验证。该控制系统能产生多路可调的脉冲触发信号,能较好地控制执行设备,其时序差可进行纳秒级调整,同时系统提升了可裁剪性、抗干扰能力和控制精度。仿真试验结果表明,系统工作可靠,精度得到提高,能够较好地满足系统在强电磁干扰下的运行要求。运用仪器仪表技术,简化了系统硬件组构,保证了系统控制的实时性,也为补偿脉冲发电机的测控提供了一种新方法。

高功率脉冲电源;电热化学炮; FPGA; 嵌入式

脉冲控制器是高功率脉冲电源系统的重要组成部分,其输出信号为多路具有时序差的触发信号,在补偿脉冲发电机、电磁电热发射中具有广泛应用[1-3]。它关系到系统整体运行的可靠性,是影响电热化学发射效率的重要因素之一[4]。传统工程应用主要基于51单片机、DSP、ARM等器件,再辅以必要的外围分立元器件构成。

国内外在时序控制方面开展了很多研究,如美国曾在电磁发射控制系统中运用PLC为控制器,其抗干扰能力强,可靠性高,但是所占体积较大,不利于小型化集成。文献[5]中运用现场可编程逻辑器件设计了一种控制器,抗干扰能力强,但其时序是通过外部拨码开关来实现的,不利于远程控制,其使用的CPLD器件不能使用嵌入式系统。文献[6]运用了DSP进行控制发射系统,其优点是人机交互界面良好,但其时序的生成仍然是对指令的逐句读取,并没有类似CPLD中的硬件电路结构。有学者使用可编程逻辑器件进行高压触发控制[7-12],但协处理器仍然使用传统单片机等,其存在的不足是系统集成度低、系统的抗干扰性差和控制精度低。

一方面,对于普通单片机而言,1 μs的时钟周期固然能满足时序要求,但由于触发过程中存在很大电磁干扰,往往导致控制系统误动作,极大地影响了安全,因此对控制系统可靠性、抗干扰能力、稳定性提出了很高的要求。

另一方面,随着电源系统设计容量的增加,电源模块数也增加很多,在不使用外部译码器的条件下,MCU的I/O口将不够使用,而增加外部器件必然使得抗干扰能力减小。

触发信号的时序差是由于光纤不等长、MCU离散性、MCU时钟频率共同导致的,但光纤不等长所引起的时序不同步约为几十纳秒,而误差主要是由MCU器件引起的。当用于对控制精度要求高的场合,如补偿脉冲发电机的放电试验中,控制精度就显得尤为重要。

针对上述问题,提出了一种基于FPGA的新型时序触发控制系统,根据现场可编程门阵列的特点进行功能划分,并对设计中的一些关键技术给出具体解决方法。利用FPGA高速并行处理的特性,通过硬件描述语言(VHDL)设计[13]通用时序脉冲控制器的IP核(Intellectual Property Core),实现对多路脉冲信号的高精度控制,同时再利用Nios II嵌入式软核处理器的多任务处理实现对时序数据、温度和端电压等的计算及显示,功能上融合了DSP和CPLD各自的优点。最后给出控制系统的性能测试结果,试验表明FPGA的实现方法可以使系统运行可视化、结构一体化。

1 系统总体设计与工作原理

1.1 系统设计思路和结构

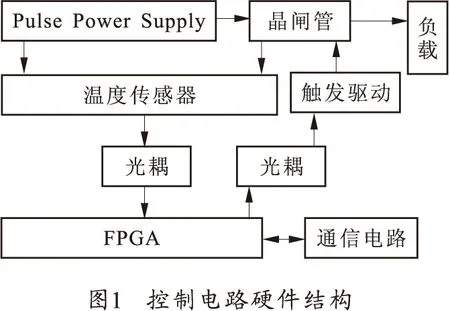

基于FPGA的控制板主要由信号捕获单元、光电转换单元、数据处理单元3部分组成。其系统框架如图1所示。

控制器(FPGA)采用Altera公司的EP2C35芯片,以64 M的SDRAM作为扩展。需要完成以下主要基本功能:

1) 温度监测。DS18B20传感器用于检测模块(电容、放电电感或晶闸管等)温度是否超过阈值。

2) 时序脉冲信号产生。

3) 与上位机进行通信。点火信号的接收以及模块运行状况的上传。

4) 监测电压。电源模块的电压通过调理后发送给FPGA进行检测。

为实现系统10 ns的时序控制精度,利用FPGA在时序和逻辑上的特点,设计脉冲控制器的IP核。性能超过200 DMIPS的Nios II软核处理器嵌入于FPGA内[14],替代传统外围扩展的协处理器,其最大优势和特点是模块化的硬件结构,以及由此带来的灵活性和可裁减性。通过参数化的Avalon总线,可以将硬件系统(包括处理器、存储器、外设接口和用户逻辑电路)与常规软件集成在单一可编程器件中。

1.2 外部扩展电路结构

控制板的输入输出端均采用高速光耦进行隔离,串口通过光纤与上位机通信,接收外部发送的点火信号,同时还将模块运行状况实时传送回控制室的上位机。外部温度传感器用于检测模块是否过温,电容端的电压经调理后实时反馈给Nios II处理器。

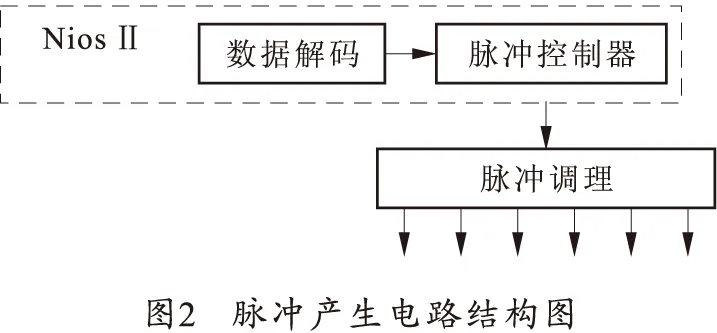

脉冲控制器的作用是产生触发晶闸管的控制信号,使电容所储能量及时输送到负载上。触发时刻的不同,将导致放电波形的不同,若对于时序触发,控制精度尤为重要。触发单元主要由初级触发形成电路、信号放大电路两部分组成,其工作框图如图2所示。

通过VHDL设计脉冲控制器,较传统控制器件有更高的输出精度,延迟响应极小。Nios II从远程计算机获得数据,经解调后获得最原始的延迟数据并输出给脉冲控制器,最后按给定时序输出给各晶闸管触发电路。

2 FPGA功能设计

2.1 计时器模块设计

在FPGA中设计1个32位计数器,外部时钟采用50 MHz晶振,计数器则利用PLL(Phase Locked Loop)倍频出所需要的时钟频率。Nios II处理器将所接收的各脉冲电源模块间的延迟信号转换成二进制代码输出给脉冲控制器。通过对PLL输出信号上升沿的计数,来控制各电源模块的放电时序。

2.2 消抖模块设计

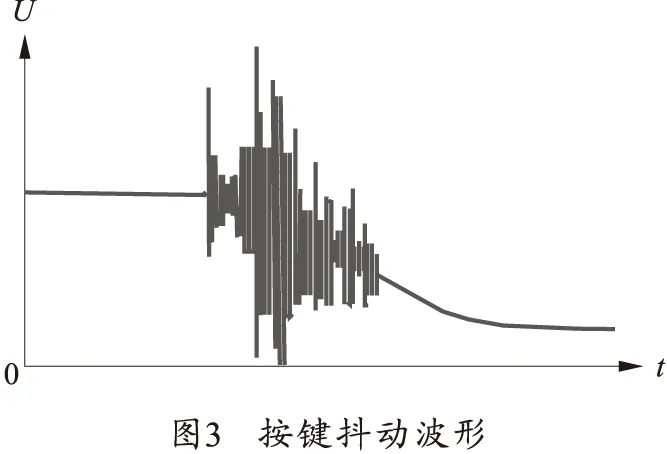

由于时序的精确控制对毫秒级脉冲放电至关重要,因此不仅要消除控制器在电路结构上的竞争冒险现象,更要解决电路上的误触发问题。点火按钮触发时电源模块开始向负载放电,因此必须考虑误触发的现象,当按钮动作时会产生如图3所示的抖动信号。

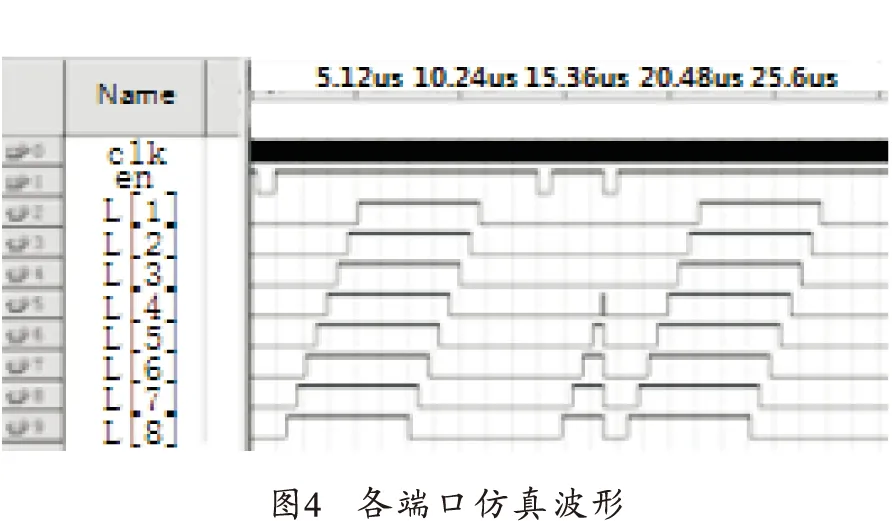

这可能会导致脉冲信号控制器的使能端口En多次变化。每当该控制信号变化一次时,系统触发一次。仿真测试采用2 s等间隔触发各路模块,图4是时序仿真效果图。

仿真时模拟1次抖动,从图4中可看出当按键抖动时,前次触发立刻终止,并且进行第2次触发,故设计按键消抖是十分必要的。抗抖动在硬件上的措施主要有两点:

1) 对前端按键输入端设计RS锁存器。

2) 对按键信号进行延时输入。当计数值未达到阈值时,输出始终为0。

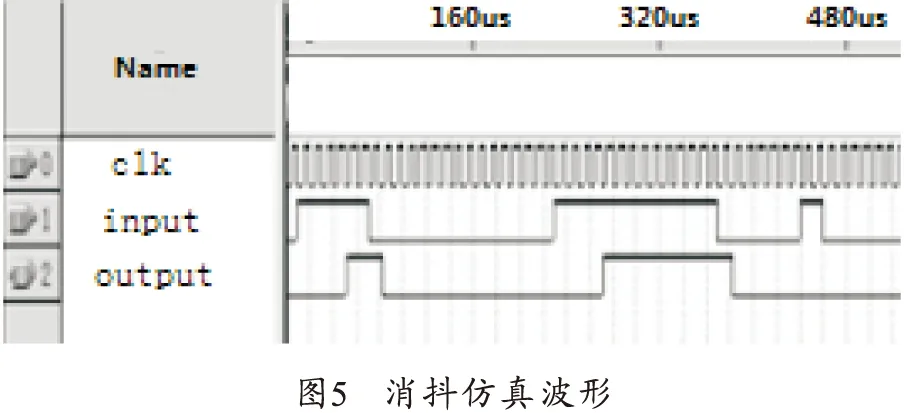

RS锁存器能使En信号在切换时能够可靠保证输出状态,图5是消抖电路处理后的信号仿真示意图,通过两种硬件消抖方式结合,确保不会误触发。

2.3 SOPC软件系统设计

系统软件基于Nios II IDE为平台所开发,利用其所提供的硬件抽象层(HAL)的函数支持,以C语言编写而成。系统上电初始化后进入等待状态,接收用户数据输入。Nios II将数据解码转换后输入给脉冲控制器。触发信号的时序控制部分由脉冲控制器单独完成,检测到点火信号后,Nios II将点火信号转送给脉冲控制器,从而完成发射操作。期间若发生晶闸管升温过高等现象,Nios II会向上位机发送警告。整个系统主要功能模块包括:

1) Nios II软核。Nios II处理器是Altera公司的第2代用户可配置的通用32位RISC软核微处理器,它是基于通用FPGA架构的软CPU内核,有完整的32位指令集、数据总线和地址空间,具有超过200 DMIPS的性能。同时该处理器内核具有3种类型来满足不同设计要求,快速型Nios II内核具有最高的性能,本控制系统是基于该类型而设计的。

2) Avalon总线接口。Avalon总线是一种开放标准,每个时钟周期可进行一次传输,各控制器以及Nios II处理器均通过Avalon总线进行寄存器读写操作。

3) CAN控制器。该控制器用于FPGA与电容模块的终端触发设备间的通信,支持CAN 2.0B协议。

4) 串口控制器。UART核是SOPC的集成模块,它提供一个到内部寄存器文件的Avalon从接口。串口通过光纤与上位机通信,接收外部发送的点火信号,同时还将电源模块运行状况实时传送回控制室上位机。

5) 脉冲控制器。由上节所设计的多路脉冲控制器用于产生控制各路触发设备的使能信号,它是独立的硬件电路,其时基信号由片内PLL提供。时序间隔由Nios II提供,其优点是通用性强,可应用于多种高速发射的控制当中。

6) 存储控制器。SDRAM用于软件运行和数据的缓存,而EPCS系列存储器用于存储FPGA配置信息和整体软件代码。这两种控制器都包含在SOPC中,很容易集成到控制系统中。

7) 要构成完整的Nios II系统,还需要用到定时器IP核、JTAG UART IP核、PLL模块和GPIO IP核。

3 系统可靠性设计

由于电源模块工作条件恶劣,加之内外部电磁环境错综复杂,因此为了保证其可靠运行,必须考虑电磁兼容和抗干扰设计。抗干扰在硬件上的措施主要有两点:

1) 电磁屏蔽外部干扰以阻断其影响自身系统。

2) 降低控制系统自身的电磁敏感性。

3.1 控制板抗干扰设计

PCB的电磁兼容设计重点是接口处理、接地处理和时钟处理。接地设计的原则是尽量让每根信号线都有最小的回流路径。时钟信号的处理原则是远离干扰源,时钟线尽可能短,与其他线间距至少满足3W原则(即两根走线的间距必须大于单一走线宽度的2倍)。在电源端口采用铁氧体磁珠、共模电感等有效滤波器件来抑制干扰[14]。

3.2 网络端口间抗干扰设计

控制箱体的接缝、开口等都是电磁波的泄漏途径,穿过机箱的电缆也是造成箱体屏蔽效能下降的原因,解决方法是在缝隙处使用电磁密封衬垫,同时对于箱体的通信线路全部使用光电隔离,阻断干扰信号串扰[15]。

4 调试与验证

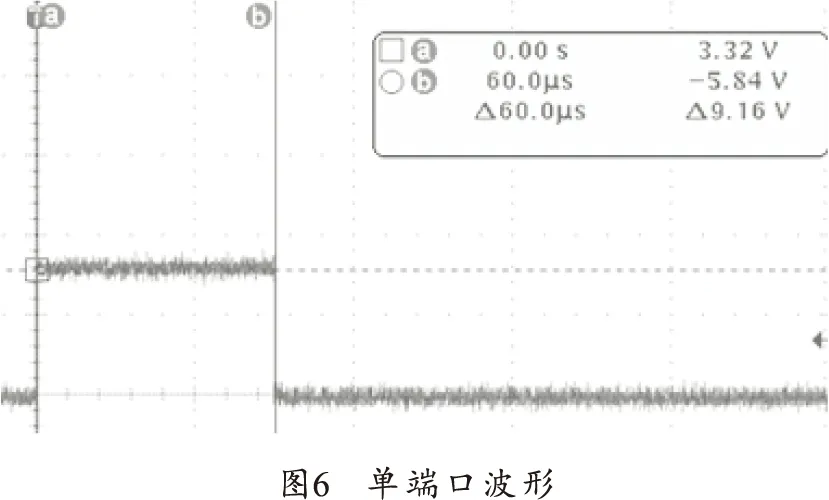

用示波器对单个输出端口进行触发扫描,采用5 MHz外部时钟。在此条件下各端口导通时间应为60 μs(300个时钟周期),示波器测试获得的数据如图6所示,其高电平持续时间约为60 μs,满足试验需要。

通过示波器检测,每个端口输出信号间隔也符合设计要求。电压幅值均为3.3 V。

触发信号与光纤隔离后的驱动信号相比,两路信号的脉宽不同步时间在2 ns左右,这是由于器件性能的离散性造成的。

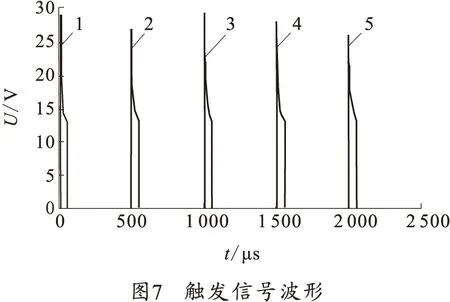

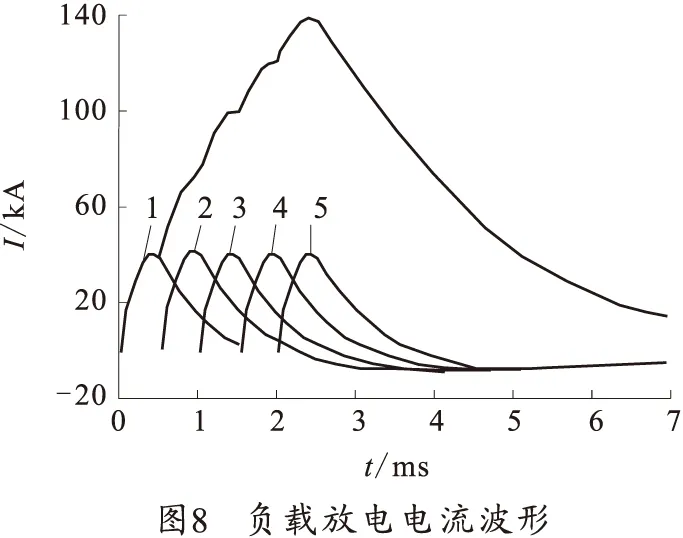

为了测试控制系统对多路信号的驱动性能,采用1.4 mF脉冲电容器、80 μH调波电感器、大功率电力晶闸管等搭建5路试验平台进行试验验证,电容初始电压UC=10.0 kV,测试采用等时序间隔进行触发驱动,时序间隔有5、50、500 μs等典型值。控制系统的板载外部时钟为50 MHz,PLL倍频一路100 MHz时钟给脉冲控制器,此时FPGA中的时序控制器最高控制精度为10 ns,晶闸管门极触发信号由控制系统发出并经过调理。500 μs时触发信号的波形如图7所示,对应的5路电源模块放电电流时序波形如图8所示,试验结果和预设值吻合较好。

5 结论

充分利用FPGA的特点,对时间控制精度要求较高的部分设计成硬件电路,又利用Nios II软核处理器强大的数据处理能力、实时控制能力和系统的可裁剪性,实现通信、数显和电路保护等。软硬件结合的方式使得控制系统更精简、可靠。所开发的控制器IP核通过充分的软硬件仿真与试验测试,可以移植到不同工艺的FPGA平台中。同时对控制箱体和控制板采用多重电磁屏蔽措施,以增强系统整体抗干扰性能。由于FPGA的可扩展性强,该控制系统也可应用于线圈炮和脉冲发电机的触发和控制中。

References)

[1]刘福才,赵晓娟,何锁纯.基于DSP的PFN触发时序控制系统设计及实验分析[J].高电压技术,2013,39(7):1778-1783. LIU Fucai,ZHAO Xiaojuan,HE Suochun.Design and experimental analysis of DSP based PFN trigger timing control system[J].High Voltage Engineering,2013,39(7):1778-1783.(in Chinese)

[2]张荣,黄海莹,李春枝,等.基于NIOS II处理器的多通道ns级时序控制同步机设计[J].计算机测量与控制, 2012,20(11):2968-2971. ZHANG Rong,HUANG Haiying,LI Chunzhi,et al.Designing techniques of multi-channel ns-level timing control synchronous machine based on NIOS II processor[J].Computer Measurement & Control,2012,20(11):2968-2971.(in Chinese)

[3]王鹏,吕志刚,杜卫东.基于FPGA与ARM的多路时序控制系统设计与实现[J].计算机测量与控制,2012,20(6):1540-1543. WANG Peng,LYU Zhigang,DU Weidong.Design and implementation of multi-channel timing control system based on FPGA and ARM[J].Computer Measurement & Control,2012,20(6):1540-1543. (in Chinese)

[4]王莹,肖峰.电炮原理[M].北京:国防工业出版社,1995:192-197. WANG Ying,XIAO Feng. The principle of electrical magnetic gun[M].Beijing:National Defense Industry Press,1995:192-197.(in Chinese)

[5]石晓晶,董建年.用于电磁发射试验的时序控制电路设计[J].仪器仪表学报,2004,25(4):969-970. SHI Xiaojing,Dong Jiannian.Design of firing control for ET experiment[J].Chinese Journal of Scientific Instrument,2004,25(4):969-970.(in Chinese)

[6]黄海,高俊山,李文龙.电磁发射器DSP控制系统的设计[J].自动化技术与应用,2007,26(3):92-95. HUANG Hai,GAO Junshan,LI Wenlong.DSP based control of the electromagnetic launcher[J].Techniques of Automation and Applications,2007,26(3):92-95.(in Chinese)

[7]潘圣民,傅鹏,蒋力,等.采用DSP和CPLD的100 kV高压脉冲电源控制系统[J].高电压技术,2009,35(7):1667-1671. PAN Shengmin,FU Peng,JIANG Li,et al.Control system of 100 kV high voltage pulse source using DSP and CPLD[J].High Voltage Engineering,2009,35(7):1667-1671.(in Chinese)

[8]刘超,尚雷,郭亮,等.采用FPGA 的多路高压IGBT驱动触发器研制[J].高电压技术,2009,35(2):350-354. LIU Chao,SHANG Lei,GUO Liang,et al.Development of the multi-channel HV IGBT driver trigger based on FPGA[J].High Voltage Engineering,2009,35(2):350-354.(in Chinese)

[9]陈文光,饶军,饶益花,等.采用FPGA控制的IGBT串联高压调制器的研制[J].高电压技术,2010,36(11):2827-2832. CHEN Wenguang,RAO Jun,RAO Yihua,et al.Deve-lopment of the IGBT series high voltage modulator using FPGA controlled[J].High Voltage Engineering,2010,36(11):2827-2832. (in Chinese)

[10]郝统关,程明.基于FPGA Nios II的等精度频率计设计[J].电测与仪表,2009,46(518):56-58. HAO Tongguan,CHENG Ming. Design of equal precision frequency meter based on FPGA Nios II[J].Electrical Measurement & Instrumentation,2009,46(518):56-58.(in Chinese)

[11]杨玉东,王建新.脉冲成型网络对轨道炮发射效率的影响[J].火炮发射与控制学报,2011(4):41-45. YANG Yudong,WANG Jianxin.Influence of pulse forming network on rail gun launching efficiency[J]. Journal of Gun Launch & Control,2011(4):41-45.(in Chinese)

[12]姚陈果,章锡明. 基于现场可编程门阵列的全固态高压ns脉冲发生器[J].高电压技术,2012,38(4):929-934. YAO Chenguo,ZHANG Ximing.All solid state high voltage nanosecond pulse generator based on FPGA[J].High Voltage Engineering,2012,38(4): 929-934.(in Chinese)

[13]VOLNEI A PEDRONI.Circuit design with VHDL[M].Cambridge:Massachusetts Institute of Techno-logy Press,2004:209-224.

[14]李兰英.Nios II嵌入式软核SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006:35-53. LI Lanying. Principle of design and application of Nios II embedded core[M].Beijing:Beihang University Press,2006:35-53.(in Chinese)

[15]张志刚,林福昌,王少荣,等.强激光脉冲电源控制装置的电磁兼容设计[J].高电压技术,2007,33(3):132-135. ZHANG Zhigang,LIN Fuchang,WANG Shaorong,et al.Electromagnetic compatibility design of remote control device for a pulsed supply of high power laser[J].High Voltage Engineering,2007,33(3):132-135.(in Chinese)

ControlSystemDesignBasedonFPGAinHighPulsedPowerSupply

GAO Liang,LI Zhenxiao,LI Baoming

(National Key Laboratory of Transient Physics,Nanjing University of Science and Technology,Nanjing 210094, Jiangsu,China)

In order to meet special requirements of the high pulsed power supply for the ETC load and to make up the shortages of the existing controllers,FPGA was used to design a kind of Nios II embedded control system so as to effectively regulate the current waveform of the pulse power. A type of IP core of high performance controller described by means of VHDL language was presented, and it was accomplished with the help of the top-down modularized method,as well as the simulation and the verification of the IP core were carried out. This control system can generate multichannel and variable signals to trigger the next executive circuit,the signal can be adjusted at nanosecond. This system can also improve the quality and scalability,anti-interference ability and control precision. Simulation results showed that the system can greatly improve the accuracy,meet the requirements under the condition of strong electromagnetic interference. This system can simplify the hardware structure by use of instrument technology,and guarantee the real time capability of the control system, it can also provide a new kind of method for the measurement and control of compensated pulsing alternator.

high pulsed power supply;electro-thermal chemical gun; FPGA;embedded

2014-04-11;

2014-05-12

国家高技术研究发展计划(863计划)(2013AA8091002A)

高 梁(1986-),男,博士研究生,主要从事补偿脉冲发电机技术研究。E-mail:quantumlab@163.com

TP271+

A

1673-6524(2014)04-0025-06