流水线型ADC数字校正电路设计

龚 骏

(哈尔滨工业大学,黑龙江 哈尔滨 150006)

1 课题来源及研究的目的和意义

1.1 课题来源

医用、商用以及军用的数模混合电子系统中的模数转换器(ADC,Analog to Digital Converter)。

图1 ADC 在数字信号处理中的应用

1.2 研究的目的和意义

自然界中的原始信号大都为模拟信号,传统方法是利用模拟电路处理这些连续的信号。随着电子科技的迅猛发展,在许多领域中,传统的模拟电路逐渐被速度快、成本低、鲁棒性好的数字电路所取代。 近些年来,随着集成电路(IC,Integrated Circuit)工艺的迅猛发展, 全球高新科技领域的数字化程度正在不断加深。 作为连接数字域和模拟域两大桥梁之一的模数转(ADC,Analog to Digital Converter)已经成为了许多电路系统的重要组成部分,广泛地应用于各种医用、商用以及军用的数模混合电子系统中。

随着对ADC 需求与日剧增的同时, 人们对其性能的要求也在不断地提高。如今在很多电路系统设计中,ADC 已经成为制约系统工作频率的瓶颈[1]。 因此,高速度高精度ADC 的实现已成为了时下研究的热点。

然而,在实际的ADC 设计中,由于受到芯片成本、面积、功耗和工艺等诸多方面因素的制约, 高速度和高精度往往是相互对立的。 高分辨率的ADC 很难做到高转换速率,而高转换速率的ADC 很难做到高分辨率和低功耗。 例如:Sigma delta ADC 的分辨率能够达到24 位,是目前为止精度最高的ADC,但是速度只能接近最初流水线型ADC 的1.5MS/s 的速度; 速度最快的ADC 无疑是全并行的Flash ADC,速度可以达到GS/s 级,但是在这种速度下,分辨率却普遍低于8 位;而流水线型ADC 在分辨率为15 位时转换速度仍可以超过200MS/s[2]。相对于其他类型结构的ADC,流水线型ADC(Pipelined ADC)在实现较高精度的同时,仍可以保持较高的速度和较低的功耗,可以在速度、精度、功耗和芯片面积之间达到最好的折中[3]。 流水线型ADC 可以提供优异的动态性能,能够满足现代数字无线通信系统、高精度成像系统、 高速数据采集系统等对A/D 转换器高速度、 高精度的要求。因此应用范围十分广泛,已经成为各种模数转换结构中的主流,自然也是近几年国内外研究的热点。

在现行的工艺水平下,由于受到热燥声、时钟抖动、开关电荷注入、时钟馈通、比较器失调、运放有限增益以及电容失配等诸多方面因素的影响,流水线型ADC 的转换精度一般被限制在10 位左右[4]。 因此,为了满足更高的精度需求,就必需使用相关的误差校正技术。 数字后台校正技术可以突破芯片工艺条件和电路设计水平的限制,而且流水线型ADC 的结构也易于采用数字后台校正技术。 使用数字后台校正技术也方便和后端数字信号处理电路在同一芯片集成,是现在主流的校正技术[5]。

2 国内外在该方向的研究现状及分析

经过三十多年来的行业和学术研究上的发展,ADC 的研发与设计已逐渐成熟。 自从1999年来,国外的ADC 发展速度异常迅猛。 国外诸如MIT、U.C.Berkeley 等大学和知名研究机构有大批研究人员从事各种ADC 的研发工作, 目标主要集中在新型ADC、系统结构、单元电路和具体技术难点的突破。 此外在工业界,ADI、TI、Linear、Maxim、NXP 等 国 际 知 名 公 司 则 主 要 对 已 经证实为准确、可靠的A/D 转换技术,从设计、工艺、生产成本等各方面进行改进和完善。 重视工程化、实用化研究,从而让这些技术和产品尽快应用于新一代A/D 转换器、通信、DSP 系统等军用民用领域。

国内ADC 发展由于起步比较晚,主要是由复旦大学、清华大学、上海交通大学等高校科研机构在研究设计。 此外在工艺上国内该领域也与国外的工艺技术存在着很大的差距, 科研水平和技术水平都比较落后。 不过近几年来随着市场经济的不断发展,也为了能够逐步的满足国内市场对于ADC 的需求,无论是工业界还是在实验室中都加大了对ADC 的研究研究和投入,也取得了一定的成就[6]。

2.1 高速度

转换速度作为模数转换器的一个重要指标,为了能够满足高速的数字信号的处理要求,必须得到不断提高。 目前提高速度的方式一般是采用高速的ADC 结构,如采用全并行(Flash)模数转换技术、流水线型转换技术、时间交织模数转换技术。 现阶段流水线ADC 速度已突破200MS/s,Flash ADC 速度突破10GS/s,时间交织ADC 速度甚至达到了40GS/s,就连以分辨率为主要性能指标的sigma delta 型ADC 也突破了25MS/s 的速度[2]。 在未来的发展道路上,随着工艺技术的日益提高,更高速度的ADC 也不再遥不可及。

2.2 高分辨率

分辨率指的是图像能分辨的程度, 它是对精度的一种体现。 现代随着多媒体技术的高速发展,这就要求数字信号能够具有更大的动态范围, 随之而来的就是需要将模拟信号转化成数字信号的模数转换器有更高的精度, 即需要更多位数的有效分辨率。 目前国际上具有较高分辨率的结构有低中速率的sigma delta 型ADC、流水线型ADC 以及折叠插值型ADC。 其中过采样的Sigma-delta 型ADC 的分辨率达到了24 位以上。如TI 公司的ADS1258,其分辨率为24 位,它在音频设备上得到了广泛的应用[7]。

2.3 低电压、低功耗

ADC 的设计除了要求有高速度和高分辨率之外,一项重要的性能指标就是功耗。 低电压、低功耗是当今电子产业不可避免的发展要求,主要原因可以从两个方面进行考虑:第一、能够节约能源;第二、低电压能够通过电池供电来使用产品,还能够增加电池的使用时间,方便用户携带。 现在低功耗ADC 的功率已降到了几十毫瓦,使得智能手机、便携式音箱设备和医疗设备等成为可能[8]。

2.4 混合信号处理(Mixed Signal Processing)方向

在微电子行业领域技术的迅猛发展以及CMOS 超大规模集成电路(Very Large Scale Integration)技术水平的快速提高,把数字信号处理器及其他标准数字器件与ADC 集成于同一芯片上, 从而构成一个混合信号处理器是集成电路产业未来发展的趋势。这样做可以提高芯片的集成度,与此同时也降低了芯片在制造和封装过程工序的成本, 除此之外还能节省和减少外围电路,降低电路的功耗,提升芯片的运行效率。 这对于系统/设备生产商来说将意味着更短的开发周期、 更小的封装面积和更加稳定的产品性能[6]。

2.5 向CMOS 工艺发展

电路的设计是以工艺为基础建立的,同时电路结构的发展又促使工艺的提高,从而满足设计的需要,两者相互促进,相互依存。近年来由于集成电路制造工艺的不断演进,模拟电路也被不断地移植到深亚微米甚至纳米尺度的CMOS 工艺上去, 芯片封装面积也越来越小。 这样一来既可以提高产品的集成度,同时也降低了封装成本。 因而尝试将混合信号功能从昂贵、复杂的专业型工艺向主流的CMOS 型工艺转化是ADC 研发的另一个趋势[9]。

3 主要研究内容及研究方案

3.1 主要研究内容

首先,从研究数模转换器的电路结构出发,针对运算放大器的非理想性因素以及电容失配对误差因素的影响, 分析总结流水线型ADC 传统实现的设计约束。 在此之上研究并提出新的流水线型ADC 的数字校正方,在数字信号处理中对误差进行校正案,提高ADC 系统的性能,降低对模拟电路的性能要求,把电路复杂度从模拟领域转移到数字领域, 从而有效地降低系统功耗。 然后完成数字校正系统方案的建模,并进行行为级验证。

根据提出的数字校正方案进行电路结构的设计,并用硬件描述语言Verilog HDL 代码实现, 对生成的Verilog 代码进行功能仿真、时序分析等;待功能仿真正确无误之后,利用综合软件(Design Compile)结合工艺库文件进行综合。

3.2 研究方案

3.2.1 首先了解ADC 的基本工作原理

ADC 是模拟系统通向数字系统的接口,其工作是对输入的模拟信号进行采样,把这些采样值通过量化和编码,最后得到所需要的数字量。因为数字量的取值是离散的,而模拟量的取值是连续的,所以这种表示只能是近似的表示。 其工作框图如下图2所示。

图2 ADC 系统框图

抗混叠滤波器防止谐波或者高频信号折叠到基带上,得到理想的频率设计范围。 采样/保持电路在时钟电路控制下,将连续的输入信号变为固定时钟间隔的离散信号。 量化电路将经过采样/保持电路生成的离散信号进行幅值量化,从而转换成数字码。 编码电路将量化后的数字码转化成二进制码,方便后续的数字电路进行处理。

3.2.2 流水线型ADC 的基本工作原理

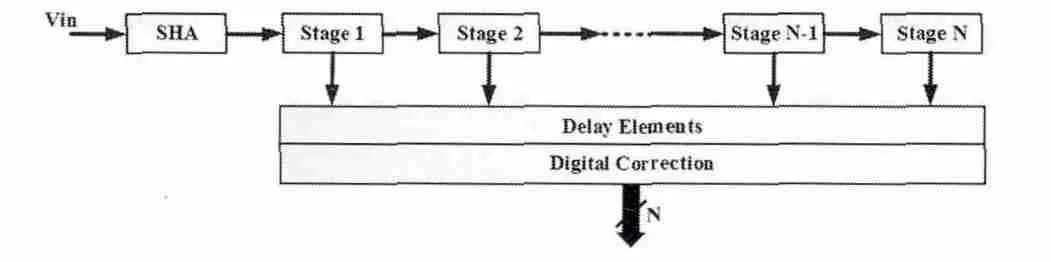

流水线型ADC 由前端采样保持电路 (SHA,Sample-Hold-Amplifier)、各级子流水线ADC、延时单元(Delay Elements)以及数字处理单元(Digital Correction)构成。 以下为其工作框图[10],如下图3 所示。

图3 流水线型ADC 系统结构框图

采样保持电路对输入的模拟信号进行处理,将处理后信号传输到子级流水线型ADC 中。 各级子流水线ADC 的结构基本相同,除最后一级之外,其余的每一级子流水线ADC 的输出分为两个部分:一部分输出到延迟对准寄存器中;另一部分作为下一子流水线ADC 电路的输入。 最后一级电路由于没有下一级子流水线ADC 电路,直接将结果输出到延迟对准寄存器中。 最后,将延迟对准寄存器中的数字码错位相加, 得到最终的数字输出码。

每一子流水线ADC 均包括采样保持电路模块(S/H)、高速低精度的子级模数转换器 (Sub ADC)和子级数模转换器(Sub DAC)、 减法器模块以及残差增益模块。 其中的采样保持模块、Sub DAC、 减法器模块和残差增益模块构成乘法型数模转换器(MDAC,Multiplying Digital-to-Analog Convertor)。 子流水线ADC的电路结构如下图4 所示。

图4 子级流水线ADC 结构框图

采样保持电路对输入的模拟信号Vin 进行采样, 同时Sub ADC 将输入Vin 转化为K 位数据输出。然后Sub DAC 将K 位数字信号还原成模拟信号, 再与被采样的输入信号相减得到残差信号。 将残差信号通过残差增益模块精确放大倍之后输出到下一级子流水线ADC, 作为下一级子流水线ADC 的输入信号,这样做的好处是使下一级子模块可以使用相同的参考电平。 该过程一直重复到最后一级。 因为最后一级后面不再跟有子流水线ADC,所以就不必具有减法和放大残差功能,通常最后一级采用Flash 结构。

由上可知,为了能够提高流水线ADC 的工作速率,相邻的子级电路在一个完整的周期内需要交替工作在采样或放大状态。也就是说,奇数级工作在采样状态时偶数级就工作在放大状态,反之,奇数级工作在放大状态时偶数级就工作在采样状态。

3.2.3 数字电路校正方案

(1)码域均衡(Code Domain Equalization)。 数字电路可以对流水线ADC 的主要误差包括非线性误差进行建模,并可以通过自适应均衡的技术得以校准。 这种技术通常需要输入ADC—个已知的测试信号来实现。 最常用的一种办法就是引入一个的低速高精度ADC (Slow-but-Accurate ADC), 也叫做参考ADC(Reference ADC)来估计并纠正主ADC(Main ADC)的非理想因素造成的误差。

主ADC 是一个高速低精度的ADC (Fast-but-Inaccurate ADC),将主ADC 与参考ADC 并行连接,参考ADC 的工作频率是主ADC 的1/M。 参考ADC 每M个时钟周期对输入信号进行一次采样。 将主ADC 与参考ADC 二者进行并行的连接。 连接后,参考数模转换器的工作频率是主数模转换器的1/M。 前者每M个时钟周期对输入信号进行一次采样。通过输入信号的采样,将主ADC 的输出连接到自适应FIR 滤波器上, 这个滤波器的系数由参考ADC 输出端的滤波器经过最小均方 (Least Mean Square)算法计算而得到,从而得到一个较为精确地数字输出。需要注意的是,这种方法虽然可以校正一些线性误差,如电容失配误差、输入失调误差、运放有限增益误差等,但不能校准运放增益变化导致的非线性误差[11]。

(2)分裂法(Split ADC technique)。 相比利用参考ADC 校准的技术,Split ADC 校准技术能在几乎不增加模拟设计难度的条件下,提供全数字式的后台校准,这种方法的原理是通过将单个的ADC 分成两个ADC,分裂后的每个ADC 只有原先的ADC 一半的面积和热噪底。 而分裂后的两个ADC 除了残差传输曲线外完全一样。 两个分裂后的ADC 的通道在相同的时钟下输入相同的模拟信号,而不是采用时间交织(Time Interleaved)技术。 经过上述校准技术:Split ADC 的面积和功耗相对于一个单个的ADC是不变的。 在理论情况下,两个分裂后的ADC 会输出相同的结果。 但实际上,由于存在ADC 本身的误差,两个ADC 的输出信号是仍然存在一定的差异的。 因此,两个输出信号的差值,即误差信号,可以采用均衡的算法进行校准,通过算法对两个输入信号的差值校准,可以减小信号之间的误差。由于信号和两个ADC的误差有着较高的相关性,分裂法能够保证高速的数字校准。

实际情况下, 精密的设计也存在着器件参数值失配的误差。 由于这些误差的存在,两个ADC 的残差放大曲线是不完全相同的,因此分裂法降低了算法收敛到错误状态的可能性,使得校准技术的鲁棒性(Robust)更强[12]。

(3)伪随机噪声(PN,Pseudorandom Noise)校正算法。 伪随机噪声是一个伪随机信号, 和除自身外的任何信号的长期相关都趋近于0,方差为1。随机噪声序列也是一个伪随机序列,由-1和+1 的序列组成,均值为0,方差为1。

在流水线ADC 信号处理通路中注入适当幅值的随机扰动, 经由随机扰动使得随机测试信号得到与输入信号相同过程的处理, 在这类处理中可以携带与输入信号处理过程中同样的误差因子。 这种校正方法是将随机码携带的误差在数字域中检测出来,并且在数字域中对原信号进行校正。 除此之外,也可以用伪随机码校正方法与低速高精度ADC 相结合的方法对子模数转换器的输入参考电压进行调制, 通过调制来消除电容失配误差。 由于伪随机码在大量统计点平均的情况下其均值才趋于零, 所以这种校正方法往往需要较多的采样点来达到收敛的效果。 一般来说,校正精度为N 位的流水线ADC 至少需要个采样点[5]。

(4)跳补法(Skip&Fill)。 跳补法校准技术的原理是:在输入模拟采样信号的转换过程中,周期性的或非周期性的跳过(skip)一个转换时隙, 而跳过的这个釆样值的数字输出可以用数字处理 的 方 式 来 填 补 (fill), 比 如 非 线 性 插 值(Nonlinear interpolation)的方式。 因此,这个被跳过的转换周期可以用来做数字校准。

在大多数的实际应用中,后台的数字校准技术需要至少一个采样时钟周期来完成校准功能。 如果模数转换器(ADC)每次采样一次模拟输入就校准一次,可以追踪到跟ADC 的温度变化以及器件老化等外界因素相关的参数, 这样一来也会大大的降低了ADC 的转换速率, 从而增加了模数转换器大量的消耗功率。

跳补法技术能够提供给校准电路空余的采样时隙来进行数字校准,使校准工作模式从前台转到后台,这种技术不需要大规模的改动模拟电路, 对于电路的整体功耗和性能没有大的影响,同时跳补法技术也降低了校准给ADC 模数转换器转换速度带来的不良影响[13]。

4 进度安排及预期达到的目标

熟悉数字集成电路设计的步骤, 熟练使用Verilog HDL 语言进行电路设计。 能够独立完成查阅资料,搜集信息,设计电路结构以及最后的功能实现及仿真。 完成流水线型ADC 校正电路所需的性能指标,向着高转换精度、高转换速率、低电压、低功耗、低噪声的流水线型ADC 的不断努力。

[1] 眭志凌.“Time-interleaved ADC 数字校正系统的研究与实现”,电子科技大学硕士学位论文,2013.

[2] 陈华.“16 位100 MSPS 流水线型ADC 数字自校正技术的研究与实现”,电子科技大学硕士学位论文,2013.

[3]程梦璋,景为平.“新型流水线ADC 的设计与分析”,《电子科技大学学报》,2008,37(6):930-933.

[4]戴澜,周玉梅,胡晓宇,蒋见花.“一种流水线ADC 数字校准算法实现”,《半导体学报》,2008,29(5):993-997.

[5]张淑颖.“12 bit 高速流水线ADC 数字校正技术的研究”,吉林大学硕士学位论文,2012.

[6] 彭蓓.“结合数字校正技术的纳米CMOS 流水线ADC 设计”,北京工业大学博士学位论文,2011.

[7]朱臻.“高速数据采集与转换的研究”,复旦大学硕士学位论文,2005.

[8]王玉永,曾云.“模数转换技术及其发展趋势”,《半导体技术》,2003,28(8):7-10.

[9]李浩.“深亚微米CMOS 工艺下模拟集成电路的数字增强技术研究”,中国科技大学硕士学位论文,2010.

[10]王刚、何乐年、王煊,“14 位100MSPS 流水线ADC 的低功耗设计”,《电路与系统学报》,2013,18(2):15-30.

[11]Xiaoyue Wang,Paul J.Hurst,Stephen H.Lewis.A 12-Bit 20-Msample/s Pipelined Analog-to-Digital Converter With Nested Digital Background Calibration.IEEE JOURNAL OF SOLID-STATE CIRCUITS,2004,39(11):1799-1808.

[12] 谌博.“流水线ADC 的BLMS 数字校准算法研究及实现”,电子科技大学硕士学位论文,2012.

[13]Sung-Ung Kwak,Bang-Sup Song.A 15-b,5-Msamples/s Low-Spurious CMOS ADC. IEEE JOURNAL OF SOLID-STATE CIRCUITS,Dec.1997,32(12):1866-1875.

[14]宫月红,罗敏,金杰,喻明艳.“基于 Simulink 的后台数字校正流水线ADC 行为级建模”,《微电子学与计算机》2013,30(8):155-159.

[15]宫月红,罗敏,喻明艳,马建国.“应用多项式插值的流水线ADC 后台数子校正方法”,《计算机辅助设计与图形学学报》,2013,25(11):1759-1766.

[16]Bibhu Datta Sahoo, Behzad Razavi. A 12-Bit 200-MHz CMOS ADC. IEEE JOURNAL OF SOLID -STATE CIRCUITS,2009,44(9):2366-2380.

[17]凌琦.“流水线ADC 中Offline 数字校准电路的设计与实现”,电子科技大学硕士学位论文,2012.

[18] 石寒夫.“基于BLMS 数字校准技术的低功耗流水线ADC 设计”,电子科技大学硕士学位论文,2012.