双路DC/DC TPS62402应用研究

王全振

(广州海格通信集团股份有限公司,广东 广州 510663)

随着电子行业的进步,手持设备发展越来越迅速,CPU频率不断提高,性能不断增强。目前制约手持设备最大的瓶颈是供电问题,手持设备有体积要求,因此电池的体积也不能太大,体积小限制了电池的容量也不可能做大,即所谓的“电池鸿沟”[1]。在电池容量一定的前提下,手持设备的低功耗设计就显得尤为重要。手持设备低功耗[2]设计首先在硬件方面要选择具有低功耗特性的CPU,其次在软件调节下才能实现最佳效果。在此背景下 DVFS[3]应运而生。DVFS[4]即动态电压频率调整[5],是根据芯片所运行的应用程序对计算能力的不同需要,动态调节芯片的运行频率和电压。

S3C6410[6]芯片是三星公司生产针对嵌入式低功耗系统的高性能CPU,广泛应用于工业及民用领域,该芯片高性能的ARM核及优化的外围模块特别适合做手持设备。S3C6410[8]芯片支持DVFS,一般在非民用手机的手持设备上不会选用价格昂贵的集成电源管理芯片,本文选用的TPS62402[9]芯片是TI公司生产的一款具有双路输出的DC/DC的电源芯片,该芯片具有的EasyScaleTM接口,可以方便地实现电压调节。

1 硬件设计

1.1 原理图设计

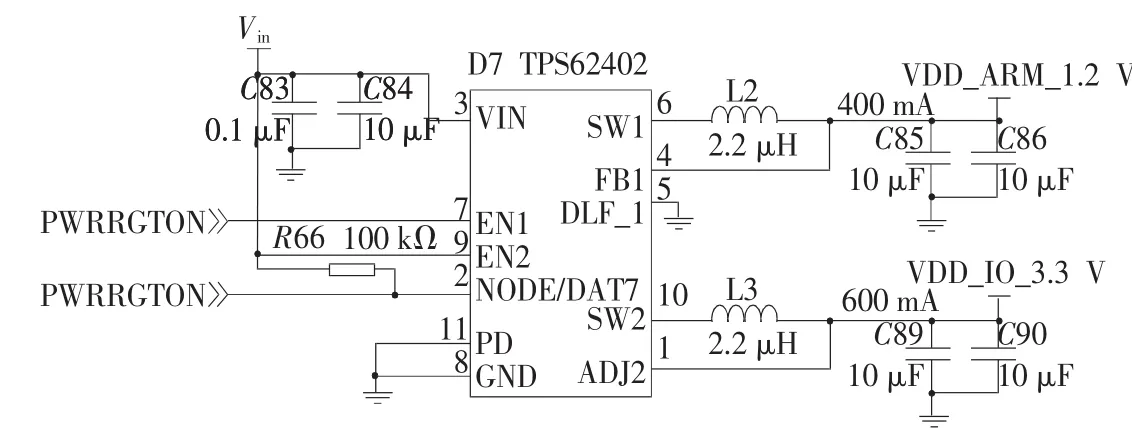

TPS62402含有两路DC/DC转换器,OUT1输出电流为 400 mA,OUT2输出电流为 600 mA,转换效率最高可达95%,2.5 V~6 V的电压输入范围非常适合手持设备采用电池来供电,OUT1(DEF_1为低时)输出电压范围以 0.025 V为步进从 0.8 V~1.575 V,OUT2固定为3.3 V输出,其DEF_1管脚设定OUT1初始输出电压值,当DEF_1为高电平时OUT1输出1.8 V,当DEF_1为低电平时输出1.2 V。本文实际使用电路如图1所示,其中Vin为电源输入;EN1和EN2为OUT1和OUT2使能管脚,OUT2设置为系统上电即开始不间断工作,OUT1连接至S3C6410的 PWRRGTON管脚,以便在低功耗模式时关闭OUT1电源输出;DATA_SET为设置OUT1电压值的通信控制管脚;SW1和FB1搭配2.2 μH 电感及 10 μF 电容组成 OUT1,DEF_1 连接至地设置上电 OUT1初始电压为 1.2 V;SW2和 ADJ2搭配 2.2 μH电感及 10 μF电容组成 OUT2,固定输出电压3.3 V。

图1 TPS62402电路设计

1.2 印制板设计要点

电路中使用的两个电感应该选择屏蔽式的功率电感,并至少留出50%的电流余量,例如L3应选择最小可通过 900 mA的电感。布局时,C83、C84应尽可能靠近TPS62402,电源的输出端要增加线宽或采用覆铜方式。

2 软件设计

2.1 接口描述

TPS62402具有EasyScale接口,即一线式串行动态电压调整接口,官方定义为:One-Pin Serial Interface for Dynamic Output Voltage Adjustment。

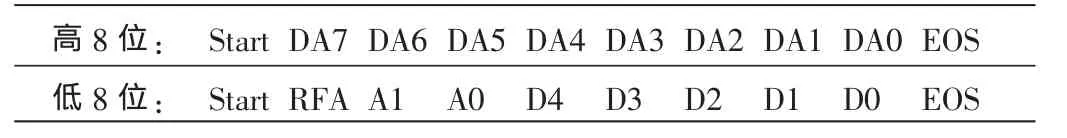

EasyScale接口以方波传输数据,其1和0以高低电平占一个周期的时间来定义:当高电平时间至少大于两倍的低电平时间则为1;反之低电平时间至少大于两倍的高电平时间则为0。每一次发送数据为16 bit,高8 bit为地址数据,低8 bit为电压数据,数据格式如表1所示。

表1 接口数据格式

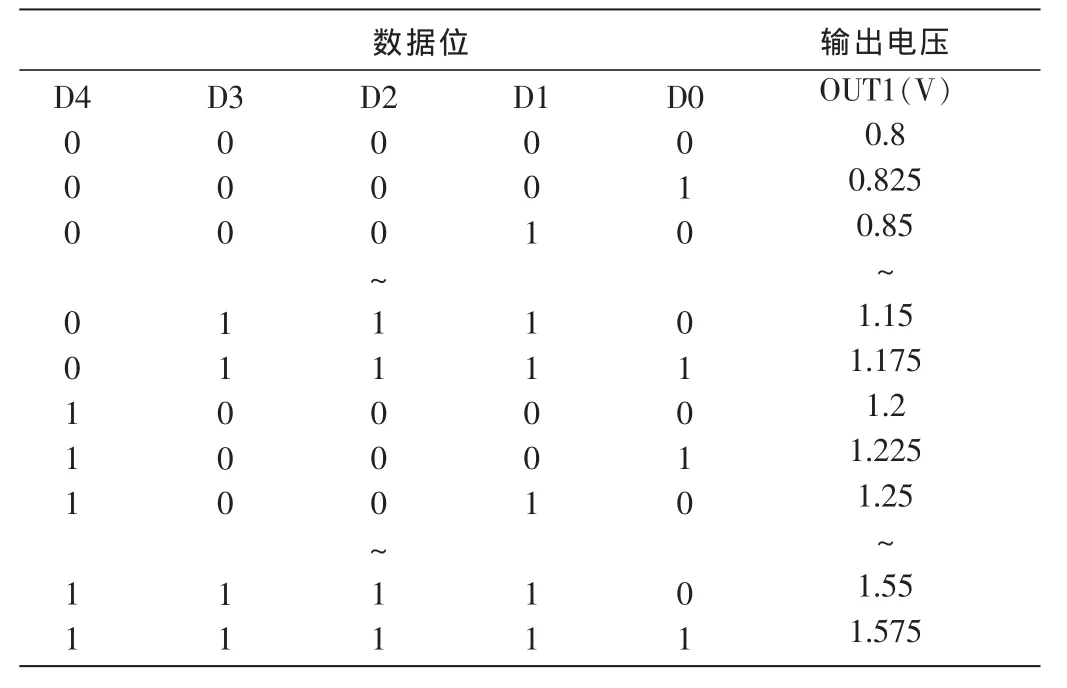

高 8 bit DA0~DA7固定为 0x4E;低 8 bit中的 RFA为请求答复设定,如果置1则TPS62402收到数据后会发出答复信号;当DEF_1为低时,A1和A0设置为00;D4~D0为电压值,对应关系如表2所示。

表2 数据与电压对应关系

2.2 驱动流程及代码

DVFS技术需要软硬件共同配合才能完成,常规流程包括以下5步。

(1)采集与系统负载有关的信号,计算当前的系统负载。

(2)根据系统的当前负载,预测系统在下一时间段需要的性能。

(3)将预测的性能转换成需要的频率,从而调整芯片的时钟设置。

(4)根据新的频率计算相应的电压。

(5)通知电源管理模块调整CPU的电压。

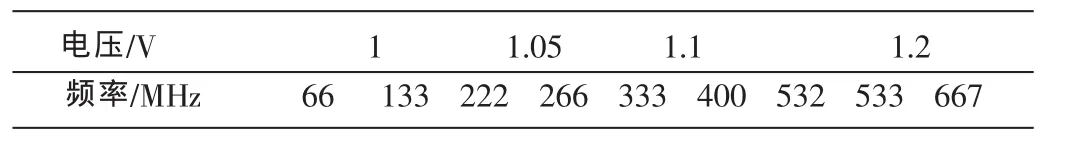

在调整电压和频率时要特别注意顺序,因为频率越高需要的电压也越高,所以当频率从高到低时要先调整频率再降低电压;频率从低到高时先升高电压再调整频率。另外电压及频率调整的频率不能过高,否则反而会增加系统能量消耗。S3C6410的核心频率设置为9挡,电压4挡,对应关系如表3所示。

表3 频率电压对应关系

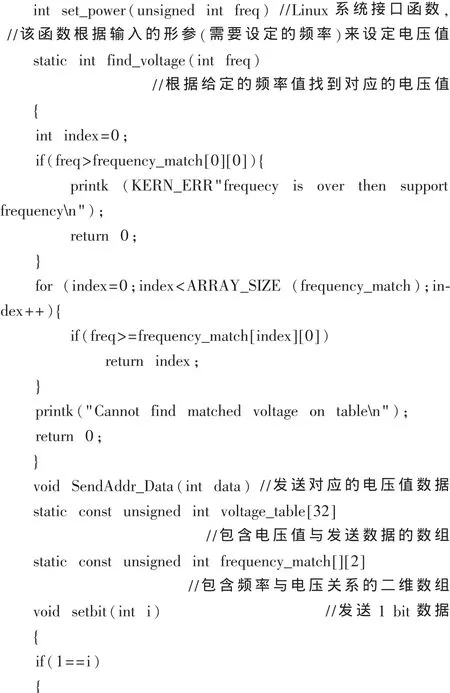

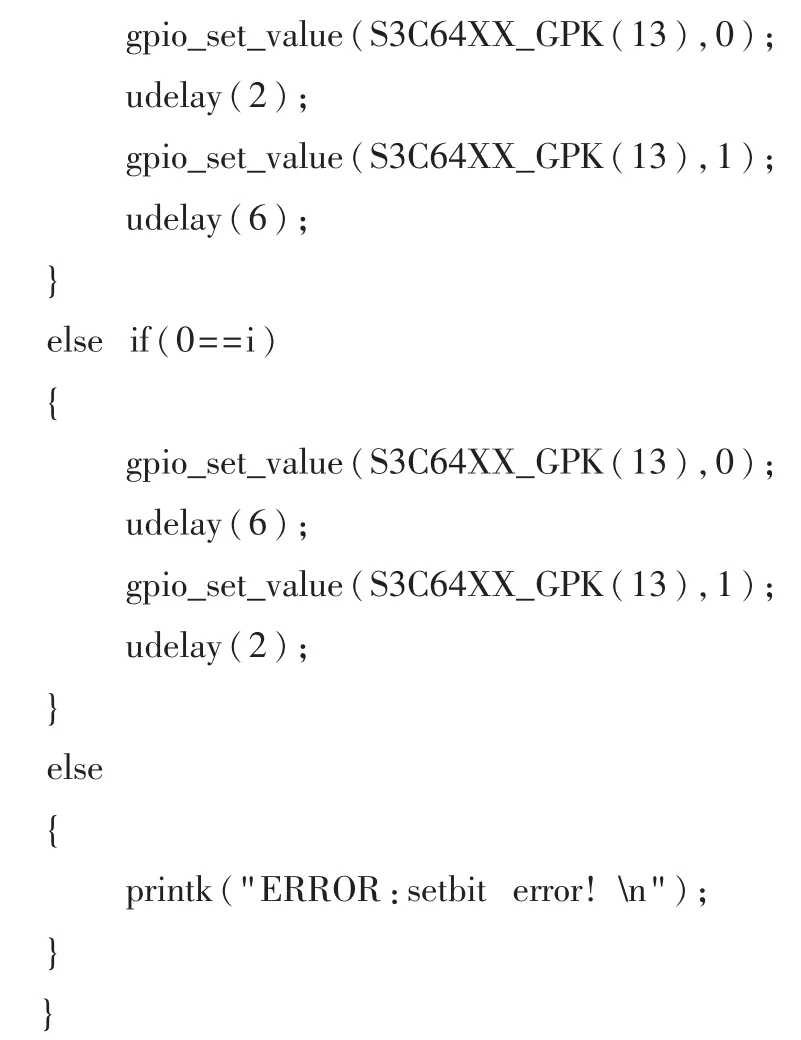

本系统中使用S3C6410的GPK13管脚来发送数据,Linux源码中已经包含DVFS,TPS62402驱动的相关函数及功能介绍如下。

setbit()函数中的 udelay()函数为微秒延时函数,延时高低电平时间比为3,满足至少大于两倍关系。

实际电路首先测试TPS62402输出电压与设定值的偏差,使用万用表测试PCB板上OUT1经过电容以后的电压,通过对表4的观察可以发现TPS62402的输出特别准确。在实际使用中,对比使用DVFS前后的功率消耗,同一设备,同一块电池,在同等条件下手持设备使用时间增加25%左右。

表4 电压对比

[1]LAHIRI K, RAGHUNATHAN A, DEYS, et al.Batterydriven system design:a new frontier in low power design[C].Proceedings of 7th Asia and South Pacific and the 15th International Conference on VLSI Design, Bangalore, India,2002:261-267.

[2]马天义.低功耗软硬件划分算法研究[D].哈尔滨:哈尔滨工业大学,2009.

[3]YUN J,SINGH D K.Dynamic voltage and frequency scaling over delay-constrained mobile multimedia service using approximated relative complexity estimation[J].Doug Young Suh EURASIP Journal on Embedded Systems,2013.

[4]张立.基于DPM和DVFS的嵌入式系统低功耗优化技术研究[D].北京:北京交通大学,2012.

[5]黄建科,周云.基于自适应 DVFS的SoC低功耗技术研究[J].现代电子技术,2009(7):120-122.

[6]邓中亮,张红星,延明,等.基于 S3C6410和无线传感器网络的手持终端设计[J].电子设计工程,2011(2):1-4.

[7]张堃.基于ARM9的嵌入式军用手持终端系统的设计与开发[D].济南:山东大学,2011.

[8]Samsung.S3C6410 datasheet[EB/OL].www.samsung.com

[9]TI.TPS62402datasheet[EB/OL].http://www.ti.com.cn/cn/lit/ds/symlink/tps62402.pdf