基于FPGA的CCD低噪声测量系统设计*

夏真珍, 汪 涛, 张 俊

(重庆大学 物理学院,重庆 401331)

基于FPGA的CCD低噪声测量系统设计*

夏真珍, 汪 涛, 张 俊

(重庆大学 物理学院,重庆 401331)

为了提高电荷耦合器件(CCD)一维尺度无接触测量系统的精度和集成度,设计了以现场可编程门阵列(FPGA)器件为核心的测量系统。对CCD输出信号进行低通滤波和相关双采样技术处理,降低了CCD信号噪声。模拟信号转换为12位数字信号后,传输至FPGA内嵌的FIFO中,提高了系统的集成度和稳定性。使用Verilog HDL语言对驱动时序发生器进行了硬件描述,并通过夫琅禾费单缝衍射实验来验证系统的可靠性和精度,实验表明:该系统稳定,精度达到0.82 %。

电荷耦合器件; 现场可编程门阵列; 低通滤波; 相关双采样

0 引 言

随着光电子技术的发展,涌现出很多光电器件,电荷耦合器件[1](charge-coupled device,CCD)为一种新型光电器件,这些年来被广泛应用于光学测量。随着CCD性能不断提高,测量系统快速采样、存储、处理和传输,是CCD数据采集发展的新方向。CCD分为面阵CCD和线阵CCD,而线阵CCD具有灵敏度高、光谱响应宽、测量范围大、线性好等优点,在一维尺度测量领域显示出其独特的优势[2]。

本文设计目的是提高系统一维尺度测量的集成度和精确度。因此,使用功能强大的现场可编程门阵列(FPGA)单芯片作为主控芯片,选用的是Altera公司EP3C16作为时序发生器,同时利用其内部自带的RAM块,建立异步FIFO,使CCD系统更小型化、集成化。同时选用东芝公司的TCD1209D作为图像采集单元,AD公司AD 9945作为A/D转换器。本文对噪声进行了系统分析和处理,提高了系统的精度和抗干扰能力,实验表明:该系统测量精度达到0.82 %。

1 系统结构

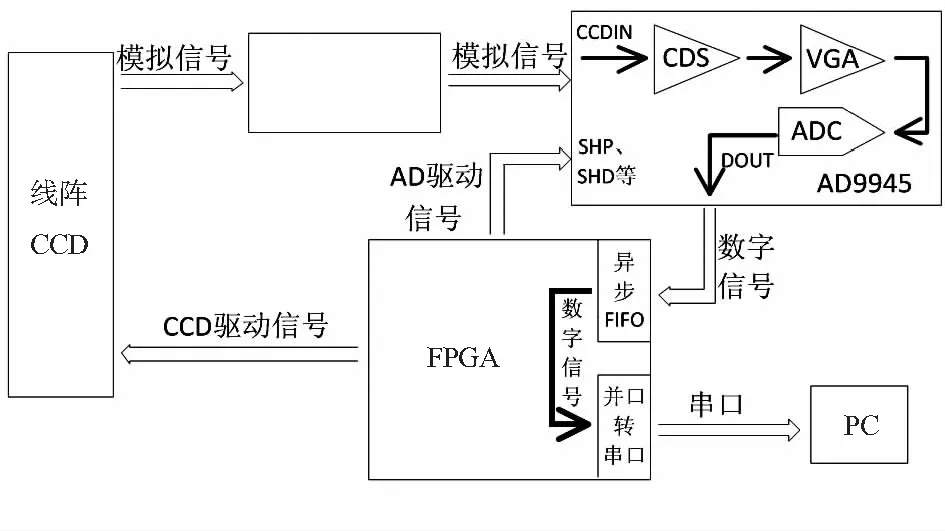

系统结构如图1所示,当衍射光垂直投射在线阵CCD上,在驱动信号的作用下CCD将光信号转换为模拟电信号,模拟电信号先通过一个低通滤波器进行滤波,再送入模/数转换器中进行模拟信号处理,处理后的模拟信号转换为数字信号,并传送至FPGA内部异步FIFO存储器中缓存起来,然后由FPGA内部并口转串口模块将数据串行输出,最后数据通过串口上传至PC机,完成数据传输[3],如图1系统结构框图所示。

图1 系统结构框图Fig 1 Block diagram of system structure

2 系统硬件模块

2.1 图像采集单元

系统选用东芝公司的TCD1209D作为感光元件,这种CCD灵敏度较高、暗信号电压较小、动态范围较大,非常适合用于尺寸测量。它有2 048个有效像元,像元尺寸为14 μm×14 μm,相邻2个光敏单元的中心距为14 μm。该CCD工作需要6路驱动时序,由FPGA产生,包括移位脉冲φ1,φ2,信号输出脉冲φ2B,转移脉冲SH,复位脉冲RS,箝位脉冲CP。

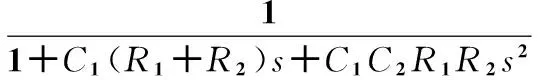

2.2 低通滤波部分

图2 Sallen-key型低通滤波器电路图Fig 2 Circuit diagram of Sallen-key low-pass filter

2.3 A/D转换部分

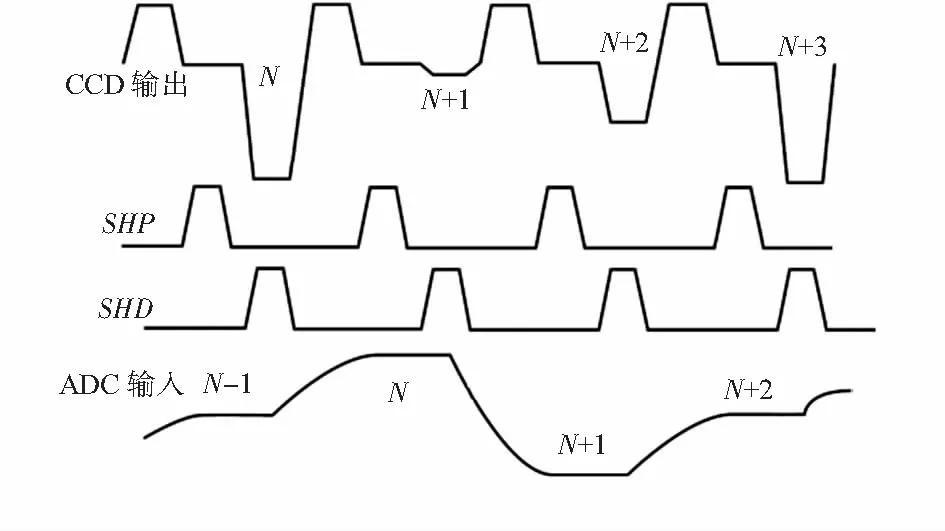

CCD模拟信号经过低通滤波电路后,传送至A/D转换器中。选用AD公司生产的AD9945,这是一种适合本系统CCD应用的完整模拟信号处理器。该芯片最高采样频率为40 MHz,而本系统CCD信号频率为1 MHz,完全能满足本系统设计需要。同时它的信号链中包含相关双采样器(correlated double sample,CDS),可以减小各种系统噪声,包括复位噪声、热噪声、1/f噪声等。CDS原理[4,5]就是用2个采样保持脉冲,其中一个为预采样脉冲(SHP),另一个为数据采样脉冲(SHD),对CCD输出信号中的每个像素进行先后2次采样。当预采样脉冲有效时,先对每个像素中的浮置栅电平部分进行一次预采样并保持;当数据采样脉冲有效时,再对信号采样并保持。2次采样差即为真正的CCD视频信号,工作原理如图3所示。

图3 相关双采样工作原理Fig 3 Working principle of CDS

同时AD 9945通过一个10位的串行数字接口编程设置CCD信号的增益,使设计简化。增益范围为6~40 dB,增益调整的公式为VGA Gain(dB)=(VGA Code×0.035 dB)+5.3 dB。最后,CCD信号通过一个12位的A/D转换器输出,将模拟信号转换为12 bit数字信号传输至FPGA内建的FIFO中。

2.4 数字信号传输部分

为了使A/D转换出来的数字信号能正确传送至上位机,本系统在FPGA内部建立异步FIFO来缓存数据。FIFO的存储介质为一块双端口RAM,由于经过A/D转换后的数字信号为12位,所以,异步FIFO设计成12位位宽。同时由于TCD1209D有2 048个像元,将RAM的深度设为2 k。CCD信号频率为1 MHz,将写时钟频率设为1 MHz。串口传输速率设为9 600波特率,则FIFO读时钟频率应大于9 600/12 Hz,所以,将读时钟频率也设置为1 MHz。当写时钟上升沿到来时,判断写信号是否有效,写入一个12位数据到RAM中;当读时钟脉冲上升沿到来时,判断读信号是否有效,若有效则从RAM中把一个12位数据读出来。

数据从FIFO存储器读出后,进入并口转串口模块,12位并行数据以串行方式传递给串口,再上传至上位机软件,显示出衍射波形。

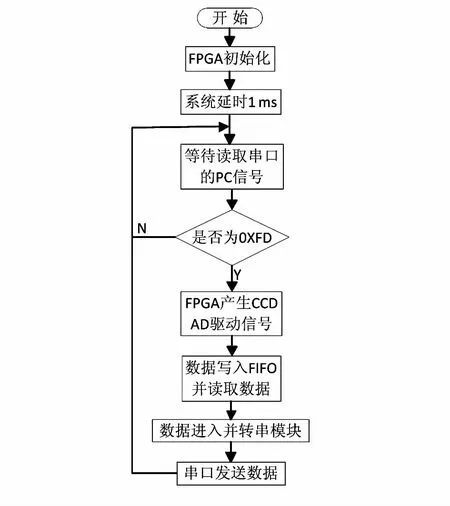

3 系统数据采集过程

电路板上电开始后,先让FPGA进行初始化,其内部建立的异步FIFO进行复位。然后系统延时1 ms,因为AD9945上电需要1 ms来复位。当PC机向串口发送读取数据的命令后,FPGA开始产生CCD和AD驱动信号,A/D转换器不断将转换后的数据送到输出口D0~D11。由于AD采样后转换输出的数字信号要延时10个转换周期,为了能准确地写入FIFO,写信号要延时10个A/D转换周期,即在A/D转换信号的第11个周期时为写信号的第一个周期,这样才能将数据写入到FIFO中[6]。

当FIFO写入2 048个数据时,它会产生满信号,此时FIFO停止写数据,等待下一次FPGA写使能信号来时才开始写数据。当FIFO数据读完时,它会产生空信号,此时发送写使能信号,进行下一帧数据传输。并转串模块将FIFO中读取出来的数据通过串口发送到PC机,完成一次数据传输。数据传送完一帧后,检验串口是否有PC机读取数据信号,进入下一次循环状态,如图4所示。

图4 数据采集流程图Fig 4 Flow chart of data collection

4 系统测试与分析

本系统通过单缝衍射实验来验证系统的精确度和稳定性。衍射现象分为两大类:夫琅禾费衍射和菲涅耳衍射,本系统仅以夫琅禾费衍射 (即平行光衍射)来验证系统性能,衍射光强分布测试光路搭建如图5所示。用He-Ne激光器做光源,激光经过光强衰减器后,垂直照射在狭缝上,产生的衍射光垂直投射在线阵CCD上,经过后续信号处理与传输模块将数据上传至PC机上显示。调节光路时需注意:狭缝的宽度、狭缝距离CCD的距离、衍射光斑的清晰度和对称性、衍射光斑和线阵CCD的平行度,这些因素都会对CCD接收衍射光强产生直接影响[7]。

图5 夫琅禾费衍射光强分布测试光路Fig 5 Testing optical path of light intensity distribution of Fraunhofer diffraction

平行光照射在宽度为b的狭缝上发生衍射现象,衍射花样为明暗相间的条纹,中央是最亮最宽的明条纹,两侧是对称的明暗相间的条纹,宽度逐渐减小。衍射光平行照射在线阵CCD上,其光强分布规律为

I=I0sin2μ/μ2,μ=(πbsinφ)/λ,

(1)

式中b为狭缝宽度,λ为入射光波长,φ为衍射角。当-λ≤bsinφ≤λ时为中央明纹,光强I0为最大值;当bsinφ=±(k+1/2)λ,k=1,2,3,…为各次级亮纹位置。代入式(1)可知,理论上0级、±1级光强比为1︰0.045 08。

图6为单缝衍射实验中测得的衍射光强分布,图中横坐标为CCD像元坐标,纵坐标为每个相元输出的电压值。从图上可以清晰地看到±4级衍射光,暗电流加杂散光引起的噪声电压大小为0.02 V。通过计算得出0级与±1级光强比为0.045 45,与理论值的误差为0.82 %,说明本系统噪声抑制的较好,精度较高。

图6 单缝衍射光强分布实验数据Fig 6 Experimental data of light intensity distribution of single slit diffraction

5 结 论

基于FPGA设计的CCD测量系统,取代了以往设计中基于CPLD和单片机的测量系统,利用FPGA的多种优势,提高了系统的集成度和可靠性。同时本系统对噪声进行了较好的处理,大大提高了系统精度。本系统还可以拓展到其它应用中,例如:无接触测量尺寸、位移测量等,当换用信号频率更高的CCD时,还可以将本系统运用到无接触振动测量中。

[1] 王庆有.CCD应用技术[M].天津:天津大学出版社,2000:30-45.

[2] 王 鑫,陈 骥,曹久大,等.线阵CCD高速数据采集与实时处理系统[J].光电子· 激光,2008,19(2):174-177.

[3] 浦国斌,张 涛,范志永.基于USB 2.0接口的CCD数据采集系统设计[J].微计算机信息,2008,24(12-1):74-75.

[4] 程鹏飞,顾明剑,王模昌.CCD视频信号处理电路设计[J].科学技术与工程,2006,24(6): 3847-3850.

[5] 王华伟,刘 波,曹剑中.CCD信号处理电路设计研究[J].科学技术与工程,2007,16(7):4153-4156.

[6] 陶纯匡,尹 刚,汪 涛.基于ARM和FPGA的CCD低噪声测量系统的设计[J].电子测量技术,2010,33(3):64-71.

[7] 潘华锦,张 丽,马春庭.利用CCD测量单缝衍射的光强分布[J].计量与测试技术,2009,36(3):57-58.

Design of low-noise CCD measuring system based on FPGA*

XIA Zhen-zhen, WANG Tao, ZHANG Jun

(School of Physics,Chongqing University,Chongqing 401331,China)

In order to improve the precision and integration of one dimension CCD non-contact measurement system, a system based on FPGA device is designed.Through low pass filtering and correlated double sampling technology process,CCD signal noise is reduced.After analog signal is converted to 12 bit digital signal,it is transfered to FIFO memory embedded into FPGA,which enhances integration and stability of system.Driving schedule generator is described with Verilog HDL.Besides,a single slit Fraunhofer diffraction experiment is conducted to validate reliability and precision of the system,experiment demonstrates that the system is reliable and the precision reaches 0.82 %.

CCD;FPGA;low pass filtering;correlated double sampling

2013—10—08

中央高校基本科研业务费资助项目(0233005205010)

TP 216

A

1000—9787(2014)04—0087—03

夏真珍(1988-),女,安徽铜陵人,硕士研究生,主要研究方向为FPGA嵌入式开发。