基于FPGA 的TFT 大屏幕液晶显示控制器设计*

陈 俊,唐小琦,周会成

(华中科技大学 机械科学与工程学院,武汉 430074)

0 引言

随着液晶技术的日益成熟,目前液晶显示器已经具有轻薄,低功耗,寿命长,接口方便的特点[1],液晶显示器在显示技术中已经得到了越来越广泛的运用。基于MCU 的屏幕驱动方法在使用上较灵活,但一般只适用于小尺寸的屏幕。例如Samsung 公司的S3C2440 内部就集成了一个液晶控制器,但最大只支持640X480的分辨率[2],如果驱动更高分辨率更大尺寸的液晶屏幕时,会使得CPU 的负载过重,造成屏幕刷新困难,甚至出现闪屏,花屏的现象。以前大尺寸屏幕的驱动都由专门的集成电路实现[3],灵活性差。而现在使用FPGA 作为接口可以驱动VGA 接口的屏幕,帧速度可以达到60HZ[4]。目前工业领域大尺寸显示屏的需求越来越大,在不便更换系统处理器平台而需要驱动大屏幕的情况下,可以基于ARM+FPGA 这种架构,ARM负责将数据经由FPGA 写入外接的显存,而将屏幕数据刷新的工作交由FPGA 屏幕驱动模块来处理,这样可以极大的减轻CPU 的负担,从而实现了大尺寸,高分辨率显示器的显示控制。FPGA 可以既作为大尺寸屏幕的驱动接口,也可以同时添加系统所需要IO,脉冲,编码器AD/DA 等接口,有效节省开发时间。

1 显示控制器的组成

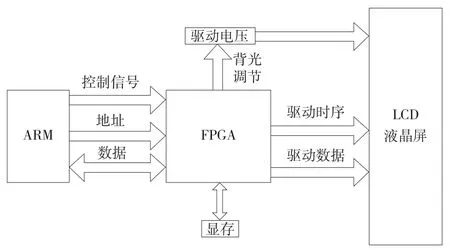

显示控制器主要由FPGA,显存,驱动电压产生电路,以及液晶屏几部分组成[5],如图1。其中FPGA 接受从ARM 发送的屏信号,经过处理后驱动液晶屏幕,而驱动电压模块产生TFT 液晶屏显示所需要的电压,以及接受FPGA 发送的PWM 脉冲来调整屏幕亮度。

图1 显示控制器组成图

由于高分辨率,多位色显示的屏幕显示需要的数据较大,FPGA 本身的数据存储能力不强,因此需要专门的显存来实现对数据的缓存[6]。采用SRAM 作为显示,操作很是方便,但会给成本带来很大的压力,于是在本文的设计中选择了SDRAM 作为液晶的显存。但是需要在FPGA 内部设计一个SDRAM 控制器来实现对SDRAM 的读、写、刷新,预充电操作等[7]。其中ARM 与FPGA 的数据位为32 位宽,如果采用64K 色(16BPP)模式,一个4 字节的数据可以表示2 个像素。

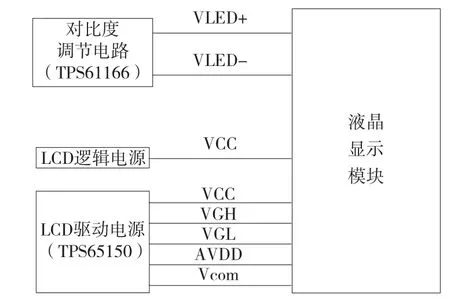

实现液晶屏幕的图像显示,需要向液晶屏提供包括AVDD,VGH,VGL,Vcom、背光电源VLED +和VLED -以及逻辑电源等多组电源[8]。为了使本文设计的驱动器能够适用于不同型号的液晶屏幕,我们采用了TI 公司的电源管理芯片TPS65150 来提供所需要的AVDD,VGH,VGL,Vcom;以及TPS61166 来提供背光电压VLED+和VLED-。图2 为电源模块的原理框图。

图2 系统电源模块

液晶显示器对于上电,下电时序有着严格的要求,如果上电,下电时序不符合要求,常常会出现乱码,锁存等现象[9]。TPS65150 能够调整电压上电顺序,使其符合相应液晶屏的上电时序要求。经过测试,表明电路能够有效的控制上电顺序,无乱码,锁存等现象。

在FPGA 内部有一个PWM 生成模块,通过接受CPU 发送的数据,以控制背光电压的输出,来实现液晶屏幕亮度的调节。当PWM 波的频率为零时,即可关断背光芯片的工作,使屏幕进入节能状态。

2 FPGA 显示控制模块设计

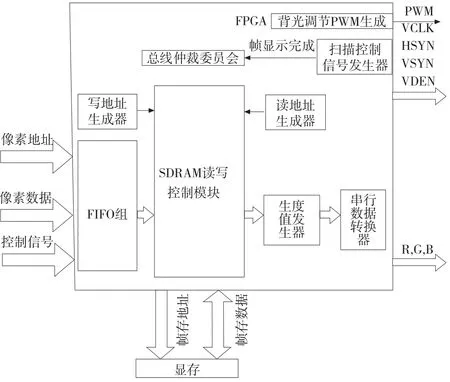

FPGA 内部功能的设计是实现液晶屏幕正确显示的关键,主要分为总线控制模块和驱动控制模块[10]。其中总线控制模块主要包括帧的片选,帧的地址产生以及帧的读写控制模块;而驱动控制模块主要包括屏显时序控制模块和屏显数据产生模块。如图3。

图3 为ARM 与FPGA 的读写控制模块,在ARM写之前,需要和FPGA 有一个“握手”信号,以便知道现在是否可以对FPGA 进行数据的写入。当数据写入时,数据先暂存入FIFO 模块,然后SDRAM 控制模块将数据进行转换后,根据写地址发生器生成的地址信号,按照一定的写时序将数据写入显存。当数据读出时,根据读地址发生器的地址信号,将数据读入灰度值发生器,最后由串行数据发生器将读取的并行数据转换成液晶屏显示所需要的串行数据送出。

解决SDRAM 分时读写的关键是ARM 发出的控制信号,和FPGA 产生的控制时序信号并完成总线仲裁逻辑。当一屏的数据刷新完成之后,通知ARM 写入新的数据,此时SDRAM 切换到写模式状态,等待接收ARM 写入的新数据,ARM 接管SDRAM 的控制权,此时ARM 发送的数据根据写地址发生器的地址经数据总线传送。数据写入完成后,SDRAM 切换为读使能信号,ARM 释放SDRAM 的控制权,不再写入新数据,使其处于等待状态,等待FPGA 读取数据信号。

图3 FPGA 显示控制模块

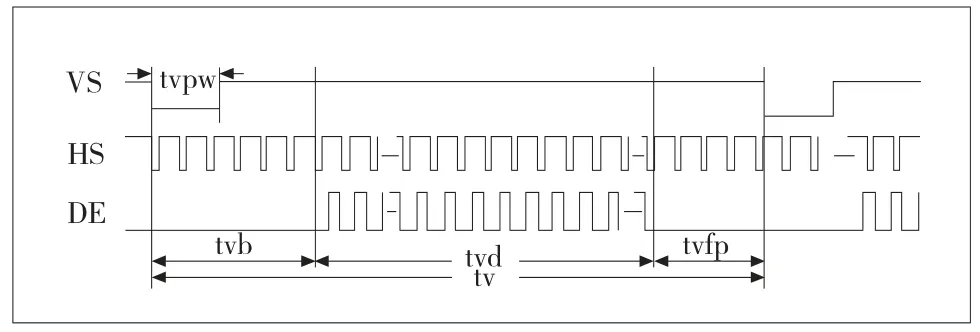

TM080SDH01 -00 的点时钟的典型值是40M,帧扫描时序以HSYN 为基准时钟,其中,HSYN 为行扫描信号,VSYN 为帧同步信号,低电平有效。每扫描完一帧(600 行),VSYN 信号有效,有效宽度为3 个VSYN(TVPW)。在VSYN 有效之前,VSYN 之前插入21 个HSYN 的帧消隐前肩,有效之后插入36 个帧消隐后肩,这样帧扫描信号相当于对HSYN 进行660 分频[11]。VSYN 时序图如图4。

图4 帧扫描时序图

同样,HSYN 以CLK 为基准进行1000 分频,其中有效点数为每行800 点,信号有效时间为48 个CLK,行前插入消隐时间为112CLK。

3 系统仿真与验证

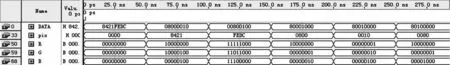

使用quartus ii 进行设计工具,并用VHDL 语句编写各个模块,最后进行仿真实验,ARM 通过32 位DATA 将图像数据写入FPGA,FPGA 经过处理后产生16位像素数据,最后得到灰度值RGB,如图5。可以发现ARM 写入的第一个数据位8421FEDC,经过FPGA 处理后得到两个像素的数据,分别问8421 和FEDC,最后每个16 位的数据依据色彩5∶6∶5的格式,得到了两组RGB 的数据,经过分析可以发现得到的两组RGB的数据就是ARM 写下来的数据,从而验证了程序设计的正确性。

图5 FPGA 读写仿真波形图

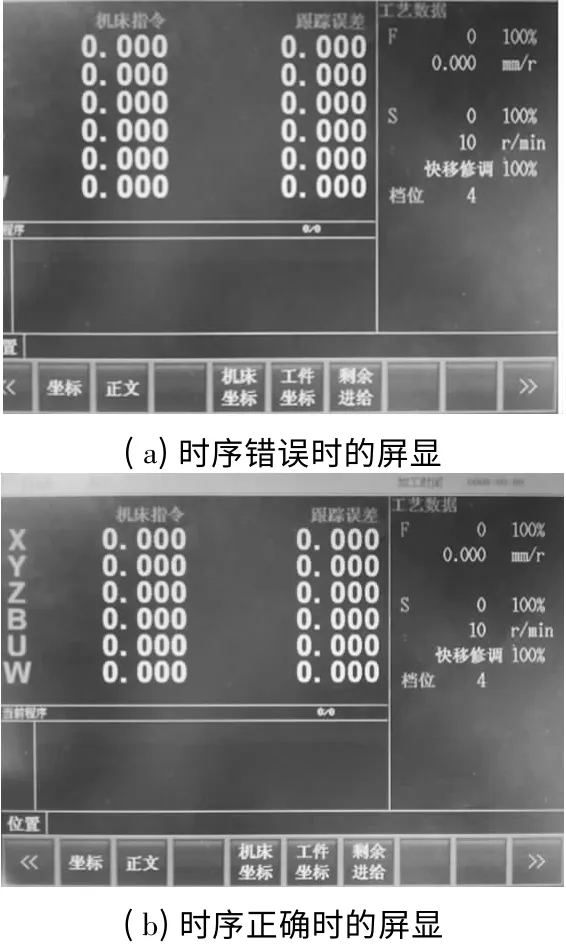

最后在ARM 上装载有界面显示的应用程序运行后,左边的图由于FPGA 驱动控制模块的HSYN 和VSYN 没有严格按照液晶屏的数据来,可以看到图像向左上方有一定的偏移。经过调试参数过后,可以发现在屏幕上已经得到了正确的图像输出。如图6 实验中所使用的屏幕的分辨率为800 ×600,嵌入式系统在复杂的加工代码计算下仍能够很稳定的驱动屏幕的显示,验证了该方法的有效性。而且通过调整FPGA 程序内部的相应的参数,修改相应的时序和显存数据位,最后验证该FPGA 模块能够有效驱动天马公司的TM097TDH01,分辨率为1024 ×768,9.7 寸液晶显示屏,大大的提升了系统所能驱动液晶屏的能力,并且完全能够满足目前绝大部分工业领域的显示需要。

图6 嵌入式数控系统

4 结论

本文提出了一种基于ARM +FPGA 的大尺寸液晶屏驱动方法,并且通过在FPGA 里面实现SDRAM的读写时序控制,以及读写总线仲裁,采用了单片SDRAM 作为显存,有效的减少了经济成本。最后在嵌入式系统中得到了实现和应用,证明了该方法能够有效的缓解ARM 的运行压力,并解决了系统运行时运行速度,寻址能力以及功耗等问题,从而支持更大区域的稳定显示,以及更加丰富的色彩显示。

[1]盛磊,徐科军,照明,陈智渊,液晶显示驱动板的设计与实现[J].电视技术,2005(2):53 -55.

[2]韦东山.嵌入式Linux 应用开发完全手册[M]. 北京:人民邮电出版社,2008.

[3]Shihong Qin,Huanhuan Li,Kai Chen. The Design of Large Screen Display Control System Based on FPFA[C]. Proceedings of the 8~(th)International Symposium on Distributed Computing and Applications to Business,Engineering and Science.2009,173 -174.

[4]Zhang Wenai,Zhang Bo,Chen Yongqian. Implementation of Bilinear CFA Interpolation and VGA Display Controller Based on FPGA[J]. Chinese Journal of Liquid Crystals and Displays,2008(1):1284 -1287.

[5]李维缇,郭强.最新液晶显示应用[M].北京:电子工业出版社,2006.

[6]刘晶,贾银亮. 基于FPGA 的液晶驱动电路设计[J]. 金陵科技学院学报,2009,25(3):26 -28.

[7]王言荣.基于FPGA 液晶控制器设计与实现[D]. 杭州:浙江大学,2006.

[8]高潮. TFT 液晶显示器驱动电路与电源优化设计方法[J].深圳信息职业技术学院学报2007,5 (2):14 -18.

[9]张超建,王厚军. 基于FPGA 的TDT-LCD 液晶显示模块设计[J].中国测试,2010,36(5):73 -75.

[10]Liang Zhiming,Li Bin. Design of scan controller in large LED screen based on FPGA circuit[J]. Chinese Journal of Liquid Crystals and Displays ,2007,22(4):477 -481.

[11] Shanghai AvicOptoelectronics. TM080SDH01 - 00 Data sheet[Z].2010:11 -12.