基于千兆以太网的高速数据传输系统设计

张金凤 李耀南

(西安电子工程研究所 西安 710100)

0 引言

近年来,FPGA在通信领域的应用越来越广泛,FPGA运行速度快,容易实现大规模系统。随着电子技术的发展,高速数据传输在现代电子系统中起着重要的作用。FPGA与普通计算机主要通过以太网接口、串口等连接。串口传输速度慢,难以实现高速数据传输,而且由于串口不能进行远程数据传输,因此要求FPGA和PC机必需在同一地点,这就限制了高速数据传输系统使用的灵活性及在特殊场合的应用。以太网接口速度高,传输距离远,便于构建FPGA和PC机的高速数据传输系统。基于以太网实现FPGA和PC机的高速数据传输方法有两种:一种是利用FPGA内嵌的MAC硬核实现,另一种是利用嵌入到FPGA的单片机实现[1]。后者逻辑控制繁琐,而且需要额外的资源,给布线带来很大的难处;前者利用FPGA自带的资源,使用简单、方便。FPGA自带的MAC硬核提供了MAC层与用户和物理层的接口,用户只需将需要发送的数据封装成MAC帧传输到MAC层与用户接口,将接收到的数据解包、错误检验和存储便可实现FPGA和PC机的高速数据互传。

1 UDP协议

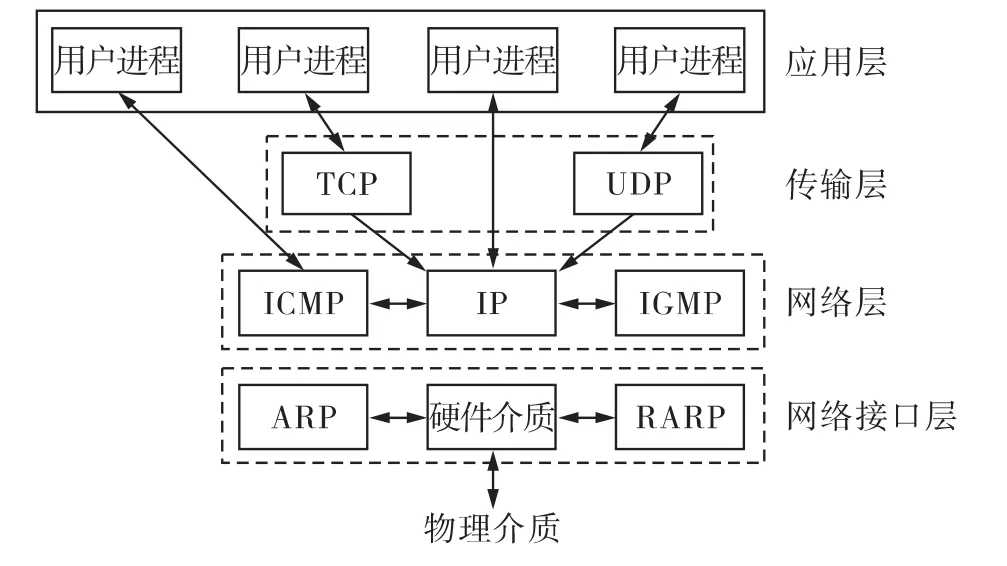

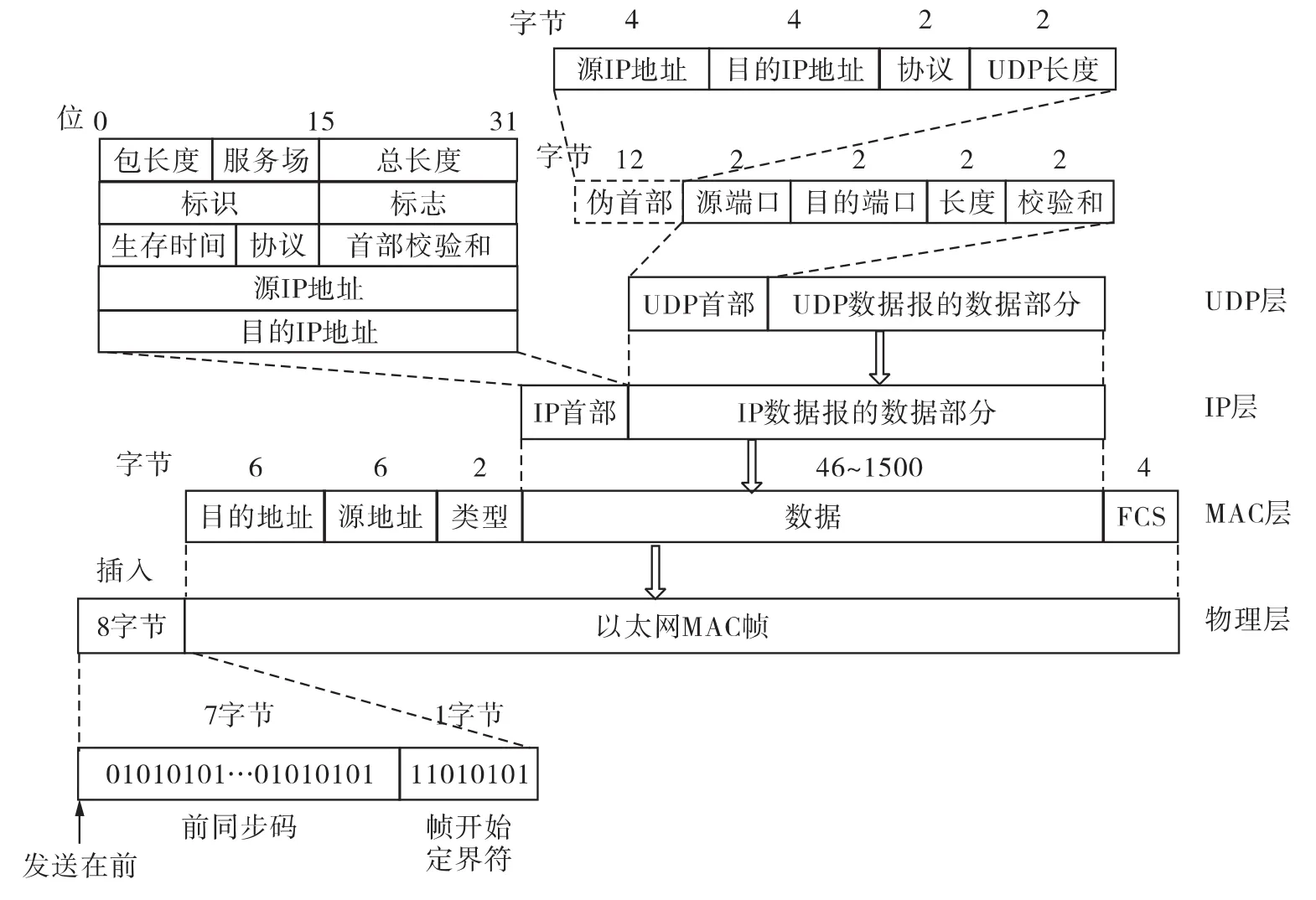

UDP和TCP是TCP/IP协议族中传输层的两个主要协议,图1给出了这两种协议在TCP/IP协议族中的位置[2]。UDP、TCP主要为应用程序传来的数据提供传输服务。TCP提供面向连接的服务,在传送数据之前必须先建立连接,数据传送结束后要释放连接,它提供可靠的传输服务,因此不可避免地增加了许多开销,这不仅使协议数据单元的首部增大很多,还要占用许多FPGA资源。而UDP是无连接的,在传送数据之前不需要先建立连接,因此减少了开销和发送数据之前的时延。UDP对应用程序交下来的报文,在添加首部后就向下交付给IP层,首部只有8个字节,比TCP的20个字节的首部短,因此UDP易于实现,占用资源也比较少。而且UDP没有拥塞控制,因此网络出现的拥塞不会使源主机的发送速率降低。所以本系统采用UDP进行数据传输。

图1 TCP/IP协议族

2 千兆以太网设计实现

2.1 千兆以太网系统设计

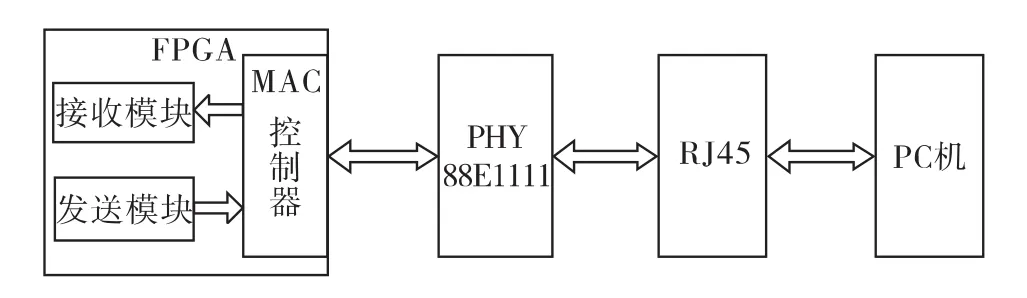

千兆以太网系统的FPGA设计工作包括以太网MAC层的FPGA设计、MAC层与上层协议的接口设计以及MAC层与物理层(PHY)的接口设计。该以太网控制器的总体结构设计框图如图2所示,整个系统包括发送模块、接收模块和MAC控制模块。发送模块和接收模块主要提供MAC帧的发送和接收功能,其主要操作有MAC帧的封装和解包及错误检测,它直接提供了到外部物理层芯片的并行数据接口,这也是本文的重点。MAC控制模块用于执行全双工模式中的流量控制功能,由IPcore产生。

本系统基于Xilinx ML605评估板实现,FPGA芯片为XC6VLX240T,它内部集成的以太网MAC核支持MII/GMII、RGMII、SGMII等多种类型接口。以太网 PHY芯片选用 Marvell公司 Alaska系列的88E1111芯片。88E1111是一款支持IEEE802.3u协议规定的自动协商机制的物理层芯片,可以支持MII/GMII、RGMII及 SGMII等多种类型的 PHYMAC接口[3]。本系统MAC层与物理层采用GMII接口。

图2 系统结构图

2.2 以太网控制器接口

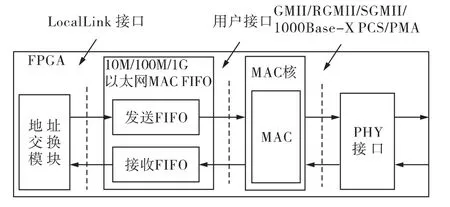

利用FPGA内嵌的IPCore生成MAC控制器时,Xilinx提供了一个以太网自发自收数据的例子程序,该例子程序是对MAC的最简最小封装,但对本系统中使用FPGA进行数据收发非常实用,如图3所示。它简化了用户和MAC数据交互程序的编写,本系统对该例子程序做了一定修改,只利用LocalLink接口以下的程序。将地址交换模块替换成数据发送和数据接收模块,实现对网络数据的封装和解包。

图3 Xilinx Gigabit Ethernet例子程序接口框图

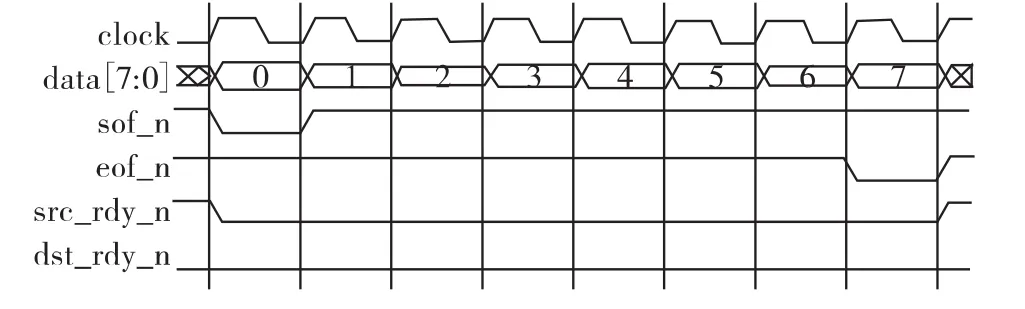

以太网MAC控制器与用户逻辑的接口为LocalLink接口,该接口以包为单位进行数据传送,数据流由sof_n、eof_n、src_rdy_n和 dst_rdy_n四个信号控制,LocalLink接口的数据发送时序如图4所示。这些控制信号都是低电平有效,当sof_n、src_rdy_n和dst_rdy_n都为低时表示一个网络数据包传输开始;当src_rdy_n和dst_rdy_n都为低时,表示正在进行网络数据包传输;当eof_n、src_rdy_n和dst_rdy_n都为低时,表示一个网络数据包传输结束[4]。

图4 LocalLink接口发送时序图

2.3 以太网MAC帧格式

标准的以太网帧结构由五部分组成,如图5所示。前两个字段分别是6个字节长的目的地址和源地址字段。第三个字段是2字节的类型字段,用来标志上一层使用的是什么协议,以便把收到的MAC帧的数据上交给上一层的这个协议。第四个字段是数据字段,其长度在46到1500字节之间。最后一个字段是4字节的帧检验序列FCS[2]。

图5 以太网MAC帧格式

本系统网络层使用IP,传输层使用UDP。发送方的UDP对应用程序交下来的报文,在添加首部后就向下交付给IP层,IP层数据添加IP首部后传送到MAC层,在MAC层将数据组成MAC帧格式。从MAC子层向下传到物理层时还要在帧的前面插入8字节(由硬件生成),它由两个字段组成,第一个字段是7个字节的前同步码(0x55),它的作用是使物理层做好发送接受准备,第二个字段是帧开始定界符(0xD5),它是帧开始的标志。

2.4 发送模块

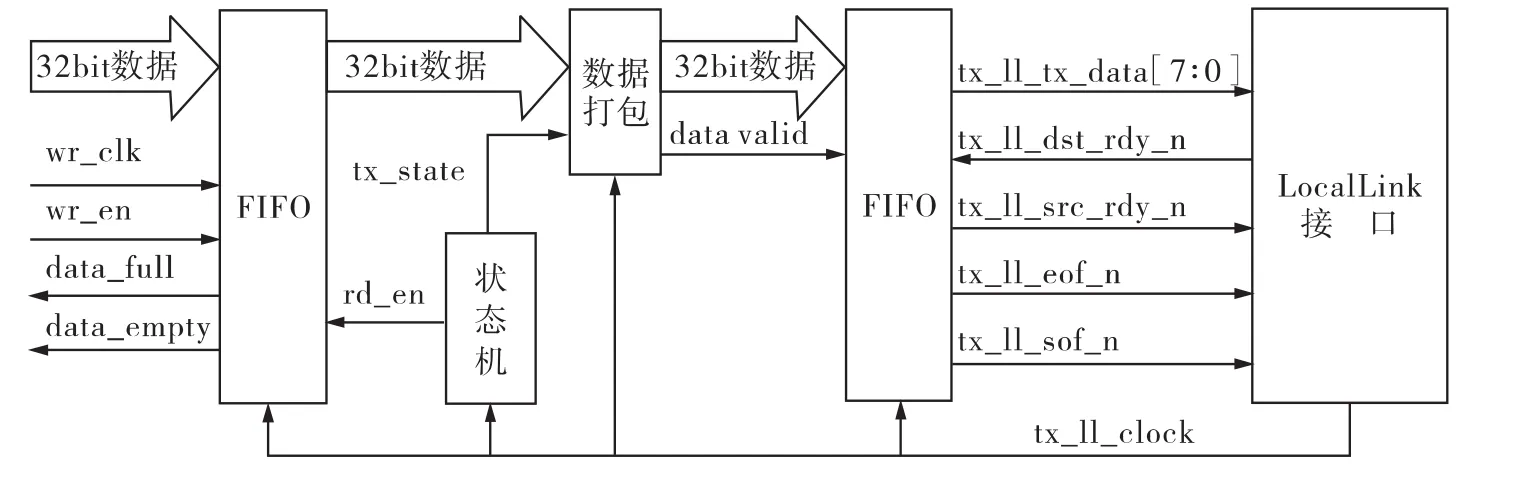

发送模块是将用户提供的数据封装之后发送到以太网MAC层,实现数据从FPGA到PC机的传输。数据封装主要是基于UDP将数据封装成图5所示的MAC帧格式,即在数据前添加UDP、IP以及MAC帧头。

发送模块与用户逻辑之间的接口通过一个异步FIFO连接,将用户要发送的数据先存入FIFO中,FIFO深度可以根据发送数据包长度自行决定,但是FIFO宽度为32bit,这是为了后续封装方便,根据FIFO的空满信号控制FIFO写数据和封装开始信号。图6为模块的具体实现过程。

图6 网络数据封装及发送原理结构图

数据封装的具体实现过程如下:

整个过程由状态机控制,该状态机包括三个状态:TX_IDLE(初始状态)、TX_UDP_HEAD(帧头封装状态)、TX_UDP_READ(数据封装状态)。

a.上层协议接到封装开始信号时,控制状态机进入TX_UDP_HEAD状态,帧头计数器累加。标识字段在系统中是一个计数器,每产生一个数据报,计数器就加1,计数器为0时执行此操作。计数器为3时开始计算头部校验和,头部校验和字段只检验IP数据报的首部。先把IP数据报首部划分为许多16bit的序列,并把校验和字段置零。用反码算术运算把所有16bit相加,总共需要6个时钟周期,将最终得到的和的反码写入校验和字段。计数器为4时,开始对IP数据首部协议字段之前的字段封装,总共需要6个时钟周期。

b.帧头计数器为9时,进入TX_UDP_READ状态,此时数据计数器累加。计数器为0时开始IP首部的其他字段以及UDP首部和发送数据部分封装,将IP首部的剩余字段和UDP首部字段完全封装一共需要5个时钟周期。数据封装过程中关键部分是UDP校验和计算,因为UDP校验和是把UDP伪首部、UDP首部以及发送数据一起检验,所以UDP校验和的计算是在发送状态机将数据从FIFO读出的过程中同时进行。计数器为2时开始从FIFO读取数据,计数器为3时开始计算数据校验和,首先置UDP校验和初始值为0x0000,并添加到UDP校验和字段,其计算方法与IP首部校验和方法相同。计数器为4时,开始数据封装。计数器值等于数据长度加4时,从FIFO读出的数据封装结束。计数器值等于数据长度加7时,校验和计算完成,此时进入TX_IDLE状态。

c.整个系统采用流水线操作,将封装数据和校验和分别存入FIFO中,利用FIFO的写计数器计数,当计数器长度为发送数据长度时,开始从FIFO中将数据读出,写入FIFO的校验和在写入的下一个周期立即读出,当校验和使能有效时,将计算所得的校验和重新写入MAC帧的UDP校验和字段。最后所得MAC帧数据再经过一个FIFO,根据以太网速度要求,控制读出数据宽度,以千兆以太网为例,读数宽度为8bit。

d.因为数据以32bit进行封装,MAC首部、IP数据报首部和UDP数据报首部总长度为42个字节,即十个32 bit和一个16bit,不是32bit的整数倍,所以在数据包末尾多加了16bit的零数据,虽然不影响UDP校验和计算,但它改变了数据长度,所以发送之前必须把末尾多加的数据截掉。从FIFO读出数据时,根据数据有效信号按照图4所示的网络数据发送时上层协议与以太网MAC层接口时序的要求产生 tx_ll_src_rdy_n、tx_ll_eof_n、tx_ll_sof_n 等控制信号就可以实现对网络数据包的传输控制。发送到PC机的数据包,既可以通过WireShark抓包软件抓包,也可以通过网络调试助手将收到数据直接存储起来,用于后续处理。

2.5 接收模块

对于FPGA收到的数据,在接收模块内完成MAC帧的解包和存储。接收模块相对于发送模块而言逻辑设计简单。接收模块收到的数据通过判断首部校验和、校验和、目的MAC地址和协议类型字段判断收到的数据是不是要发给本FPGA的,或发送的数据是否正确。

根据rx_ll_src_rdy_n、rx_ll_sof_n控制信号判断数据起始位置,此时计数器累加,将数据的前6个字节锁存起来,拼接成一个48bit的数据与本FPGA的MAC进行比较。如果不是发给本FPGA的,直接将该包丢掉,不再进行后续处理,否则,当计数器为13时,按照发送模块中计算首部校验和的方法计算收到数据的首部校验和。计数器计到23时,将该字节数据锁存,判断是否为UDP协议。计数器为25时,开始计算校验和,计数器为34时,头部校验和计算结束,计数器为41时,开始将数据存到FIFO中以便后续使用。当rx_ll_eof_n信号抬高时,计数器停止计数,数据存储结束,下一个时钟周期校验和计算结束。如果判断结果正确,且计算所得的校验和都为0XFFFF,将收到的数据用于后续处理,否则FIFO复位将该包数据丢掉。

3 结束语

本文基于千兆以太网实现FPGA和PC机的高速数据传输。采用UDP、IP协议的MAC帧格式,通过判断头部校验和和校验和字段,检测数据在传输中是否有错,提高数据传输的可靠性,而且突发速率达到1Gbit/s。利用FPGA内嵌的MAC核建立千兆以太网系统,为高速数据传输提供了方便的途径。

[1]罗侄敬.在嵌入FPGA的IP核8051上实现TCP/IP的设计[J].电子元器件应用,2007,(4):44-50.

[2]谢希仁..计算机网络(第5版)[M].北京:电子工业出版社,2010.

[3] MARVELL corp.88E1111 datasheet[CP].2004.

[4]Virtex-6 FPGA Embedded Tri-Mode Ethernet MAC user guide[M].XILINX.UG368(v1.2)[CP].January 17,2010.