基于CompactRIO的多通道强震动数据采集器FPGA的实现

吴华灯, 叶春明

(1.广东省地震局,广州 510070;2.中国地震局地震监测与减灾技术重点实验室,广州 510070;3.广东省地震预警与重大工程安全诊断重点实验室,广州 510070)

基于CompactRIO的多通道强震动数据采集器FPGA的实现

吴华灯1,2,3, 叶春明1,2,3

(1.广东省地震局,广州 510070;2.中国地震局地震监测与减灾技术重点实验室,广州 510070;3.广东省地震预警与重大工程安全诊断重点实验室,广州 510070)

提出以CompactRIO作为硬件平台,用LabVIEW FPGA技术实现48通道强震动数据采集器底层数据采集功能。详细阐述了设计要点及从技术上实现了时钟同步、数据采集、标定信号输出、量程设置、状态显示、外触发信号接入等功能。结果表明,数据采集器的噪声、动态范围、幅频响应等主要技术指标满足国内地震行业标准DB/T 10-2001的要求,数据采集器的线性度误差满足DB/T 22-2007的要求。实现的阶段成果能为人们利用NI产品进行强震动数据采集器开发提供重要参考。

CompactRIO;LabVIEW;强震动;数据采集;FPGA;锁相环; 脉冲标定;I2C

0 引言

数据采集系统的体系结构大致可分为以MCU或CPU为控制核心、以通用PC为控制核心、片上系统SOC、嵌入式实时控制与热插拔采集模块组合等几种。以MCU或CPU为控制核心构成的数据采集系统,它是一个集硬件设计和软件设计相结合的应用系统,可以充分发挥设计者的智慧,设计灵活、集成度高、功耗低、功能多、实用性强,地震行业内多采用这种体系结构,一般基于MCU/CPU+DSP+FPGA/CPLD/EPLD的结构进行地震数据采集系统设计,缺点是开发周期较长。

2O世纪8O年代中期,美国国家仪器公司(National Instruments,简称NI)推出了一种图形化的编程语言LabVIEW,并于 2002年底推出LabVIEW FPGA预展系统,目前的版本已经更新到LabVIEW 2013。传统FPGA的程序设计一般需要通过专业的开发软件完成(如ISE),也需要专业的编程语言(如VHDL)并且要求开发者具有广泛的FPGA及硬件方面的知识基础。利用LabVIEW FPGA技术,使得人们无需了解VHDL或其他底层硬件设计工具,就可以轻易、高效开发FPGA程序并将其运行于NI基于FPGA的可编程I/O硬件上,实现复杂采集系统的设计[1]。本文以CompactRIO(以下简称cRIO)为硬件平台,借助 LabVIEW FPGA技术,除了设计多路复用转换电路板外,不涉及其它硬件开发,仅仅通过FPGA编程,便低成本、短周期、高可靠地实现了多达48通道强震动数据采集器底层数据采集功能[2]。基于cRIO的数据采集系统设计,一般包括FPGA编程、实时RT编程和RT图形接口编程三部分,底层数据采集逻辑是在FPGA编程中实现。下面将着重介绍48通道的强震动数据采集器FPGA编程的实现过程。

1 基于cRIO的FPGA开发环境

1.1 硬件平台搭建

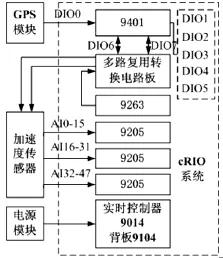

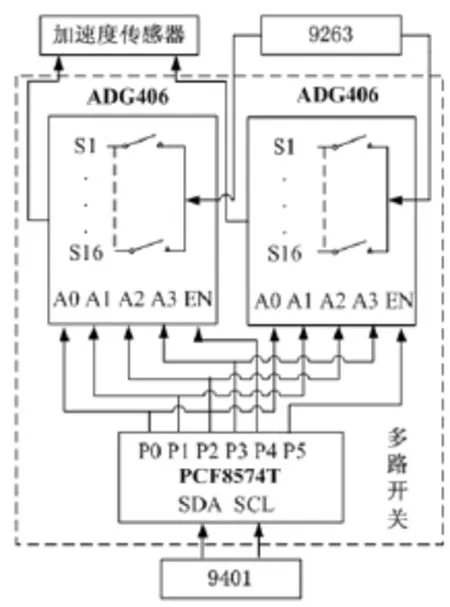

硬件平台由cRIO系统、GPS模块、电源模块和加速度传感器搭建而成。cRIO是NI公司出品的一款高级嵌入式控制和采集系统,采用可重新配置I/O技术。本设计的cRIO系统由嵌入式实时控制器9014、背板9104、模拟输入模块9205、模拟输出模块9263和高速数字IO模块9401构成[2-5]。传感器选用三分向力平衡加速度计,测量范围± 2g、灵敏度±2.5 V/g、动态范围为135 dB。硬件平台环境如图1所示。图1中,9014是安装有VxWorks操作系统的嵌入式实时控制器,用于运行实时程序,与FPGA交互,实现数据采集;背板9104是运行FPGA程序的地方,它的上一级是9014实时控制器,下一级是9205、9263、9401模块,负责数据采集和控制;9205具有90 dB的动态范围,支持16通道的差分输入。本设计采用差分方式连接传感器,接入3块9205模块共48通道信号,对应的节点分别定义为AI0-AI15、AI16-AI31、AI32-AI47;9401是具有8通道的高速数字IO模块,其作用是为获取GPS秒脉冲、外接触发、获取状态信号、I2C通信控制等提供输入输出通道;9263模拟输出模块两通道分别接多路复用转换电路板的ADG406芯片,通过ADG406芯片对加速度传感器进行标定。

1.2 软件平台搭建

在开发电脑上,安装了LabVIEW集成开发软件、LabVIEW FPGA工具包和LabVIEW驱动软件 。 LabVIEW 是 Laboratory Virtual Instrument Engineering Workbench(实验室虚拟仪器集成环境)的简称,是一个功能强大而又灵活的图形开发环境。本设计采用LabVIEW 2011 SP1专业版。

2 FPGA逻辑单元构成及工作原理

图1 硬件平台Fig.1 Hardware platform

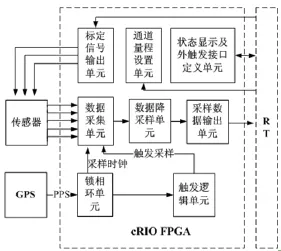

FPGA负责信号采集、数据缓存、简单的数据处理、输入/输出控制等。基于cRIO的多通道强震动数据采集器的FPGA由锁相环、触发逻辑、数据采集、数据降采样、采样数据输出、标定信号输出、通道量程设置及状态显示与外接触发源接口等八部分逻辑单元构成[2],工作原理如图2所示。锁相环单元工作时,会得到本地时钟,当接收到GPS的秒脉冲(Pulse Per Second,简称PPS)并且判断是有效的上升沿后,显示状态单元会驱动状态灯闪烁,同时执行本地时钟与GPS时钟同步的逻辑,生成采样时钟,由触发逻辑驱动数据采集单元采样数据。采样的数据经过FIFO缓冲区读写操作,被送往数据降采样单元的三级FIR滤波器进行降采样,最终回复到正常采样率的数据由采样数据输出单元传输到实时RT程序作后续的处理。当标定信号输出单元或通道量程设置单元收到指令时,将执行传感器标定或量程设置的动作。外触发接口用于连接外部触发信号源。

3 FPGA逻辑单元的设计及实现

设计基于cRIO平台,采用LabVIEW FPGA工具包,全程通过FPGA编程,形成所需的功能芯片,实现了各个逻辑单元的功能。为了实现底层数据采集的功能,并确保能够准确、可靠、稳定工作,FPGA逻辑设计着重解决了锁相环、数据采集、标定信号控制等关键问题。

3.1 锁相环单元

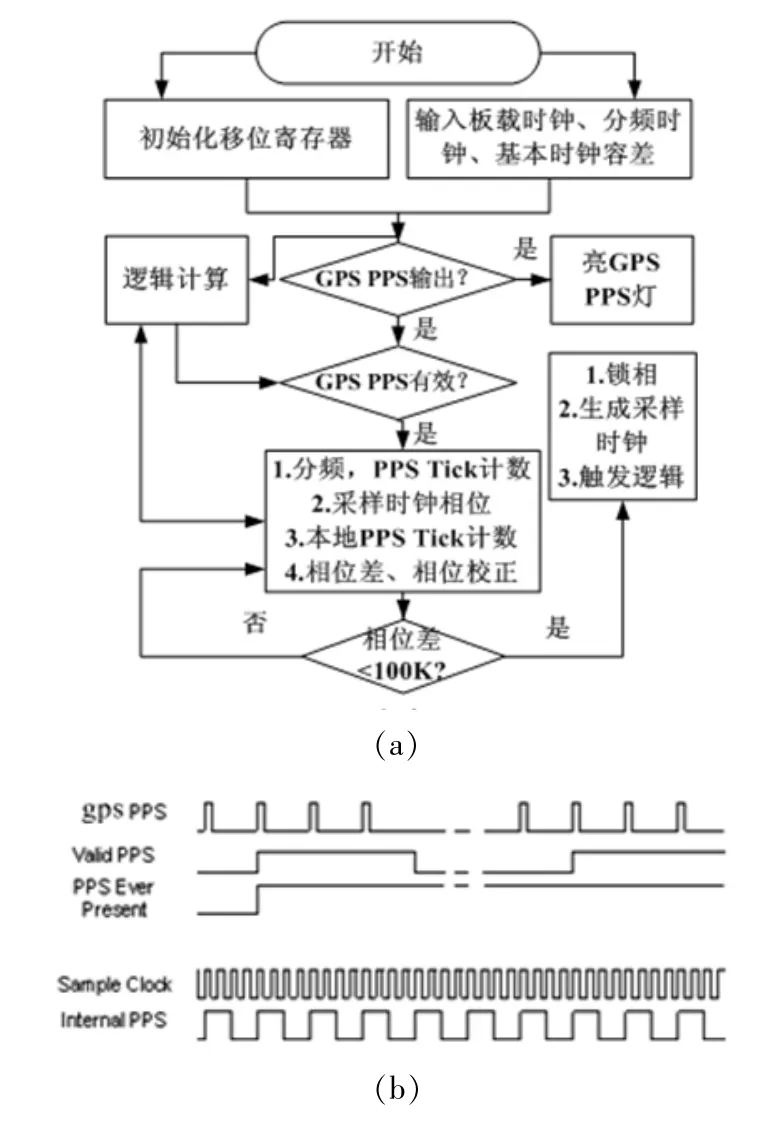

锁相环单元的作用是锁定采样时钟,对地震数据进行时间标识,确保多通道数据的时钟同步和数据时间标识的精确度。设计中采用了GPS授时技术和本地校时技术,这也是地震观测中的关键技术之一。GPS除为用户提供定位功能外,还能利用GPS卫星的高稳定性原子时钟提供同步授时服务。由于本地时钟的频率值会随时间推移和受温度变化等因素的影响而发生改变,与GPS的秒脉冲相比较,有出现同步、超前或滞后的可能。因此需要对承担时间服务的本地时钟进行频率校正和相差校正,使其以尽可能小的误差接近标称频率值,保证时间精度[6-8]。图3是校时原理及流程。图3a的校时流程首先初始化移位寄存器和输入板载时钟、分频时钟、基本时钟容差同时进行秒脉冲滴答(PPS Tick)、采样时钟(Sample Clock)、采样脉冲等逻辑计算,并求出本地秒脉冲(Internal PPS)。接着,在GPS模块输出PPS后,判断其是否是有效的上升沿,如果是,则对40 MHz板载时钟进行分频和PPS Tick计数,求出采样时钟相位、Internal PPS计数和超前或滞后相差。最后,通过逐步调整Internal PPS的相位,使其以最小的误差接近GPS秒脉冲(GPS PPS)的相位。如图 3b所示,当GPS PPS、Valid PPS、PPS Ever Present、Sample Clock和Internal PPS在同一上升沿,便实现Internal PPS与GPS PPS同步,最终锁定PPS生成采样时钟。

3.2 触发逻辑单元

当锁定PPS生成采样时钟后,触发逻辑单元设置事件发生,数据采集单元收到事件通知便执行数据采集。

图2 FPGA逻辑单元构成及工作原理Fig.2 FPGA logic unit constitution and work principle

图3 校时原理及流程Fig.3 Principle and flow of time correction

3.3 数据采集单元

图1的硬件平台搭建好后,LabVIEW将自动建立FPGA I/O节点,以对应各模块的输入/输出点,即建立了各模块I/O点与FPGA的内部联系,操作FPGA I/O相当于直接操作外部I/O点。3块9205模块接线端采用差分接入,所映射的输入分别是AI0-AI15、AI16-AI31、AI32-AI47。该单元的实现用到了FPGA I/O节点、FIFO方法节点和While循环。在While循环里,用了两层平铺式顺序结构和条件结构。平铺式顺序结构的第一层是等待事件响应条件,第二层是3块9205模块的I/ O变量,由FPGA I/O节点配置得到。FIFO数据写入缓冲区由程序生成器生成。当触发逻辑生成后,事件响应,执行一次采样,并把采样数据写入条件结构中名为BSMDecimation_DataIn的FIFO数据写入缓冲区中[9]。

3.4 数据降采样单元

为了避免信号混叠,并提高更大的动态范围,模拟数据通过采集模块时是以24倍的过采样率采集下来。在数据降采样单元,利用三级数字降采样滤波器将过采样的数据恢复到正常采样率。三级数字降采样滤波器由LabWIEW中的程序生成器直接生成,降低了程序设计的难度,也大大提高了开发效率。

3.5 采集数据输出单元

该单元用FIFO方法节点定义了一个FIFO读取缓冲区和一个FIFO写入缓冲区,用储存器方法节点定义了通道地址储存器。目的是将数据采集单元FIFO写入缓冲区的数据,按照通道的地址,重新写入到新定义的FIFO写入缓冲区,形成有通道标识的数据,为实时RT部分提供实时数据。

3.6 标定信号输出单元

为了实现对加速度传感器的标定,用到了I2C总线技术。首先,需要设计多路复用转换电路板,并进行相应的线路连接。具体做法是用两片Analog Devices公司的多路复用芯片ADG406和一片Philips I2C并行口扩展芯片PCF8574T设计成16路的复用转换电路。其中,9401模块的DIO6、DIO7通道分别与PCF8574T的串行数据线SDA和串行时钟线SCL相接,进行并行口扩展。9263的AO0、AO1通道分别接到两片ADG406上。其次是通过FPGA编程实现标定信号的发送。如图4所示,在FPGA里,通过I2C通信,向PCF8574T芯片指定地址发送设定的通道号数据,打开指定的通路,再由9263模块输出两组方波信号,控制ADG406芯片将两组方波向相应通道的加速度传感器发送过去,实现标定。

设计的I2C通信遵循I2C规范,使用高速模式的总线时序,采用7位寻址[10-12]。从机的地址为100 000,读写位为0,发送的1字节数据包含通道号、SDA及SCL的使能状态。

3.7 通道量程设置单元

9205模块具有±200 mV、±1 V、±5 V、±10 V四档电压量程。在实际测量过程中,针对不同的观测对象往往需要设置不同的量程。在通道电压量程设置单元里,程序的实现是把通道号、待设置的量程组成数组簇,在While循环里,根据数组簇中通道号数据,计算出9205对应的AI通道节点,赋待设定的量程值到 “设置电压范围的FPGA I/O节点”中的电压范围输出端子即可。

3.8 状态显示与外接触发源接口单元

图4 多路复用转换电路工作原理Fig.4 The principle of multi-channel switch

状态显示与外接触发源接口单元包括PowerLED、StatusLED两个状态灯和 ExtTrigger、Btn1及 Btn2三个外接触发源。它们都是通过FPGA I/O节点的操作来获取数据。如图1所示,PowerLED、StatusLED分别对应的节点是9401模块的 DIO04、DIO05通道。ExtTrigger、Btn1及Btn2分别对应DIO01、DIO02、DIO03通道。局部变量 Start Sample、 Internal PPS和布尔变量Logging的逻辑决定了StatusLED FPGA I/O节点输出端子的值。PowerLED FPGA I/O节点输出端子的值则由Error布尔变量的非和计数器的逻辑或决定。外接触发源的值通过三个布尔变量赋值得到。

4 检测方法及结果分析

FPGA的设计及实现关系到数据采集系统成败。为了验证FPGA各个单元的准确性和可靠性,在设计过程中,编写了每个单元的调试、测试程序,可以显示各个环节的关键参数和状态。重点对锁相环、数据采集、标定信号输出单元进行了测试检验。

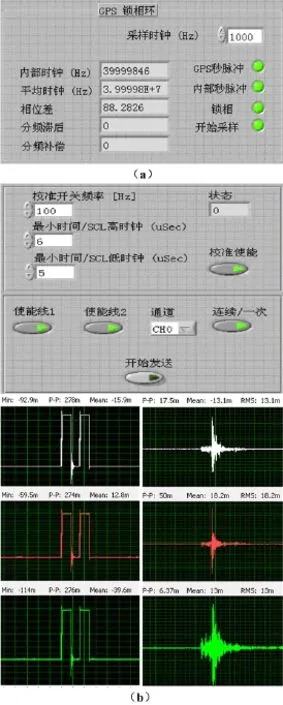

图5a是GPS PLL的测试界面。右边的四个状态灯绿色显示时,分别表示当前GPS秒脉冲是有效的、内部秒脉冲已经获取到、锁相已经成功并开始了采集。左边的时钟是当前内部秒脉冲的滴答计数,平均时钟是GPS秒脉冲的滴答计数,两者接近40 MHz标称频率,与标称频率相差小于等于200 Hz,即不到5微秒的钟差 (每滴答是25纳秒),符合中华人民共和国地震行业标准DB/T 10-2001中校时精度优于1 ms的要求[13]。相位差就是采样时钟与标称频率的相位之差。因为小于100 kHz的相位差,时钟精度已经在1 ms的范围内,所以在程序设计里,设定了相位差小于100 kHz便锁相的操作。实测的Phase Error均小于2 000 Hz,图中的相位差则更小,仅有88.282 6 Hz。图5b是标定信号控制和数据采集的实测情况。①图5b的上方是I2C通信的测试控制界面,用于发送标定控制信号。②图的下方左侧是从加速度传感器反馈回来被9205采集到的其中一组标定波形,波形无畸变。③图下方右侧是实际采集到的振动信号。除了采集真实的振动信号,观察有无波形畸变外,还进行了采集器的线性度误差检测、噪声检测、动态范围检测和幅频响应检测,验证数据采集器的关键性能指标。受篇幅限制,以9205-1模块实测数据为例,描述检测方法和相应的检测结果。

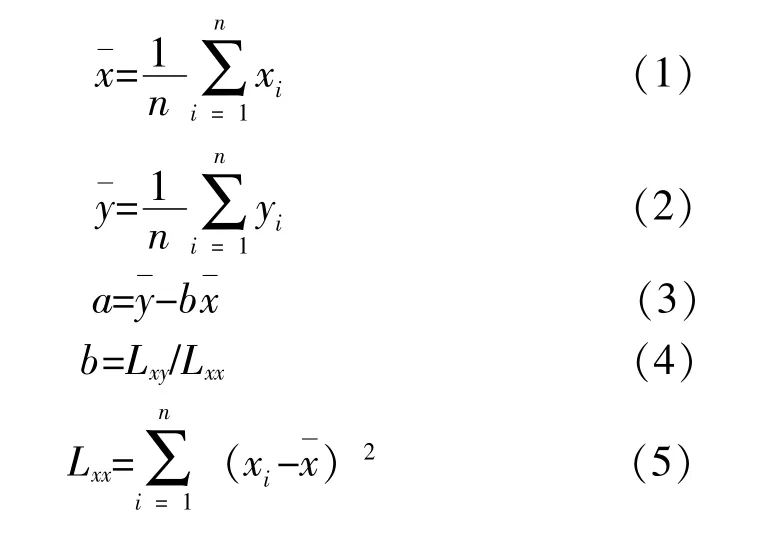

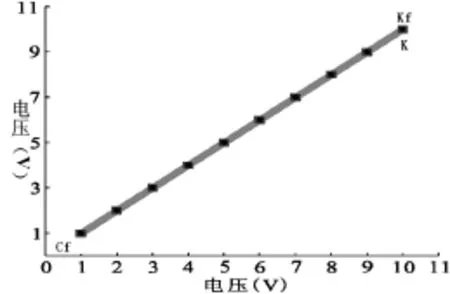

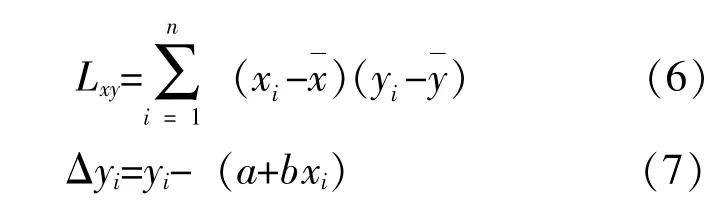

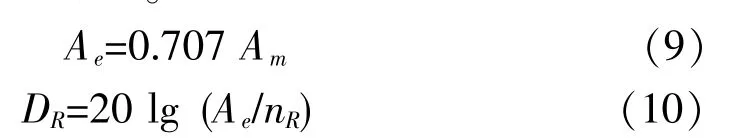

与线性度误差相关的主要是增益误差、偏置误差和积分非线性误差(INL)。前两项是线性误差,可以通过定期校准来减小或消除。本文在标定时,测试信号设置为5 Hz的正弦波,选取了幅值为满量程的10%、20%、30%、40%、50%、60%、70%、80%、90%、100%均匀分布的10个标准值x,每个标准值xi测量10次,10次测量值的平均值yi作为实测值。将yi绘图,理想情况下得到一条近似的直线,再将该直线上的所有点用最小二乘法做最佳直线拟合,得到斜率为Kf、截距为Cf的拟合直线。标准值绘制的是理想直线,斜率为K。拟合直线截距Cf的绝对值就是偏移误差,而拟合直线斜率Kf与理想直线斜率K之差的绝对值定义为增益误差,实测值减去拟合后的直线,残留的就是线性偏差,也称积分非线性误差。如图6所示,标准值用直线表示,实测值用方点表示,拟合后的直线用圆点表示。实测值及计算结果见表1。表1各参量反映了实测值和标准值的线性拟合关系y=a+bx,如下所示:

图5 锁相环、数据采集、标定信号输出测试界面Fig.5 The test interface of PLL,data acquisition andcalibration signal output

图6 线性度误差Fig.6 Linearity error

最后,线性偏差Δyi由公式(7)求得。

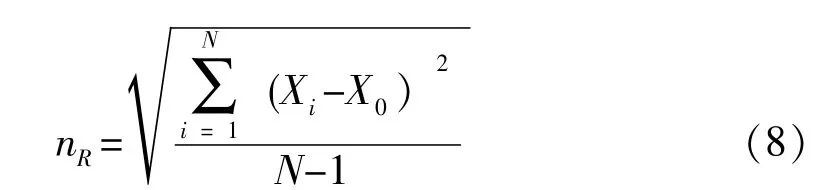

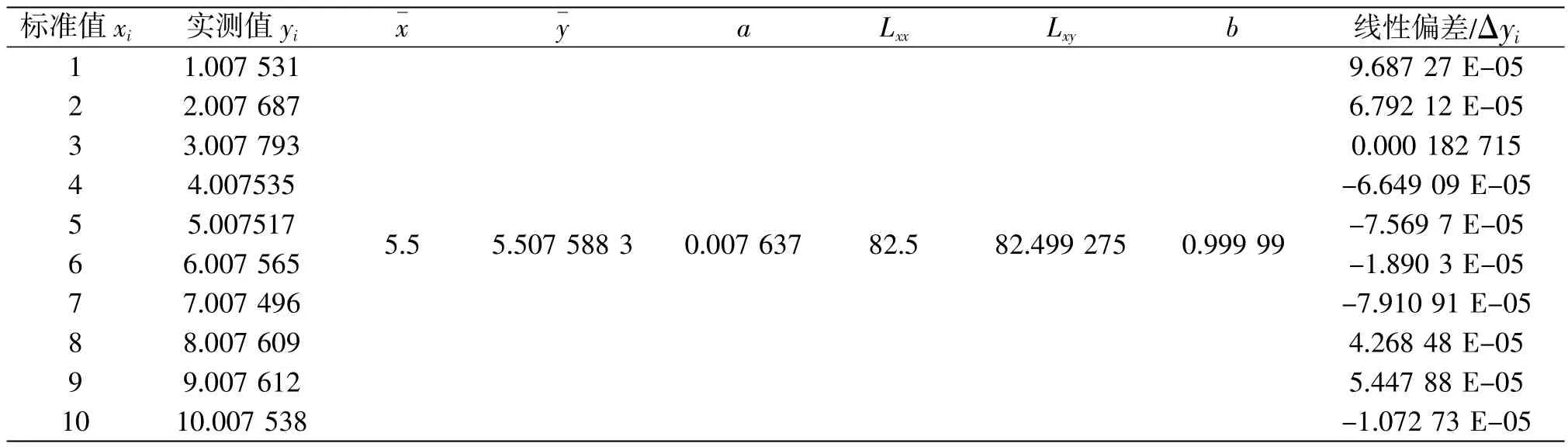

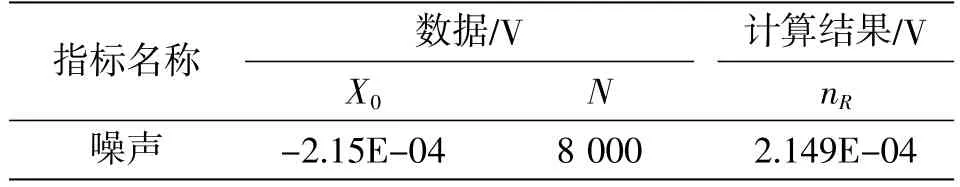

噪声检验的方法是:将 9205-1、9205-2、 9205-3模块各通道输入端短接并接地,在200 sps采样率下记录4 000个以上采样数据(i=1,2…,N),计算的平均值,按照(8)式计算噪声均方根值,实测数据及计算结果见表2。

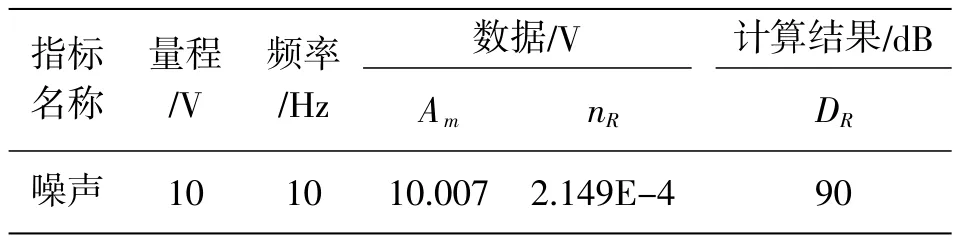

动态范围检验的方法是:用数字信号发生器向9205模块输入端输入频率为10 Hz、振幅为10 V满量程的正弦波信号,按照(9)式计算采样记录的有效值Ae,Am是采样记录的振幅值,单位为伏特(V)。最后,按照(10)式计算采集器的动态范围。实测数据及计算结果见表3。

表1 线性度误差检验数据及计算结果Table 1 Linearity error inspection data and calculation results

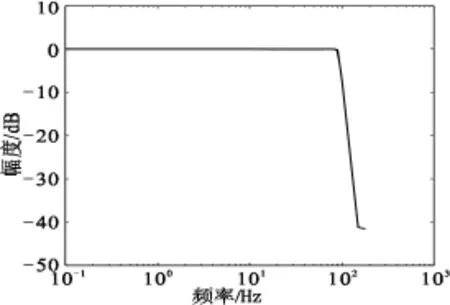

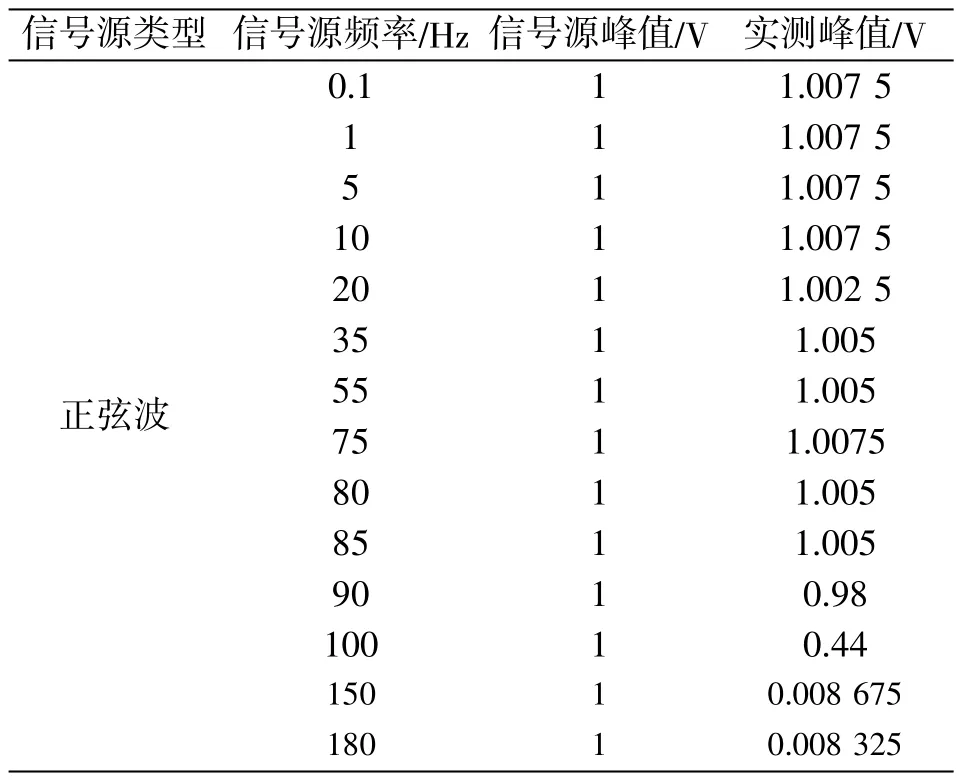

幅频响应测试的方法是:用数字信号发生器在14种频率下输出幅度稳定的正弦波电压,对采集器进行幅频响应测试,实测数据见表4,幅频响应曲线见图7。

表2 噪声检验数据及计算结果Table 2 The noise inspection data and calculated results

图7 幅频响应曲线Fig.7 Response curve of amplitude frequency

表3 动态范围检验数据及计算结果Table 3 The dynamic range inspection data and calculated results

表1 Δyi集合中绝对值的最大值是0.000 182 715 V,线性度误差远小于地震行业标准DB/T 22-2007中满量程的0.03%,即0.003 V的技术要求。此外,从表1的数据及图6均可以看出,实测值成直线分布,与拟合直线和理想直线重叠,反映了增益误差、偏置误差特别小,整体的精确度非常高。表2计算出的噪声均方根小于噪声均方根上限值2.158E-4 V,符合DB/T 10-2001标准中理论计算要求。表3计算的动态范围也与硬件的动态范围吻合。从表4实测数据及图7可以看出,数据采集器在0~90 Hz内频率响应是平坦的,优于DB/T 10~2001标准0~50 Hz的频率响应范围。

表4 幅频响应检验数据Table 4 Amplitude frequency response inspetion data

5 成果应用

项目的研究成果,具有创新性和实用价值。首先在虎门大桥上部署使用,记录了大量的震动波形数据,为计算这座桥梁关键部位的峰值加速度、频率分布、桥面地震响应及传递函数和桥梁的振动周期等提供了宝贵的基础数据。与之相关的技术应用方案,曾经获得过美国国家仪器有限公司颁发的 “最高成就奖”,并在 《仪器仪表学报》上得到录用和刊登。其次,还在我国新丰江水库大坝地震反应专用台阵上进行了部署应用。其中记录到2013年2月22日11时34分发生在河源的M4.8级地震,是新丰江水库大坝强震动数字化观测史上取得最有价值的数字化地震记录,取代了前期进口的多通道数据采集器不能正常记录地震事件的缺陷。项目的研究成果陆续部署到汕头礐石大桥地震反应专用台阵、汕头国际隔震试验楼台阵开展强震动观测应用。该项目的成果,也适于向石油、地质、建筑设计等行业领域推广使用,目前已经推广到省内外多家单位的项目建设中,具有较好的市场前景。

6 结论

基于CompactRIO开发强震动数据采集器,在国内地震行业是一种新的尝试。本文基于cRIO硬件平台,设计了多通道数据采集器FPGA逻辑单元并利用LabVIEW FPGA技术加以实现。整个设计实现过程几乎不涉及硬件开发,主要通过软件编程实现了GPS PLL、数据采集、标定信号输出等复杂的功能。实验结果表明,数据采集器的噪声、动态范围、频率响应等主要技术指标满足中华人民共和国地震行业标准DB/T 10-2001的要求,数据采集器的线性度误差满足DB/T 22-2007的要求。实现的阶段成果将为后续的实时RT编程和RT图形接口编程提供可靠的数据接口,项目的成果能为重大工程、生命线工程、超高层建筑和特殊结构的强震动观测提供新型的观测仪器,同时也能为人们利用NI产品进行地震数据采集器开发提供重要参考。

[1]陈树学,刘萱.LabVIEW宝典[M].北京:电子工业出版社,2011.

[2]叶春明,吴华灯,郭德顺,等.基于NI cRIO的多通道强震动监测与报警系统开发[J].仪器仪表学报,2010,31(4):357-361.

[3]刘云峰,沈庆宏,阮静,等.基于QF4A512的加速度测量系统的实现[J].电子测量技术,2012,35(9):106-108.

[4]黄豪彩,杨灿军,陈道华,等.基于LabVIEW的深海气密采水器测控系统[J].仪器仪表学报,2011,32(1):40-45.

[5]吴邦春,彭晓彤,周怀阳,等.基于海底观测网的深海化学监测系统的设计[J].仪器仪表学报,2011,32(5):1171-1176.

[6]杨俊强,毛征,曹锋,等.多通道数据实时采集标时系统设计[J].国外电子测量技术,2011,30(3):29-32,36.

[7]马海瑞,韩云东,袁群哲,等.基于LABVIEW的GPS信息采集与解析[J].国外电子测量技术,2011,30(9):64-66,75.

[8]行鸿彦,武向娟,吕文华,等.自动气象站数据采集器温度通道的环境温度补偿[J].仪器仪表学报,2012,33(8):1868-1875.

[9]崔佩佩,何强,韩壮志,等.用LabVlEW FPGA模块实现不同时钟域的数据连续传输[J].现代电子技术,2011,34(17):149-152.

[10]亓成宇,史晓锋.高速曼码解码器及其I2C接口的FPGA实现[J].电子测量技术。2011,34(10):53-56,95.

[11]张清秀,孔令昌,江劲军,等.新型流气式固体氡源用于氡仪器标定的实验研究[J].华南地震,2012,32(3):60-67.

[12]蔡晓葳.一种低功耗单片机与I2C总线连接的设计[J].国外电子测量技术,2011,30(8):70-72,76.

[13]中国地震局.地震标准汇编2009(第二册、第三册)[M].北京:地震出版社,2010.

Implementation for Multi-channel Strong Motion Data Acquisition System FPGA Based on Compact RIO

WU Huadeng1,2,3,YE Chunming1,2,3

(1.Earthquake Administration of Guangdong Province,Guangzhou 510070,China;2.Key Laboratory of Earthquake Monitoring and Disaster Mitigation Technology,CEA,Guangzhou 510070,China;3.Key Laboratory of Earthquake early Warning and Safety Diagnosis of Major Project,Guangdong Province,Guangzhou 510070,China)

By taking CompactRIO as hardware platform,and using LabVIEW FPGA technique,the paper bring about the bottom data acquisition function of 48 channel strong motion data acquisition.The paper elaborates the key points of design in detail,and technically realizes the function of clock synchronization,data acquisition, calibration signal output,range set,state show,external triggering signal access,etc.The results show that the recorder's main technical indicators,for example,noise,dynamic range,frequency response,etc,meet the domestic requirements of seismic industry standard DB/T 10-2001 and linearity error meets the DB/T 22-2007. The stage result realized can provide important reference for people who will develop strong motion dataacquisition by use of NI products.

CompactRIO;LabVIEW;Strong motion;Data acquisition;FPGA;PLL;Pulse calibration;I2C

TP274+.2

A

1001-8662(2014)03-0033-07

10.13512/j.hndz.2014.03.06

吴华灯,叶春明.基于CompactRIO的多通道强震动数据采集器FPGA的实现[J].华南地震,2014,34(3):33-39.[WU Huadeng,YE Chunming. Implementation for Multi-channel Strong Motion Data Acquisition System FPGA Based on Compact RIO[J].South china journal of seismology,2014,34(3):33-39.]

2014-03-01

广东省科技计划项目(2009B080701095),地震科技星火计划项目(XH1019Y)资助

吴华灯 (1980-),男,理学学士,工程师,主要从事地震观测研究和软硬件开发工作.

E-mail:1160285781@qq.com.