高速通信系统PCB的电磁兼容性设计*

陈 岩,陈 曦

(中国电子科技集团公司第30研究所,四川成都610041)

0 引言

随着综合业务和多媒体通信的快速发展,直接对通信系统提出了高速交换、大容量数据传输的设计要求。如:40 Gb/s、100 Gb/s以太网、SDH线路和背板高速传输,都对时钟、信号线方面提出了具体要求。当信号频率超过1 GHz,互连关系必须充分考虑传输线、电源、叠层、板材电参数等诸多因素的影响,在PCB的叠层、布局布线、阻抗匹配、高速差分线等设计方面均与设备的信号质量、电磁干扰和性能相关。而要如何做好这些,则需要在高速电路的PCB设计过程中进行完整的电磁兼容设计。

1 高速通信系统的电磁兼容性

高速通信系统主要应用对处理性能和传输速率都要求较高的场合,常选用高性能嵌入式CPU,如:MIPS、PowerPC、ARM 等,核 心 工 作 频 率 可 达1.5 GHz以上;常选用超高速通信接口,如:XAUI(万兆以太网)、SATA(并串与串并转换)、PCIE等,传输速率都在Gb/s以上。所以在进行信号完整性(SI)设计时常见问题主要包括:反射、串扰、振铃、过冲、地弹等[1]。

反射:反射就是信号在传输线上的回波,一般由于在传输线上阻抗不连续引起,部分能量会被反射回源端。

串扰:是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。

振铃:振铃表现为信号反复出现过冲和下冲,在电平门限上下抖动,振荡呈欠阻尼的状态。振铃主要由于传输线上过度的寄生电感和电容,引起收端与源端的阻抗失配造成。

电磁干扰(EMI),包括传导干扰和辐射干扰[2]。传导干扰是指通过电介质把一个电网络上的信号耦合到另外一个电网络;辐射干扰指干扰源通过空间把其信号耦合到另外一个电网络。由于高速器件对干扰敏感,很容易接收到高速假信号并给出响应,有时会对板卡正常工作产生致命的影响。

电磁兼容(EMC),它是研究在有限空间、时间和频谱资源等条件下,各种电气设备可以共同工作的科学,研究的重点之一在于如何尽可能的降低电路的 EMI。

2 高速通信系统的PCB设计

2.1 系统架构设计

由于通信设备的PCB设计重点和难点往往集中于高速差分线、高速并线总线和电源的设计上,这几部分的设计是否满足要求很大程度上直接关系到板卡最终是否可用。

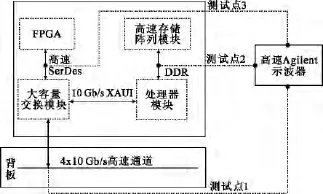

所以本节结合某通信设备中高速路由板的设计,重点详细介绍高速板卡的PCB设计方法。该路由转发板主要应用于骨干网的核心交换设备。板卡采用CPU、存储阵列、FPGA和交换芯片的硬件架构,EMC设计难点主要在于:①CPU、DDR和FPGA信号频率较高,切换速度快;②系统需要满足40 Gb/s实时业务的处理,对系统性能要求很高;③PCB面积小,芯片引脚密度高、属高密度板设计;④电源种类繁多,很多模拟电源,对电源纹波要求非常高;⑤用户对设备的电磁兼容指标要求严格,上述要求对板卡的EMC设计提出了巨大的挑战。图1简单展示了该板卡的硬件设计架构。

图1 板卡硬件架构Fig.1 Hardware architecture of board

FPGA采用Xilinx公司的V5系列芯片,配合外围电路组成。该芯片是Xilinx公司推出的高性能FPGA,逻辑资源丰富,同时支持高速SerDes接口。

处理器模块与外围的高速存储阵列模块之间采用DDR接口,DDR采用源同步接口,选通信号DQS使用双沿来采样数据 DQ,目标速率达到1 600 Mb/s,并行传输总线速率非常高。其中时钟锁相环的抖动、偏斜、PCB布线偏斜、同步开关噪声、串扰和码间干扰都会对芯片的时序产生影响,在PCB设计中必须重点考虑。

交换芯片与背板之间采用4路XAUI接口,每路XAUI传输速率达10 Gb/s。同层串扰、噪声、损耗、抖动等问题都会对高速差分信号产生影响,最终表现在误码率和系统的EMI上。

2.2 具体PCB设计

通信设备中高速总线的SI和EMC直接影响到板卡的性能,在设计中,如何防止高速信号在传输线上的反射、串扰,降低电磁干扰,保证信号完整性是高速总线的设计重点,在本设计采取了如下的设计方法和步骤:

1)叠层设计:文中的高速PCB板卡均采用多层板设计(见图2),通过增加地平面数量来改善板卡的EMC。增加地平面的作用在于保证了每层信号都有特性阻抗较低的地平面作为参考平面,而且可以有效的避免信号层间信号线的串扰。在本设计中,高速XAUI、SerDes差分线和DDR信号选择信号质量最好的S1层和S2层走线。

图2 高速路由板PCB设计Fig.2 PCB sheet of structure

2)布局布线设计:综合系统信号流、不同种类功能进行布局,如:CPU等数字电路、锁相环等模拟电路、接口电路、电源和时钟;按照信号流向关系,尽可能保证XAUI、SerDes差分线和DDR高速并行总线走线最短,时钟信号走线尽可能短,同时对参考时钟和关键信号采用包地的方式进行处理,降低关键信号的电磁干扰和电磁辐射。对于传速速率不高的低速信号线尽量避免信号线周围有强辐射,同时进行单端50 Ω的阻抗匹配的处理。

在文中的设计中,单端信号采用线宽0.15 mm,外部间距大于0.2 mm的约束条件。差分信号采用如下的约束条件:布线长度不超过38.1 mm,线宽0.15 mm,内部线间距0.15 mm,外部线间距大于0.5 mm,差分阻抗采用100 Ω匹配,精确匹配差分对走线,误差控制在0.15 mm以内。

3)高速差分线设计。差分信号接收端接收到的信号是差分信号线间的电压差,在高速通信总线中,由于差分线的长度不同会引起两根线间出现相位差,从而破坏差分信号的磁场抵消作用并产生EMI。在本设计中,XAUI、SerDes差分总线保证了差分线对长度误差控制在0.05 mm以内[3]。

以本系统的高速差分时钟设计为例:本系统中的高速时钟设计需要提供4路125 MHz时钟分别提供给FPGA。2路156.25 MHz时钟提供给FPGA作为XAUI接口参考时钟和工作时钟。本设计中选用专用的高精度晶振和IDT公司的专用时钟合成芯片来产生精度非常高的差分时钟。在高速差分钟的PCB布线选用TOP层的微带线,原因在于:虽然信号层S1、S2相比TOP层的电磁干扰更小,但是必须通过过孔换层,这样会增加信号的传输延迟;同时保证差分信号之间的紧耦合,保证差分线对的线间距小于或等于线宽,这样处理来有效的抵消磁场和电场的互耦合,并减少对外的电磁辐射。

4)采用源端和终端阻抗匹配:匹配电阻主要起到了吸收反射的作业,同时也能保证总线正常传输差分电压。在本设计中,差分线端采用封装为0402贴片电阻,并靠近接收引脚(控制在5 mm内)。同时,在电阻中间通过电容接地来滤除共模噪声。

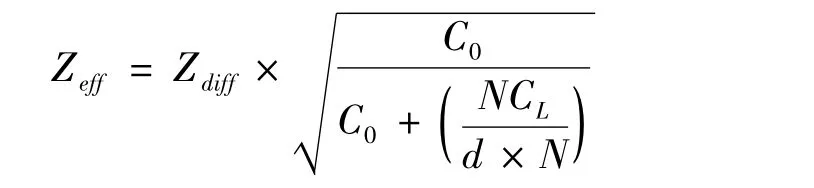

匹配公式选用Xilinx公司推荐的终端匹配电阻计算公式,公式如下所示:

式中,Zeff为差分线差分阻抗,Zdiff为差分线特性阻抗,约为单端传输线阻抗2倍。C0为传输线感抗特性;CL为终端负载的电容特性;N为总线上负载个数;d为总线上相邻槽位之间间距。

5)背板接插件选择:高速信号常遇到由于线路阻抗不匹配而出现的信号反射,印制线阻抗在板卡生产过程可以严格控制,但是在背板接插件处因无法控制容易出现信号反射。本设计选用无源背板方式,采用ATCA架构的高密度、高速度的差分接插件,保证了信号在背板连接器上反射尽可能小,同时高速信号的过孔选择了微通孔也保证了过孔对信号影响最小。

综上所述,作者在PCB设计过程中采用合理的叠层设计,根据信号流和分类进行了最优化布局,既保证了信号的参考平面完整,又大幅度降低了印制板的电磁辐射;按照高速线布线规则重点对高速差分信号和时钟进行了约束和设计,同时对高速信号进行了阻抗匹配,既保证了高速信号完整性,又最大程度避免了信号的反射。通过以上处理最大程度上做到了设备的电磁兼容设计最优化。

2.3 电源完整性设计

电源信号的质量很大程度上会直接影响到板卡上信号的质量,尤其对于芯片模拟电源如果引入的噪声较大会直接影响使用。

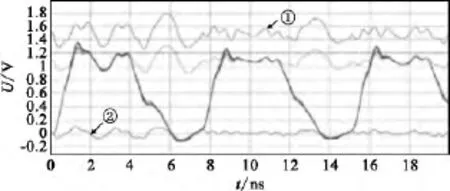

图3展示了在理想电源(线①)条件下,信号对地漂移(线②)非常小;图4展示了一旦电源层(线①)和地层(线②)上叠加了噪声,信号纹波明显增加。

图3 理想电源和信号关系Fig.2 Relationship between ideal power and signal

图4 实际电源和信号关系Fig.3 Relationship between practical power and signal

作者曾经在其他项目的电源设计时遇到过如下的问题:①在进行芯片的模拟电源设计时未选用纹波较小的LDO芯片,而选用了DC-DC芯片,导致模拟电源纹波较大,导致芯片工作稳定性较差;②对于电压相同类型不同的电源未采用磁珠进行隔离,导致不同芯片之间电源出现相互干扰,噪声增大,影响板卡工作的稳定性。所以文中在充分总结电源部分设计经验的基础上,在设计电源完整性设计时采用了以下的处理手段:

1)合理布局,模数分离。电源布局采用电流方向进行,同时输入模拟电源和本板的数字电源、电源和地层之间尽可能进行隔离,电源和信号部分尽可能远离,最大程度降低外界输入的电源的噪声对信号的干扰。

2)对不同类型电源尽可能采用独立的电源模块供电。对于电压相同,类型不同的电源,采用磁珠进行隔离,降低电源间串扰。对于电流较小的模拟电压采用线性电源供电。

3)电源包地处理。由于电源层和地层之间磁场的不停变化,在电路板边缘会向外辐射电磁波,称之为边沿效应,采用电源层内缩,地平面包裹的方式,保证了电源层辐射的磁场只在地层传导。

4)多种滤波电容组合。为降低电源输出端产生的纹波及电流冲击对板卡的干扰,在电源的输入、输出端通过添加高频电容、电解电容并配合电感组成滤波电路,过滤不同频段噪声。

这里在电源设计过程中首先在合理布局,模数分离的前提下,采取了独立供电措施,最大程度降低了不同电源间的串扰;进行了电源包地处理,减小了电源的电磁辐射;最后配合RC、LC滤波电路组合,最大程度吸收了电源噪声,降低了电源纹波。通过本设计保证了电源的电磁兼容设计最优。

3 实验与验证

为了对板卡的信号完整性和EMI进行验证,搭建测试平台对板卡进行全面测试,测试系统框图如图5所示。

图5 板卡SI和EMI测试平台Fig.5 SI and EMI test platform

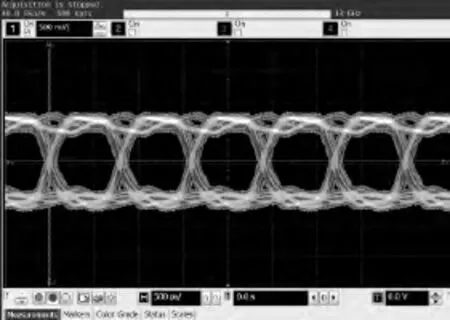

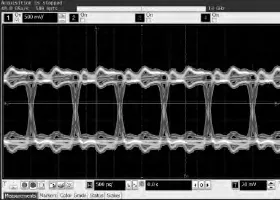

测试中使用了Agilent公司高带宽、高采样率示波器,型号 DSA91304A,带宽13 GHz,采样率可达40 GSa/s。选择了3个关键信号作为测试点,通过测试点的眼图、频谱图来对信号质量作较为全面的分析和评估[4]。图6、图7和图8分别表示测试点1、2和3的眼图,从每个眼图的张开度、信号的建立保持时间来看,信号漂移和抖动很小,稳定可靠;同时测试了某块因叠层设计错误而导致层间信号出现串扰的板卡的千兆链路信号,信号眼图如图9所示。从眼图来看,信号抖动明显,眼图不规则,信号质量较差,有较大的时序风险,所以该板卡在实际使用过程中经常出现丢包的情况。

图6 测试点1眼图Fig.6 Point 1 eye diagram

图7 测试点2眼图Fig.7 Point 2 eye diagram

图8 测试点3眼图Fig.8 Point 3 eye diagram

图9 串扰信号眼图Fig.9 Crosstalk signal

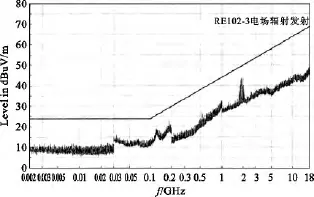

使用德国R&S公司EMI测试系统,按照某标准对整机进行了电磁兼容测试,测试设备在不同频率范围下的电磁辐射强度。图10给出了根据RE102-3标准,在垂直极化下,频率范围为 0.002~18 GHz的电场辐射发射图,从图上看设备在2 GHz频点左右有较强辐射;图11给出了根据RE102-3标准,在水平极化下,频率范围为0.03~18 GHz的电场辐射发射图,从图上来看设备在500 MHz左右电磁辐射信号较强。总体来看,整机的电磁辐射冗余较大的控制在标准之内,较好的满足指标的要求。

图10 垂直极化电磁辐射Fig.10 Horizontal polarization EMI diagram

图11 水平极化电磁辐射Fig.11 Vertical polarization EMI diagram

4 结语

文中针对高速通信系统PCB的电磁兼容设计原则和方法,结合项目实际进行了详细论述,先后提出了高速信号完整性、叠层、布局布线设计方法和实施原则;高速差分总线、时钟设计的约束原则以及电源完整性的设计原则,最后通过实验对本设计的信号完整和电磁兼容性能进行了充分的验证,实验结果表明,本系统在信号完整性和电磁兼容性方面都能够满足设计要求。

综上所述,通信系统PCB设计工程师,应该深刻理解EMC、传输线理论,仔细分析和总结引起各种信号畸变的原因,不断的提高自身的设计水平,同时在设计中灵活应用EMC的设计方法和原则,大幅提升设备的性能。

[1]ERIC BOGATIN.信号完整性分析[M].李玉山译.北京:电子工业出版社,2005.ERIC BOGATIN.YUSHAN LI translated.Signal integrity analysis[M].Beijin:Electronic Industry Press,2005.

[2]岳春华,尹征琦.高速PCB电磁兼容的研究[J].电子质量,2007(08):92-94.YUE Chun-hua,YI Zheng-qi.High Speed PCB EMC Research[J].Electronic Quality,2007,(08):92 -94.

[3]邱剑.差分线对的 PCB设计要点[J].通信技术,2010,43(06):221 -223.QIU Jian.Main Point on PCB Design of Differential Signal[J].Communications Technology,2010,43(06):221 -223.

[4]高晓宇,杨龙剑.高速串行通道的信号完整性问题分析[J].通信技术,2013,47(06):44 -47.GAO Xiao-yu,YANG Long-jian.SIAnalysis of High-Speed Serial Channel[J].Communications Technology,2010,47(06):44-47.