6 kV链式STATCOM控制器设计

唐艳波,张敬,李文峰

(1.国网青岛供电公司,山东青岛 266003;2.山东电力建设第一工程公司,山东济南 250100;3.中国电力科学研究院,北京 100192)

目前几乎所有的STATCOM均采用DSP芯片作为控制器,其开发周期长、I/O点数少,无法用一个DSP芯片完成多台SVG的并机运行。而且DSP易受外界环境干扰,造成程序不能正常运行[1-3]。具有DSP数字信号处理功能单元的FPGA,具有并行运算能力,其运算速度以及I/O点数可以满足STATCOM控制要求。同时FPGA内部程序采用逻辑阵列实现,不易受外部环境干扰。因此采用全FPGA技术对6 kV链式STATCOM的控制器的硬件结构进行了设计,具有一定的应用价值。

1 STATCOM工作原理

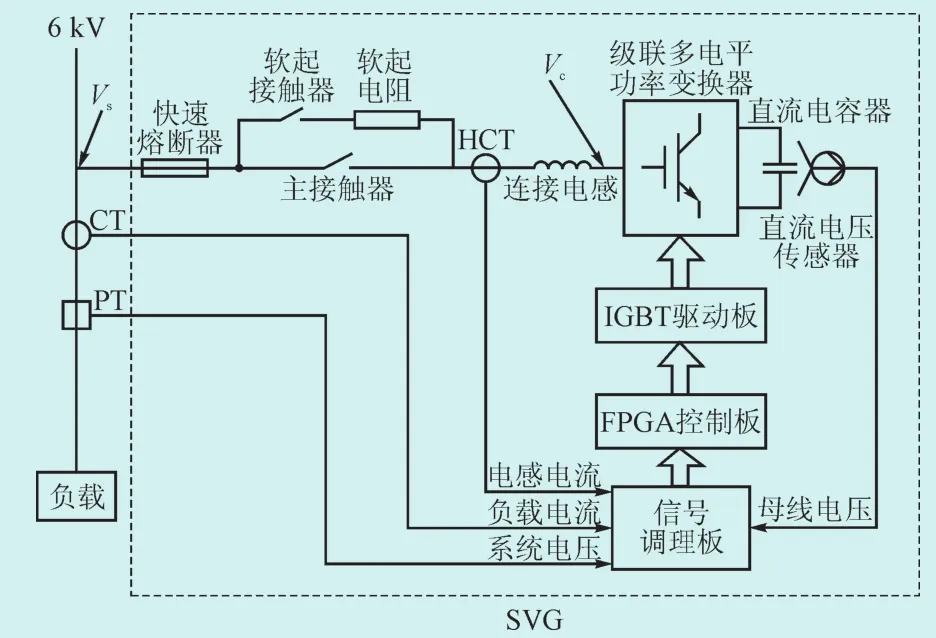

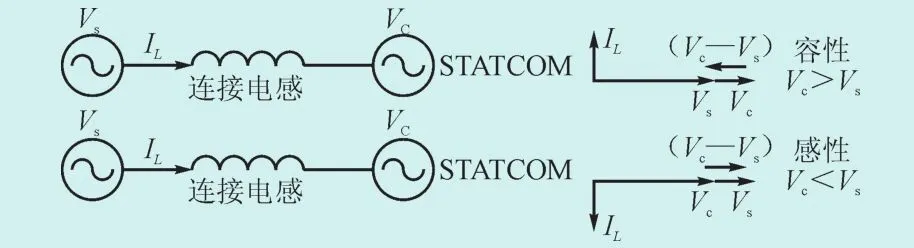

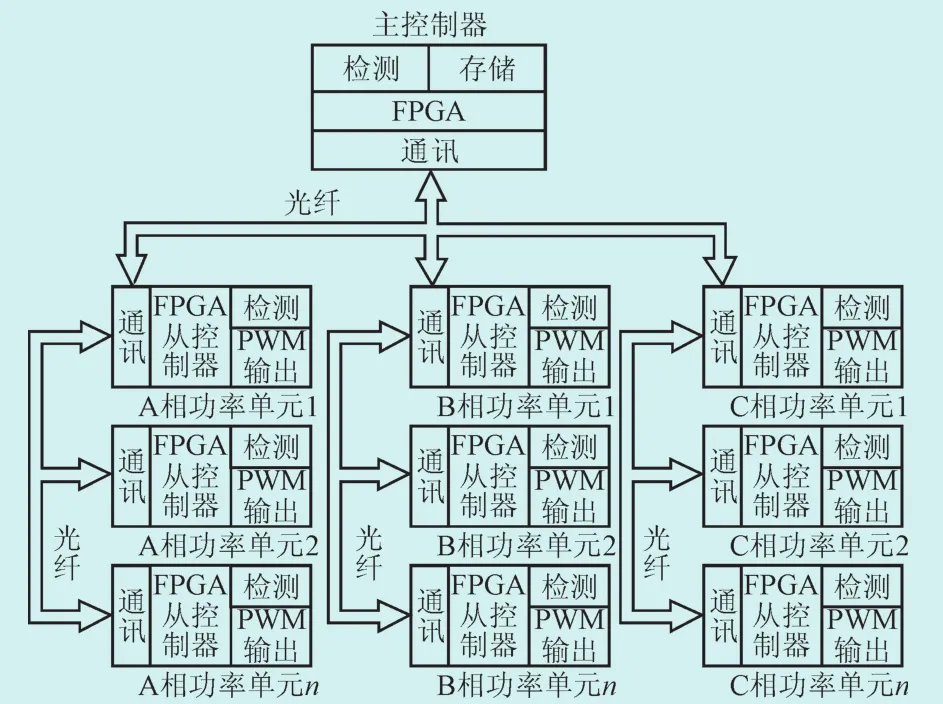

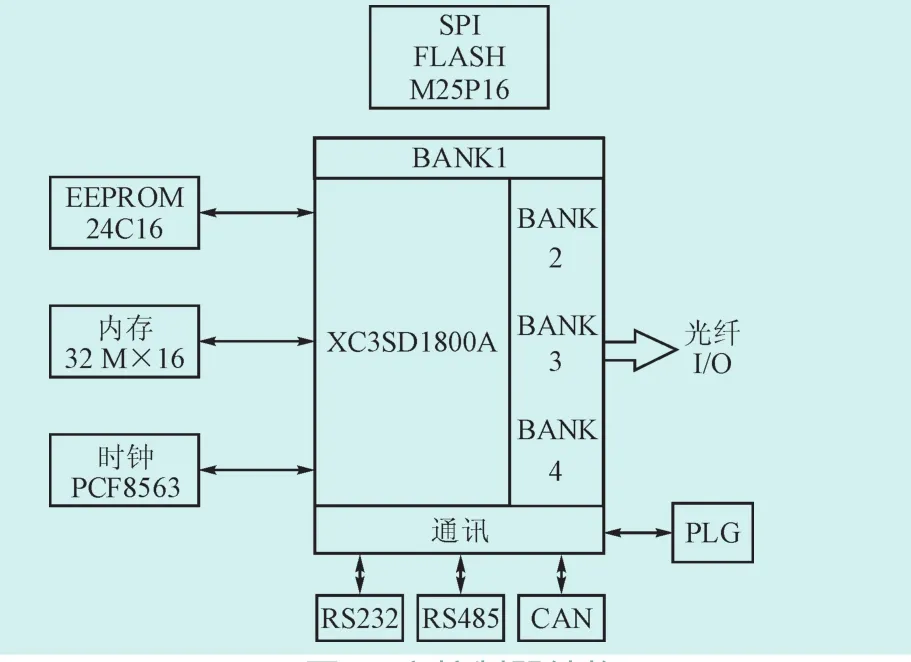

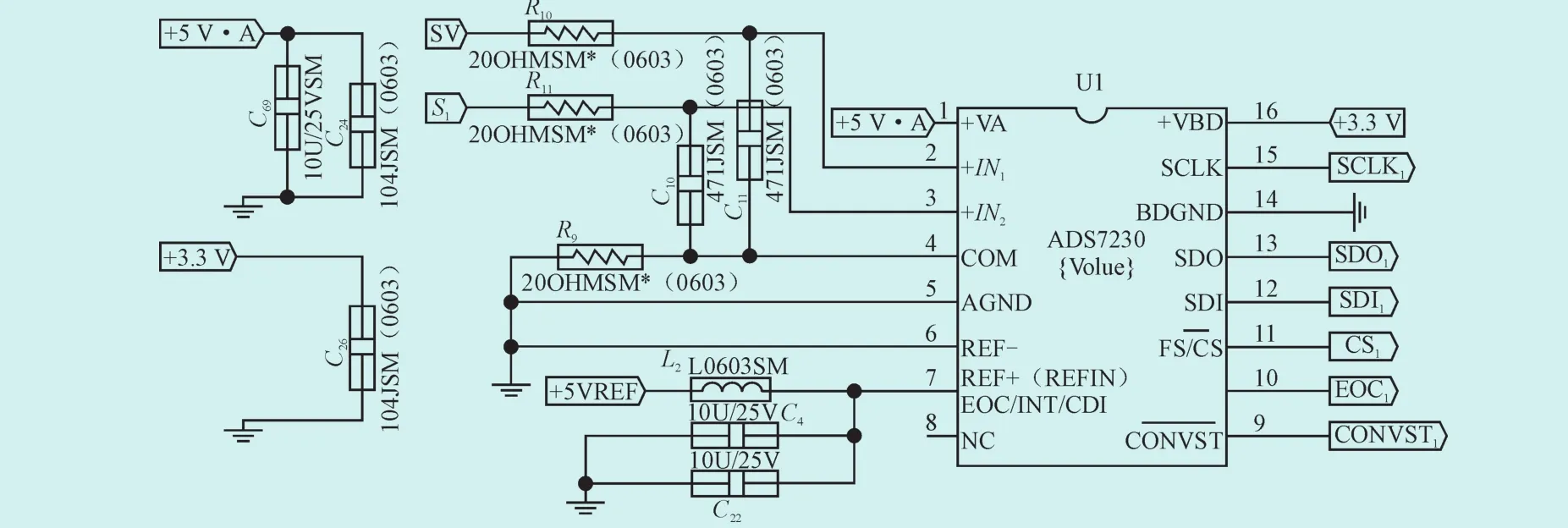

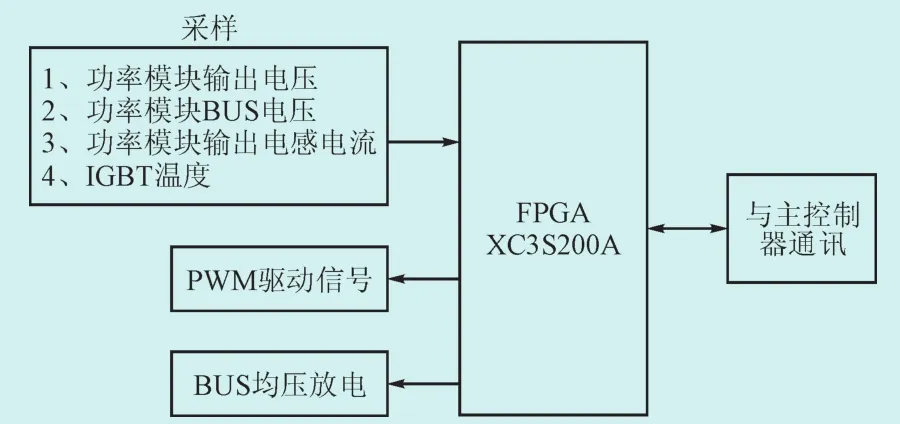

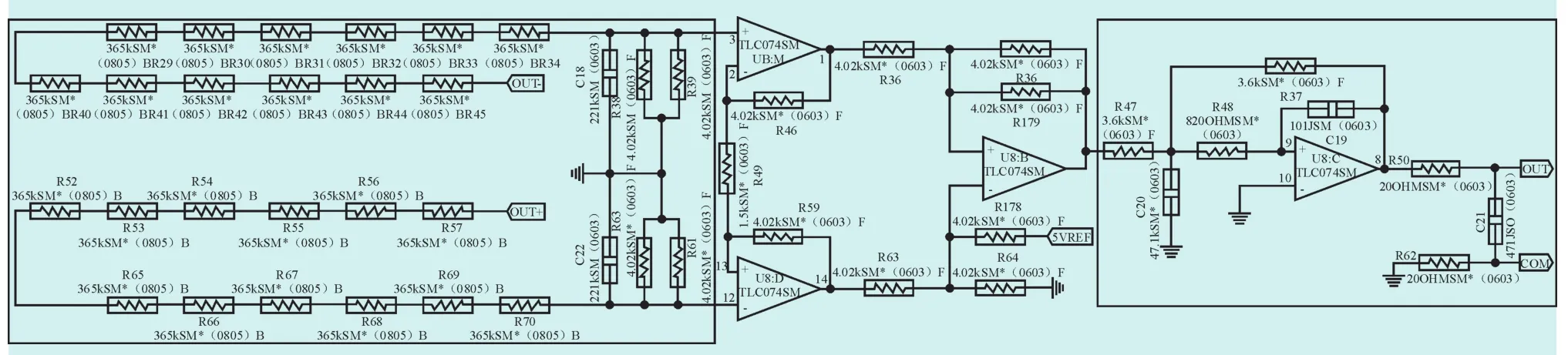

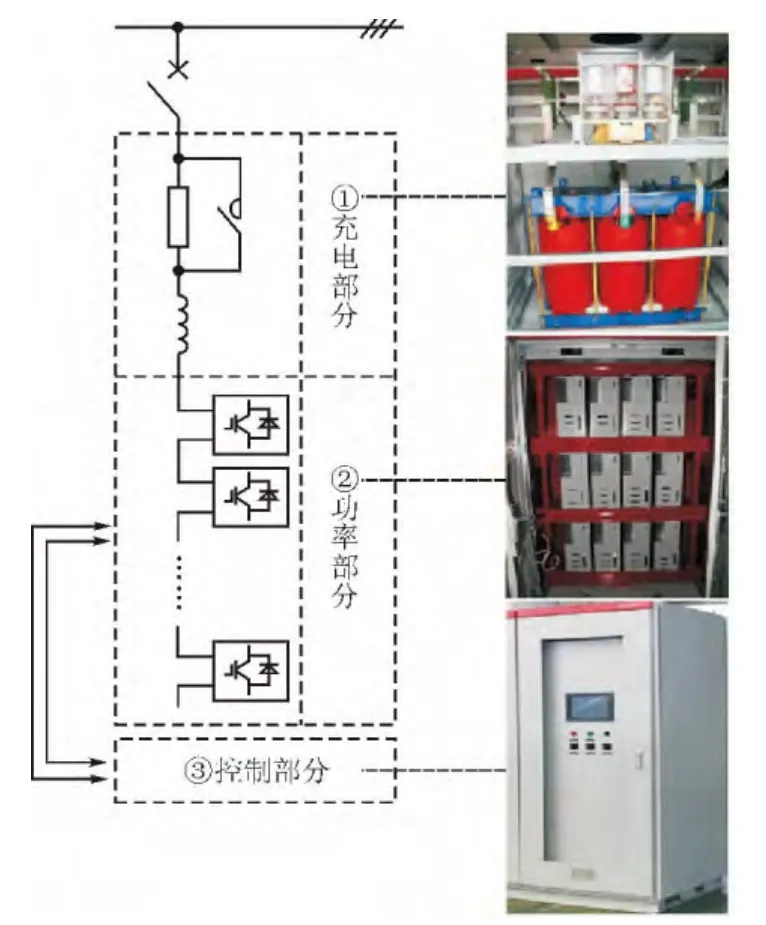

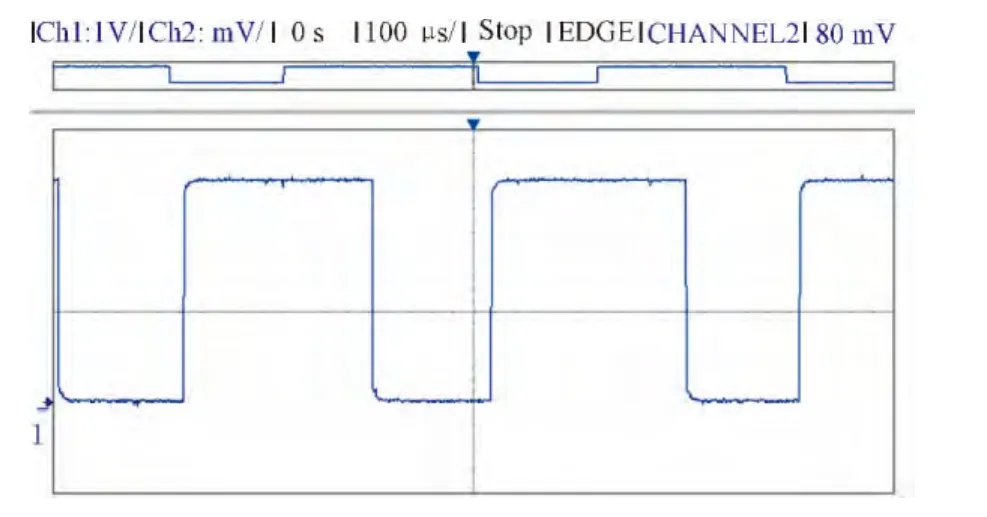

图1为STATCOM的结构示意图,其中信号调理板、FPGA控制板以及信号驱动板构成了STATCOM的控制电路;功率变换器、连接电抗、软起电阻、主接触器等构成STATCOM的主电路。Vc为功率变换器输出电压;Vs为系统电压。通过控制连接电感两端的电压关系,即可使流经电感的电流IL在容性电流和感性电流之间进行调整。IL与功率变换器的输出电压Vc及系统电压Vs的关系如图2所示,当Vc>Vs时为容性电流;当Vc 图1 STATCOM结构图Fig.1 The structure of STATCOM 根据链式STATCOM的工作原理,从提高装置的工作可靠性出发,采用主从控制器相结合的方式对控制电路进行设计。控制器采用xilinx具有数据处理功能的FPGA代替传统的DSP控制器,总的电路控制框图如图3所示。主控制器负责整个装置的数据存储、运行监控与通讯。从控制器位于每个级联的功率模块内部,其主要作用为产生PWM、处理采样数据、获取驱动状态、与主控制器通讯以及当失去与主控制器联系时独立控制功率模块等[7]。 图3 STATCOM控制结构图Fig.3 The control structure of STATCOM 2.1.1 FPGA主控制板设计 对FPGA控制板设计需要首先确定系统所需要的I/O个数。设计中各功率单元选用1700 V的IGBT模块,BUS电压最高可使用到1100 V,功率模块输出的最大电压为1100×0.9/1.414=700 V,对于6000 V母线电压的应用,采用三角形接法,并考虑一级冗余,最大需要级联的个数为:6600/700+1=11。若考虑一个控制器可以控制两路级联,则控制器需要控制11×3×2=66个功率模块,如果每个功率模块通过4条光纤链路和控制器通讯,需要控制器提供264个I/O口[8-9]。 控制器由主控制器和从控制器两部分组成,主控制器负责整个装置的数据存储、运行监控与通讯;从控制器位于每个级联的功率模块内部,其主要作用为产生PWM、处理采样数据、获取驱动状态、与主控制器通讯以及当失去与主控制器联系时独立控制功率模块等。 主FPGA控制板如图4所示,控制芯片采用XC3SD1800A,其内部集成有XtremeDSP,性能达到30 GM·C/s、存储器带宽高达2196 Mb/s。 图4 主控制器结构Fig.4 The master controller 由于其需提供多种数据存储能力、实时时钟、以及足够的I/O口。首先是RAM,使用32 MB×16 DDR2 SDRAM,运行时钟可达到100 MHz以上。需要频繁保存的配置数据要存储到24C16(EEPROM/IIC)上。其余需要保存的用户数据存储到M25P16(SPI FLASH)上。FPGA的配置数据和程序存储到专用的M25P16(SPI FLASH)上。采用DS1302(IIC)作为RTC,为系统提供实时时钟[10]。 BANK1用作RAM接口(独占),其余3个BANK除掉专用的引脚外,共287个I/O(INPUT/OUTPUT),88个IP(INPUT),用于光纤I/O。 2.1.2 信号调理板设计 信号调理板负责对采集的电网电压、电流以及流经串联电抗器上的补偿电流进行检测,从CT、PT采样出来的是电流信号,需要将电流信号变成电压信号,每个通道的输入电流暂定为±50 mA,之后送入ADC。采用TLC074作为信号调理运放,可以直接输出±50 mA电流。具体电路如图5所示。 首先经过一个电阻R85,将电流转换成电压;然后再经过差分放大电路,增益分放大效果,比例电阻推荐采用0.1%精密电阻,使运放同相、反相输入阻抗尽可能一致。在输入另加一个直流偏置2.5 V,VRV=I-RV×11+2.5 V。 图5 信号调理图Fig.5 The signal conditioning diagram of STATCOM 采样板采用ADS7230作为模数转换器,可以实现1 msample/s,12位无丢码采样,具有2个模拟输入通道。模拟输入信号幅值可达5 V,并采用差分输入模式,对噪声的抑制能力较强。每个采样板使用6片ADS7230,不使用模拟开关可实现12通道,每个通道500 ksample/s的采样速率。这12个通道可转换3相母线电压、3相母线电流、3相电感电流、3路备用。具体电路如图6所示。 在输入管脚处加上RC低通滤波器(截止频率约在170 kHz),用来滤除从源传来的噪声。输入为单极性电压,幅度范围0 V ~VREF。ADC与FPGA通讯采用SPI主从控制方式(FPGA为主设备,ADS7230为从设备),由一个主设备多个从设备组成,由图6中的SDI(数据输入)、SDO(数据输出)、SClK(时钟)、CS(片选)进行控制。由于SPI采用的是串行通讯协议,因此图中的管脚SCLK用于产生时钟脉冲,SDI与SDO在此脉冲的基础上完成数据传输。 图6 采样电路Fig.6 The sam pling circuit 2.1.3 光纤电路板设计 功率模块与控制器之间采用光通信方式,光纤通信有不怕外界强电磁场的干扰、信道间无串扰、损耗低、柔软可挠等优点[5]。特别是在高压系统中,弱电控制信号极易受干扰,影响系统的正常运行。每个光纤接口板可以和6个功率模块通讯,每个功率模块通过4条光纤链路和控制器通讯。采用异步串行通讯,只需使用1收1发2个通道,其余2个通道备用。 光纤收发器是一种将短距离的电信号和长距离的光信号进行互换的传输媒体转换单元。本模块采用Agilent的HFBRx528。其中,1528为发送器,2528为接收器。HFBRx528工作波长为650 nm(红色可见光),数据传输速率可达10 Mbit/s,推荐工作电流60 mA。 2.1.4 通讯电路设计 通讯板包括2个RS232接口,2个RS485接口,2个CAN接口,另外还有4个开关量输入,6个开关量输出。设置开关量输入和输出主要是为了响应某些需要快速反应的输入和输出,其余慢速的开关量输入及输出由PLC实现。开关量输入和输出使用6N137隔离。 RS232接口用于近距离通讯,可用于与上位机通讯,或外接GSM模块或无线模块进行远距离无线通信。RS232接口提供5 V/1 A电源,可用于给外接模块供电。RS232采用6N137作信号隔离,以提供高达921600B/S的波特率。RS232由FPGA实现。 RS485接口用于与PLC,或远程监控系统通讯;也使用6N137作信号隔离,SN75176作为收发器;RS485也由FPGA实现。 CAN接口主要用于与监控系统的通信或多台机器间的通信。使用6N137作信号隔离,82C250作为收发器,CAN控制器采用MCP2515。 所有通信接口之间相互隔离,为此设计隔离电源模块,以+12 V为输入,产生+5 V/1 A。模组使用UC3846D作为控制芯片。 从控制器的结构如图7所示,控制芯片采用xilinx XC3S200A FPGA,主要完成采样、通讯、PWM驱动信号输出、BUS均压放电等功能。 图7 从控制器结构Fig.7 The slave controller 2.2.1 模块输出电压采样电路设计 输出电压采样放大滤波电路如图8所示,由于模块输出电压正常情况下大于1000 V,不能直接送到AD中转换,因此首先通过电阻分压(如图8中红框所示),电阻由24个365 kΩ(0805/0.1%)和4个4.02 kΩ(0603/0.1%)的贴片电阻组成,0805的贴片电阻耐压值为150 V,最大功率为1/8 W。设计最大采样输入电压为1700 V,采样电阻经过分压后实际承受的最大电压约为70 V,功率约为15 μW,远小于额定值。所以采样电阻的选取是合适的。为保证差分放大效果,分压电阻及比例电阻必须采用0.1%精密电阻,使运放同相、反相输入阻抗尽可能一致。电阻分压送入由TLC074组成的仪用放大器进行差分放大,当R46=R59、R35=R63、R36//R179=R64//R178时,增益可简化为 图8 电压采样Fig.8 The sam pling circuit of voltage Vout=-(OUT×4.587×10-4×3.18+2.5) 2.2.2 BUS均压放电电路设计 在模块工作过程中,BUS电压可能超出正常范围,因此设计放电电路,使得BUS电压下降到正常范围。具体电路如图9所示。 图9 BUS均压电路Fig.9 The sharing voltage of BUS 正常工作时,IO_DIS为高电平,Q3截止,光耦导通,BUS+通过3个330 kΩ电阻到BUS-。MOSFET关断。当BUS过压时,IO_DIS为低电平,Q3导通,光耦截止,BUS+通过3个330 kΩ电阻给MOSFET的结电容充电直至导通,之后稳压管分流使其保持在15 V驱动电压。同时,BUS+连接一个放电电阻通过MOSFET放电,放电功率50 W。设BUS电压为1700 V,驱动电阻功率为3 W,选用额定功率2 W的电阻,留有足够裕量。放电电阻放电用的MOSFET选用IXBH-6N170,VCES=1700 V,IC=12 A(25 ℃),ICM=24 A(25 ℃,1 ms),满足要求。 为验证所设计控制器的性能,搭建了链式STATCOM的实验平台。各功率模块电容为320 μF/1200 V,连接电感为1.1 mH/6 kV/300 A。设计中STATCOM的电压环、电流环及平衡链均采用PI调节器进行控制。图10为实验平台结构图。 图11为从控制器的PWM驱动信号波形,从图中可以看出看出PWM波并没有振铃及反射,串扰的现象发生。 图12为功率模块的IGBT开通与关断波形,从图12可以看出开通过程调整迅速,关断时,反峰电压良好。 图13为整个实验装置在负载投入时刻的补偿效果图,从图13可以看出STATCOM从负载开始投入就立即进行补偿,不仅可以补偿无功还可以抑制谐波,最终电流波形趋于正弦且与电压同相,补偿效果良好。 图10 实验平台Fig.10 The experiment platform 图11 从控制器发出的PWM波形Fig.11 The PWM waveform from controller 图12 功率模块IGBT开通与关断波形Fig.12 The on/off waveform of power module IGBT 图13 STATCOM补偿实验Fig.13 The compensation experiment of STATCOM 采用具有数字信号处理功能的FPGA芯片进行系统设计,可以充分利用其并行运算处理功能,提高整个系统的响应速度。同时FPGA芯片不受外部电磁干扰影响且I/O口较多,可以满足STATCOM的设计需求。 [1] 蔡海青,张建设,韩伟强,等.南方电网东莞STATCOM过负荷与暂态逻辑控制仿真研究[J].南方电网技术,2013,7(4):75-77.CAI Haiqing,ZHANG Jianshe,HAN Weiqiang,et al.Simulation on the overload and transient logical controls of dongguan STATCOM in CSG[J].Southern Power System Technology,2013,7(4):75-77(in Chinese). [2] 高小刚,周羽生,王云飞.UHVDC换流站环形接地极埋深特性研究[J].电瓷避雷器,2012(2):72-76.GAO Xiaogang,ZHOU Yusheng,WANG Yunfei.Research on the burial depths characteristics of the annular grounding electrodes in UHVDC converter stations[J].Insulators and Surge Arresters,2012(2):72-76(in Chinese). [3] 张廷营.采用STATCOM抑制次同步谐振的理论与仿真研究[J].电网与清洁能源,2013,29(11):49-54.ZHANG Tingying.Theory and simulation research of STATCOM for damping subsynchronous resonance[J].Power System and Clean Energy,2013,29(11):49-54(in Chinese). [4] 方磊,王英健,张玉环.电力系统谐波检测加窗插值算法及其Matlab实现[J].电瓷避雷器,2009(3):39-42.FANG Lei,WANG Yingjian,ZHANG Yuhuan.Power system harmonics measurement window interpolation algorithm and the realization with matlab[J].Insulators and Surge Arresters,2009(3):39-42(in Chinese). [5] 陈晟.电能质量与供电可靠性关系分析[J].高压电器,2013,49(12):99-103.CHEN Sheng.Analysis of relationship between power quality and power supply reliability[J].High Voltage Apparatus,2013,49(12):99-103(in Chinese). [6] 尚勇,朱岸明,王敏,等.高压大容量SVC阀组冷却系统优化设计[J].高压电器,2013,49(3):79-84.SHANG Yong,ZHU Anming,WANG Min,et al.Optimal design of thyristor valve cooling-system for high-voltage and large capacity SVC[J].High Voltage Apparatus,2013,49(3):79-84(in Chinese). [7] 解蕾,金琪,刘晨怡,等.含有动态无功补偿器的供电系统自动电压控制设计[J].电力与能源,2014,35(1):35-42.XIE Lei,JIN Qi,LIU Chenyi,et al.Automatic voltage control design of power supply system with dynamic reactive power compensator SVC[J].Power&Energy,2014,35(1):35-42(in Chinese). [8] 刘俊杰,赵钢,李彪.基于新型电流直接控制策略的SVG仿真研究[J].电网与清洁能源,2013,27(6):21-24.LIU Junjie,ZHAO Gang,LI Biao.Simulation and study of SVG based on new direct current control strategy[J].Power System and Clean Energy,2013,27(6):21-24(in Chinese). [9] 许胜辉.逆变器输出滤波器的设计[J].高压电器,2011,47(12):44-48.XU Shenghui.Design of inverter output filters[J].High Voltage Apparatus,2011,47(12):44-48(in Chinese). [10] 刘娇,刘斯佳,秦斌,等.逆变站无功控制及无功补偿设备的投切策略[J].电力与能源,2012,33(6):535-539.LIU Jiao,LIU Sijia,QIN Bin,et al.Reactive power control and the strategy of reactive power compensation equipment for switching on the inverter station[J].Power&Energy,2012,33(6):535-539(in Chinese).

2 控制电路设计

2.1 主控制器设计

2.2 从控制器设计

3 实验

4 结语