某飞行器双绞线数据传输系统的设计与实现

瞿林,陈海亮,甄国涌,刘东海

(1.中北大学电子测试技术国家重点实验室,山西太原030051;2.北京航天长征飞行器研究所,北京100076;3.太原市华纳方盛科技有限公司,山西太原030051)

高速长距离数据传输对总线要求比较高,常用的高速总线主要有HOTLink和低压摆幅差分信号LVDS(Low Voltage Differential Signaling),其中LVDS可以在差分PCB线对或平衡电缆上以几百兆至几千兆比特每秒的速率传输数字信号,在实际应用中较多[1]。

常用的LVDS传输介质有双绞线和同轴电缆。比较而言,双绞线具有抗干扰能力强、重量轻、易弯曲、易安装、成本低等优点,同时还特别适用于互补信号的传输,其制造不需要特别的设备,装配、焊接方便,窜扰小,这些为它的广泛应用提供了有利条件[2]。

某型号飞行器的研制中,要求设备间通信速度达到

176.947 2 Mb/s波特率,电缆由多对低频连接器连接,总长度达104 m。但双绞线是有损耗传输线,百米以上信号传输衰减比较严重,且低频连接器阻抗不可调控,与电缆之间阻抗不连续,其耦合电容、漏电流、辐射等因素导致容易产生干扰信号。这些都成为了信号传输过程中的隐患。本文选用戈尔高性能屏蔽双绞线作为传输介质,设计数据传输方案,并进行了关键性分析。

1 总体方案

1.1 数据传输模型

图1 数据传输模型

数据传输模型如图1所示,双绞线的特性阻抗为100±10 OHMS,最大延迟是1.24 nSEC/FT,衰减特性为在100 MHz下衰减8 dB/100 FT。为了有效模拟设备电缆网,实现百米数据传输,实验时双绞线电缆由6段15 m、1段11 m和1段3 m的双绞线组成,总长度设计为104 m(约341.2 FT),中间有9对J14H系列连接器相连接。信号通过传输链路,最终由上位机进行数据分解。

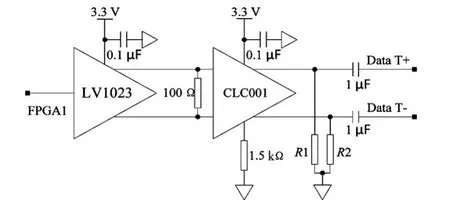

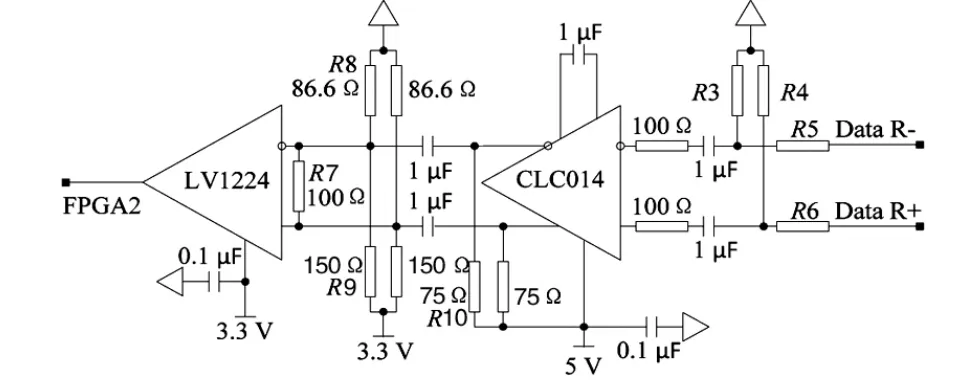

1.2 系统硬件设计

数据发送电路如图2所示,接收电路如图3所示,采用美国国家半导体推出的10位总线型LVDS应用芯片组SN65LV1023和SN65LV1224作为发送和接收芯片。该器件组进行数据串化时采用内嵌时钟,可以有效避免因时钟不严格同步而造成的数据传输错误问题。为了达到数据传输104 m的要求,在发送端加一片高速电缆驱动芯片CLC001,接收端加一片自适应电缆均衡芯片CLC014。CLC001可以增强双绞线电缆的驱动能力,CLC014可以自适应地对不同长度电缆进行均衡,均衡长度从0 m到相当于信号在200 MHz时衰减40 dB的长度,即300 m的Belden型同轴电缆或120 m的第五类未屏蔽双绞线。

图2 数据发送

图3 数据接收

2 阻抗匹配分析

信号反射的主要原因是线路中间阻抗不匹配。本设计中双绞线特性阻抗为100 Ω,所以R1、R2的阻值选取50 Ω,而R3、R4、R5、R6的选取除了要遵循阻抗匹配的原则外,还应该考虑到输出信号的电平,使得电缆可以发挥最好的均衡效果,设计中选取25 Ω。

J14H系列连接器阻抗不可调控,导致传输线路阻抗不连续。而阻抗不连续机构的耦合电容、漏电流、辐射等因素导致容易产生干扰信号。所以传输系统可靠实现的关键是要确定干扰的影响能力并最大程度恢复数据波形。

3 双绞线衰减分析

设备间通信速度快,工作频率在趋肤效应区,衰减与频率的平方根和长度之积成正比[3]。因此本文从频率和长度两方面进行测试与分析,在确保信号传输性能良好的情况下,最大限度提高系统传输距离。以下列出了其中3组标准码型测试结果和1组非标准码型测试结果。

3.1 标准码型信号传输

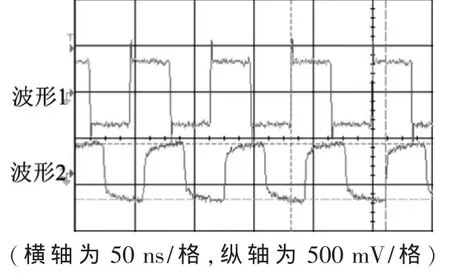

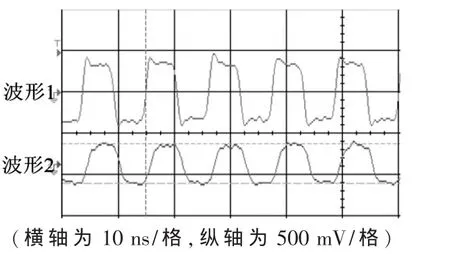

标准码型数据中高低电平持续时间相等,如图4~图6所示,电缆发送端信号摆幅均使用700 mV。图4中双绞线长度为18 m,中间有3对连接器,信号传输频率为14.745 6 MHz,双绞线末端接收到的信号摆幅为600.6 mV,通过衰减公式中双绞线为18 m,中间有3对连接器,信号传输频率为88.473 6 MHz,双绞线末端接收到的信号摆幅为481.25 mV,计算得衰减约为3.25 dB;图6中双绞线为104 m,中间有9对连接器,信号传输频率为14.745 6 MHz,双绞线末端接收到的信号摆幅为289 mV,计算得衰减约为7.68 dB。图4和图5说明了在传输距离一定时,信号衰减与信号频率的平方根成正比;图4和图6说明了在信号频率一定时,信号衰减与传输距离成正比。

图4 电缆发送端(波形1)和接收端(波形2)波形

图5 电缆发送端(波形1)和接收端(波形2)波形

图6 电缆发送端(波形1)和接收端(波形2)波形

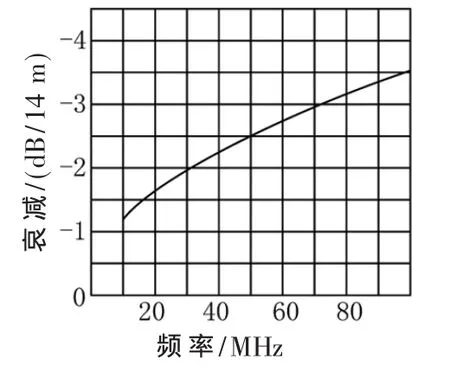

结合其他频率和距离下的测试结果,绘制出频率衰减特性曲线如图7所示。测试表明,高频信号衰减与信号频率的平方根和传输距离之积依然成正比关系。

很明显,J14H系列低频连接器并未对传输信号衰减造成明显的影响,但是信号存在反射,当然这个反射不一定是由连接器产生的,也有可能是示波器本身或者其他因素造成的。为了获得更理想的传输效果,应该尽量选用能够支持高达千兆位以上数据传输率并且阻抗可以调控的连接器[4]。

图7 频率衰减特性

3.2 非标准码型信号传输

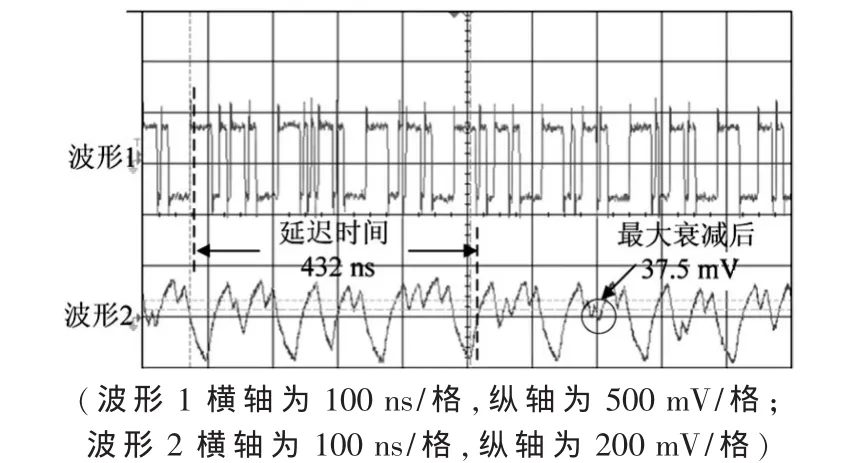

如果LVDS信号不经过编码处理,则其传输时都是非标准码型的,高低电平持续时间随机。所以当接口频率为14.745 6 MHz时,最小的数据脉冲有效频率应该是14.745 6×6=88.473 6 MHz。由于衰减与频率的平方根和距离之积成正比,可算得电缆最大7.5 dB/100 FT,所以341.2 FT电缆最大衰减即为25.5 dB。实验中电缆发送端信号UI为700 mV,根据衰减公式端实测波形如图8所示。从图中可以看出,发送端信号约为700 mV,接收端信号最大衰减后约为37.5 mV,与理论值37 mV基本吻合。电缆的延迟时间理论值为1.24×341.2=423.088 ns,与实测432 ns相差也不大,考虑到电路板上存在着传输延迟以及其他因素,以上误差在合理的范围内。

图8 电缆发送端(波形1)和接收端(波形2)波形

4 均衡器的实现

由图8可知,电缆接收端信号码型比较差,最小数据脉冲甚至越不过零点门限。虽然交流耦合网络可以去除数字信号中由前级产生的直流偏置分量,使得波形的高低电平偏移相等,但是非标准码型信号不均等的衰减使得部分数据脉冲无法越过零点门限。若单独使用SN65LV1224,则会造成接收端解码出现错误。

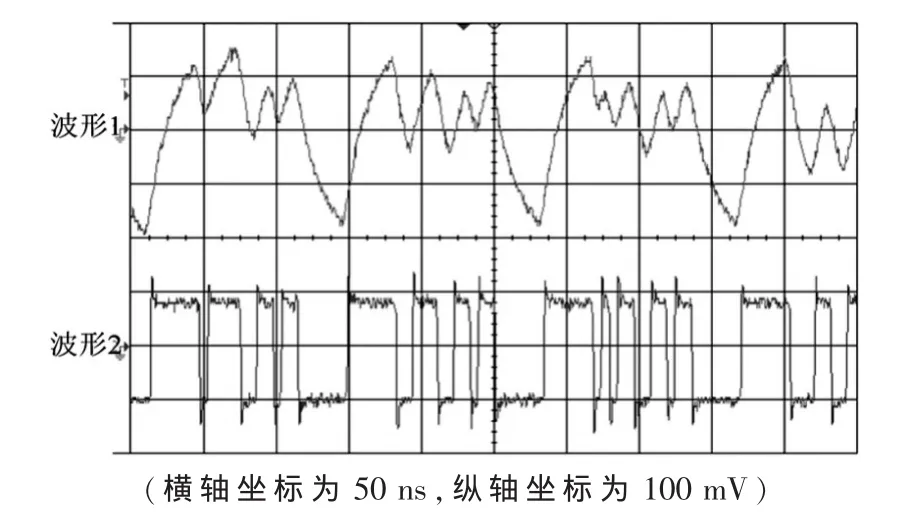

因此必须对接收到的LVDS信号进行模拟均衡,本设计采用电缆均衡器芯片CLC014。经过测试,对于最大有效频率为88.473 6 MHz时衰减25.5 dB的信号,通过均衡器后波形恢复比较理想。如图9所示,波形1为电缆接收端信号波形,波形2为CLC014输出信号波形。可以看出,均衡器输出摆幅为200 mV。CLC014是电流型输出,输出电流大约10 mA,所以均衡器输出信号幅值大小与均衡器端接负载有关[5]。由于CLC014与SN65-LV1224之间为交流耦合,所以交流阻抗可以等效看成是多个负载电阻的并联,即R10//(R8//R9)//(R7/2)=75//55//50=19.4 Ω,则输出端电压值为19.4×10=194 mV,与实测的200 mV基本吻合,符合SN65LV1224的门限电压。因此均衡后的LVDS信号可以通过解串器正确解码。

图9 电缆接收端(上)和CLC014输出(下)波形

5 测试

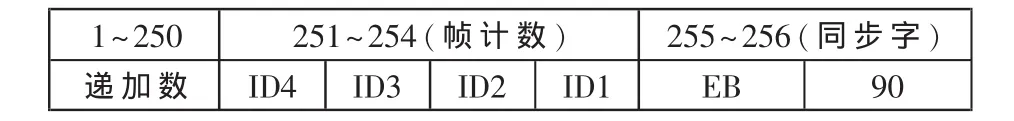

对系统进行高温60℃和低温-40℃环境下的传输测试,数据帧格式如图10所示。1~250字节为递加数,251~254字节为帧计数,255~256字节为同步字。将设备及电缆放入恒温箱内,保温2 h后启动设备通电工作,传输满4 GB数据时断电,并通过上位机测试软件对记录的4 GB数据进行分解,得出数据分析报告。经过多次高低温循环测试,结果表明,数据传输104 m时误码率小于10-9。

图10 数据帧格式

本数据传输系统的设计中使用了多对低频连接器,虽然存在信号的反射,但这并不影响LVDS信号的传输。对于工作在趋肤效应区的高频信号,其衰减与频率的平方根和传输距离之积依然成正比关系。电缆均衡器CLC014可以对高速长距离传输的LVDS非标准码型信号进行自适应补偿,改善信号因传输线路不均等引起衰减而越不过零点门限的情况。该系统已经通过温度循环试验、高低温试验等,传输可靠,性能稳定,能够满足某型号飞行器数据传输的需求,现已投入正式使用。

[1]杨雷,龙哲仁,卢继华,等.LVDS高速并口通信协议设计[J].电子技术应用,2013,39(3):119-122.

[2]管京周,李世平,陈世伟,等.双绞线的基本概念及应用技巧[J].工业控制计算机,2005,18(4):74-75.

[3]霍华德·约翰逊.高速数字设计[M].北京:电子工业出版社,2010.

[4]GLISIC D.数百Mbps@数百米:扩展LVDS的传输距离[J].电子产品世界,2004(21):123-124.

[5]李建荣,张颖光.自适应电缆均衡器CLC014的原理与应用设计[J].电子技术应用,1999,25(3):57-59.