PCB设计中的串扰分析

上海交通大学电子工程系 王 佶

1.引言

串扰在电子学上是指两条信号线之间的耦合现象。电容性耦合会引发耦合电流,而电感性耦合则引发耦合电压。根据麦克斯韦定律,只要有电流的存在,就会有磁场存在,磁场之间的干扰就是串扰的来源。

2.串扰的危害

接下来,我们以一块板卡中出现的数据丢包问题,来说明串扰对信号品质的影响,以及对整个电路系统的危害。笔者遇到过一块板卡,在常温下数据传输是正常的,高低温的时候,出现了数据丢包的现象,查看发生数据丢包的差分信号线的眼图,发现丢包数据线的眼图很差,如图1所示:

图1 发生丢包的数据线对应的眼图

为了查找数据丢包的原因,用Sigrity PowerSI软件对丢包的数据线Lane3,提取了其插损、回损、串扰、ICR(Insertion to crosstalk ratio),参照IEEE802.3ap标准,将提取出来的参数和IEEE802.3ap标准中规定的最低限进行比对,以期能找到数据丢包的原因。

2.1 IEEE802.3ap标准

IEEE802.3ap标准中,关于ICR的计算如下:

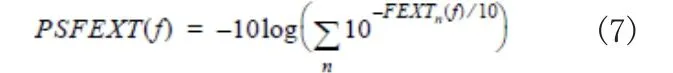

IEEE802.3ap标准中,关于crosstalk的计算见式7,其中PSFEXT是NEXT和FEXT的功率之和。

2.2 仿真准备

此板卡的PCB为20层,所用PCB材料为MEGTRON4,介电常数3.9。

2.3 仿真过程和结果

我们找到离Lane3最近的同层信号线、相邻层信号线、换层过孔,作为干扰源,一共找了10条信号线,这10条信号线加上Lane3本身的两条信号线,总共有12条信号线,将其设为24个port。在Sigrity中提取这些干扰源对Lane3中的差分信号线中N/P各自的串扰,导出S24P参数,将其导入到ADS中,然后利用ADS中的合并功能,合并出这些干扰源各自对Lan3中差分对的串扰(不是对N/P单独的干扰,而是对N/P组成的差分对的串扰)。

再结合IEEE802.3ap标准中的公式,在excel中设计公式,计算出Lane3的插损、串扰、ICR,并与IEEE802.3ap中对插损、串扰、ICR规定的最低限进行比对,比对结果见图2、3、4:

图2 S12(红色为IEEE802.3ap标准中规定的最低限;蓝色为实际的S12)

图3 Crosstalk

图4 ICR(Insertion to crosstalk ratio)

从图2、3、4中可以看出,发生数据丢包的Lane3,其S参数,是能满足IEEE802.3中的相关标准的,说明信号线本身的品质是不错的,但是其串扰和ICR比较差,说明其同层和相邻层的信号线,对它的串扰比较大,从而导致的眼图张不开,进而出现数据丢包的现象。

2.4 解决办法

减小串扰的方法有以下几种:(1)增加信号路径之间的间距;(2)用平面作为返回路径;(3)使耦合长度尽量短;(4)在带状线层布线;(5)减小信号路径的特性阻抗;(6)使用介电常数较低的叠层;(7)在封装和接插件中不要共用返回引脚;(8)使用两端和整条线上有短路过孔的防护布线。

针对这块板卡的实际情况,采取了以下的措施:(1)加大Lane3与同层信号线、过孔、shape的距离,让距离大于其4倍的线宽。(2)Lane3位于第13层,跟第14层的信号线有重合的情况,为了减小其相邻层的耦合,在L13和L14之间加一个GND层,为了保持总层数为偶数,在L10和L11之间也加一个GND层,以保持其对称性。

对改善之后的Lane3进行仿真,其ICR和Crosstalk得到显著改善,完成PCB打板和贴片后,对PCB进行实际量测,其眼图明显改善,且高低温的时候也不丢包,可见,此次丢包正是由于串扰而引起的。

图5 做了抗串扰处理后的Lane3眼图

3.结束语

本文先阐述了串扰的概念,和PCB中串扰产生的机理。其次,结合工程实践中,一块板卡中出现的数据丢包现象,说明串扰对信号品质的危害和对整个电路功能高品质实现的危害。最后,结合既往设计经验,同时参照IEEE802.3ap标准,提出了减小串扰的方法,并据此方法进行改版,对改版后的PCB测量其眼图,并做高低温测试,发现眼图效果良好,且数据能正常传输,未发生丢包,故而证明文中提出的方法是可行的。

[1]吴昊,陈少昌,王杰玉.高速数字系统的串扰问题分析[J].现代电子技术,2009(01):170-173.

[2]曾爱凤,王海鹏.板级互连线的串扰规律研究与仿真[J].电子测量技术,2010,33(8):9-10.

[3]李朝辉.基于RLC模型的集成电路互连线串扰估计[J].电子测量技术,2008,31(5):49-51.

[4]李世文,王贵.多导体传输线间的串扰分析与仿真[J].声学与电子工程,2009(02):31-33.

[5]王强,沙斐.平行双线串扰的分析[J].电子测量与仪器学报,2009,22(6):75-77.